# 高速リカバリタイプSJ-MOSFETプロセスの確立

## Establishment of Fast Recovery Type SJ-MOSFET Process

大 森 寛 将 Tomoyuki Omori

崔 正 鉉\*\* JungHyun Choi

概要 近年,電子機器は小型化,大電流化,高速化の要求を受け,搭載されるデバイスはさらなる高性能化を求められている。その中で高耐圧素子であるスーパージャンクション MOSFET (以下, SJ-MOSFET) は,民生,産業,自動車など多岐分野にわたり採用されている。SJ-MOSFET は耐圧とオン抵抗のトレードオフを改善し,オン抵抗を大幅に低減できる。しかし,インバータ回路のように寄生ダイオードを積極的に使用する場合は,その特徴的な構造からリカバリ特性が悪くスイッチング損失を悪化させる。そこで当社は独自のプロセス技術により,リカバリ特性を改善したSJ-MOSFETプロセスを確立した。

#### 1. まえがき

近年,経済発展と人口増加に伴い,世界の消費エネルギーは増加の一途を辿っている。太陽光発電などの再生可能エネルギーの創出と,そのエネルギーを利用する電力変換機器の省エネルギー化が求められている。特にインバータなどの電力変換機器はパワー半導体デバイス,回路,制御システムによって構成されており,回路や制御方式でエネルギー損失の低減を図る一方でパワー半導体デバイスにおいても自身で発生するエネルギー損失の低減が必要となっている。

現在、高速・電力変換デバイスとしてパワーMOSFET が多岐分野にわたり採用されている。このパワーMOSFET も低損失化に向けて継続的に改善が行われており、高耐圧領域ではスーパージャンクション MOSFET (以下 SJ-MOSFET) が主流となっている。詳細な構造については第3節で述べるが、SJ-MOSFETは従来のプレーナー MOSFETよりもオン損失を大幅に低減できる。しかし、インバータ回路のように MOSFET内部に形成されている寄生ダイオードを積極的に使用する場合は、その特徴的な構造からダイオードのリカバリ特性が損失に大きく影響してしまう。

そこで本稿では独自のプロセス技術により、リカバリ特性を改善し、インバータ回路に最適なSJ-MOSFETのプロセスを確立したので報告する。

#### 2. 市場背景

パワー半導体デバイスは、自動車や太陽光発電といった新エネルギー用途、さらには冷蔵庫やエアコンといった民生機器まで、様々なアプリケーションで用いられており、1kV以下の高速・電力変換デバイスとしてパワーMOSFETが幅広く採用されている。

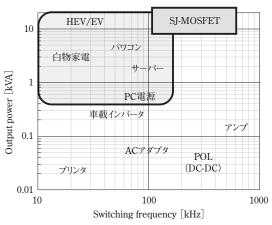

図1に、パワーMOSFETの動作周波数と出力電力による用途マップを示す。現在、高電力領域では、プレーナーMOSFETからSJ-MOSFETへの置き換えが進んでいる。用途別にはPCやフラットパネルディスプレイの1次側電源、サーバーや基地局のPFC回路、太陽光発電用パワーコンディショナ(パワコン)、HEV/EVのオンボードチャージャーなどで使用されている。また、最近ではSJ-MOSFETを搭載したIPMも製品化されており、今後も多くのアプリケーションで需要が見込まれている。

図1 パワー MOSFETの用途マップ

<sup>\*</sup>生産技術(統)素子量産技術部 素子調達課

<sup>\*\*</sup> Advanced Power-device Technologies Co., Ltd Product Team

#### 3. SJ-MOSFETの特徴

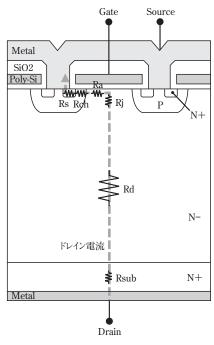

一般的な高耐圧パワーMOSFETは、図2に示すようなプレーナー構造となっている。パワーMOSFETの耐圧は、P型ボディ領域とN型ドリフト層で形成されたPN接合部において、低不純物濃度のN型ドリフト層に空乏層が拡がるとともにP型ボディ領域底部の電界ピークがSiの臨界電界強度に達したときに起こるアバランシェ降伏によって決定される。高耐圧化を図るにはN型ドリフト層の厚みを大きくすると共に不純物濃度を下げることで空乏層の厚みを確保する必要がある。

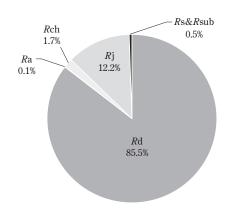

一方でパワーMOSFETのオン抵抗は、ソース抵抗(Rs)、チャネル抵抗(Rch)、蓄積層抵抗(Ra)、JFET抵抗(Rj)、ドリフト層抵抗(Rd)、基板抵抗(Rsub)の合成抵抗となる。これらの抵抗値のうち、高耐圧パワーMOSFETではドリフト層抵抗(Rd)が大部分を占めている。例として図3に600V耐圧MOSFETの抵抗成分割合を示すが全体の8割以上がドリフト層抵抗(Rd)で占めているのが分かる。

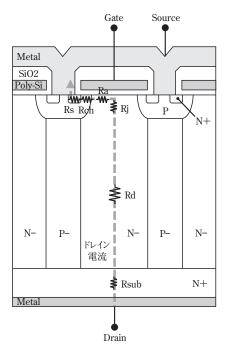

このように耐圧とオン抵抗はトレードオフの関係にあり、これまでN型ドリフト層の最適設計にてオン抵抗の改善が進められてきたが、ほぼ理論限界に達し、プレーナー構造ではこれ以上のオン抵抗低減は見込めなくなっていた。そこで理論限界をブレークスルーするため開発されたのがスーパージャンクション構造である。図4にそのスーパージャンクション構造を示すが、N型ドリフト層内にP型コラム層を周期的に交互に形成した構造で

図3 高耐圧プレーナー MOSFET の抵抗成分割合

ある。従来のプレーナーMOSFETは、バイアスが印加されるとP型ボディ領域からドレイン方向に向かってN型ドリフト層に空乏層が伸びるが、SJ-MOSFETはバイアスが印加されると縦方向でなく、各P型コラム層とN型ドリフト層の接合部より横方向に空乏層が伸び、左右に伸びた空乏層同士が繋がり完全空乏化となる。電流経路となるN型ドリフト層の不純物濃度を上げても空乏化しやすいため、耐圧を保持しつつ、低オン抵抗化が可能となる。SJ-MOSFETは、1997年に発表されて以来、各社活発に開発が行われている。プロセス技術の進歩による微細化と生産性向上により、オン抵抗の低減とコストダウンが進んでいる。

図2 プレーナー MOSFET

図4 スーパージャンクション MOSFET

#### 4. 開発成果

当社では損失低減のため、SJ-MOSFETを搭載した高 圧モータドライバICの開発を行っている。当社モータ ドライバICでは、使用される電流によって駆動素子を IGBTまたはMOSFETで使い分けている。モータードラ イブで使用されるインバータ回路では、回生電流や還流 電流を流すために、IGBTではダイオードを並列に接続 し、MOSFETではP型ボディ領域とN型ドリフト層で形 成された寄生ダイオードを使用する。このダイオードの リカバリ特性は、ターンオン損失と発生ノイズに大きく 影響するため、高速かつ低ピーク電流、低ノイズが求め られる (1)。

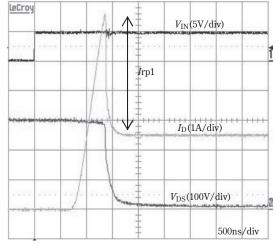

図5(a)に、インバータ回路にてSJ-MOSFETのスイッチング評価を行った時のターンオン波形を示すが、オン時に大きなリカバリ電流Irp1が重畳しているのが分かる。この大きなリカバリ電流の発生は、SJ-MOSFET特有の構造が原因である。ダイオードのリカバリ電流は、導通状態の順方向電流およびdi/dtに依存するが、ドリフト層内に蓄積されたキャリア量が多いほど大きくなる。つまり、P型アノード領域からの正孔注入が多いほど大きくなる。SJ-MOSFETは、第3節にて特徴を述べたとおり、耐圧を保持するためドリフト層内にP型コラム層を配置する。このP型コラム層はP型ボディ領域と繋がっており、いわばP型アノード領域を増加させることになるため、正孔注入も増加し、リカバリ電流増加の原因となってしまう。

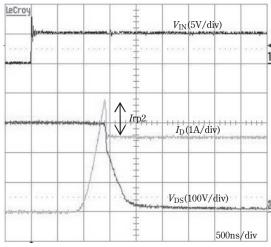

そこで今回、SJ-MOSFETのリカバリ特性改善のため、P型コラム層形成及びライフタイム制御条件等の最適化による独自のプロセス技術を確立した。図5(b)に今回プロセスの最適化を行ったSJ-MOSFETを同回路にてスイッチング評価した時のターンオン波形を示す。波形からも分かるようにリカバリ電流Irp2は、(a)プロセス最適化前のIrp1と比較し半分以下となっており、リカバリ電流の大きな抑制効果がみられた。また、ノイズの原因となるリンギング等も起きておらず良好な波形となっている。

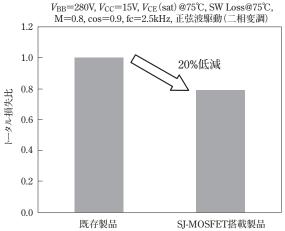

図6には今回最適化を行ったSJ-MOSFETを搭載した製品と当社にて量産しているプレーナーMOSFETを搭載した既存製品との損失比較を示す。このSJ-MOSFETは既存チップに対してチップ面積を約50%低減しているが、チップサイズを大幅に縮小したうえでも、約20%のトータル損失低減を実現しており、製品パッケージの小型化にも大いに期待できる結果を得ることができた。

測定条件:  $V_{BB}$ =300V,  $I_{D}$ =5A

(a) プロセス最適化前

(b) プロセス最適化後

図5 インバータ回路 ターンオン波形

損失比較

図6 既存製品との損失比較

## **5.** むすび

今回, インバータ回路に最適な高速リカバリタイプ (1) 南野: サンケン技報, vol.50, p.39-42, (2018.11) SJ-MOSFETプロセスを確立することができた。順次製 品開発へ展開し、当社製品のラインナップ拡充を図る。 また、今後も産機機器や民生機器、自動車市場などから のニーズに応えるべく、各アプリケーションに適応した 次世代SJ-MOSFETプロセスの構築を進めていく。

### 参考文献