# 40V/100V VFP-MOSFET の開発

# Development of 40V/100V VFP-MOSFET

近藤太郎\*

Taro Kondo

日 中文 悟\* Bungo Tanaka

概要 近年、パワー電子機器には高効率が求められている。このニーズを満たすため、機器の高速スイッチングによる高効率化が進んでいる。しかし、高速スイッチングは、主回路の電圧および電流のサージを増大させ、EMI (電磁干渉) の主要因となる。今や機器から発生するノイズは無視できなくなっており、EMI 対策は非常に重要となっている。サンケン電気ではノイズの主要因となるMOSFETの低ノイズ化に着目し、サンケン電気が独自開発した技術を用いて、EMI の原因となるスパイク電圧やリンギングノイズの低減を実現した。本稿ではEMI の抑制に優れた効果を発揮するVFP (Vertical Field Plate)-MOSFETの開発状況について述べる。

# 1. まえがき

パワー半導体デバイスとは、電力の制御や変換、供給をおこなうための半導体素子である。自動車や鉄道といった産業機器用途から、エアコンや冷蔵庫などの民生機器用途、さらには再生可能エネルギー用途まで幅広く用いられている。近年、省エネルギー対策の重要性が増しており、パワー半導体デバイスへの注目度が上がっているため、今後、市場規模が拡大することが予測されている。

パワーMOSFET (金属酸化膜半導体型電界効果トランジスタ) は、大電力を扱うパワー半導体分野において中心的な存在であり、その性能は、機器のエネルギー効率や消費電力などに直接影響するため、省エネおよび二酸化炭素の削減など環境に配慮するうえでも重要なデバイスである。

パワー MOSFETでもっとも重要視される特性はオン 状態の導通抵抗(以下,オン抵抗と呼ぶ)である。オン抵 抗は,同一プロセスのパワー MOSFETで比較した場合, チップサイズが大きいほど低くなる。しかし,チップサ イズが大きいほど,チップコストが上昇し,製品も大型 化してしまう。また,製品のスイッチング損失低減のた めにはパワー MOSFETのスイッチング速度の高速化が 重要となる。高速スイッチングのためには、ゲートチャージの低減が重要となるが、オン抵抗が低いほどゲートチャージは大きくなり、このトレードオフの改善が低導通損失と高速スイッチングを実現するパワーMOSFET開発の重要なポイントとなる。

低導通損失と高速スイッチングの両方を満たすために、VFP構造は特に低電圧アプリケーションにおいて有望なデバイス構造と見なされている。本稿では、当社のVFP-MOSFETの特徴、開発状況について述べる。

### 2. 市場背景

パワー半導体デバイスは自動車、鉄道、産業機器、情報通信機器、民生機器、新エネルギー(太陽光発電、風力発電など)、電力送電システムなど幅広い分野で使われている。産業用途ではファクトリ・オートメーション機器および工作機械やロボットなどのモーター駆動用の汎用インバータ、サーボモータなどにパワー半導体デバイスは欠かせない。また、自動車用でもハイブリッド電気自動車(HEV)や電気自動車(EV)のパワーウインドーやパワーステアリングなどにもパワー半導体デバイスが利用されている。このように、低損失、高効率のパワー半導体デバイスへの需要は着実に拡大している。

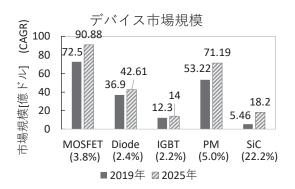

世界パワー半導体デバイス市場規模の推移を図1に示す。MOSFETの市場規模は2019年に72.5億ドル,2025年には90.8億ドルまで成長が予想される。また、需要分野では、自動車、産業機器が成長分野である。

\*半導体事業本部 マーケティング本部 プロセス技術統括部 デバイス開発部 デバイス設計 2 課

図 1 世界パワー半導体デバイス市場規模の推移 出典: 『2020\_ 進展するパワー半導体の最新動向と将来展望』 (矢野経済研究所)をもとにサンケン電気株式会社作成

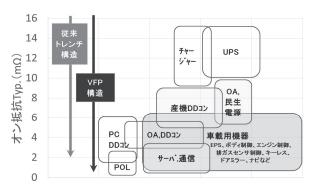

自動車や産業機器市場でMOSFETが多数使用されている低電圧MOSFETの市場マップを図2に示す。産業機器向けや自動車向けのアプリケーションでは機器の大電流化や小型化、省電力化に対応するため、MOSFETに非常に低いオン抵抗が要求される。しかしながら従来のトレンチ構造MOSFETでは同一素子サイズでの低オン抵抗化が限界に達しつつあり、市場要求に対応することが難しくなってきた。

当社ではこの要求に応えるため、VFP構造のMOSFETを開発し、さらなる低オン抵抗化を図ることとした。

図 2 低電圧 MOSFET 市場マップ

#### 3. VFP-MOSFETの特徴

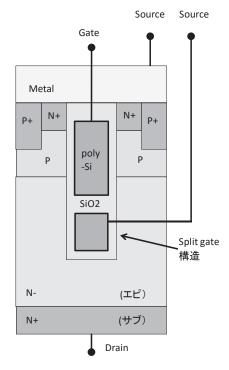

当社が開発したVFP-MOSFETは、 $R_{\rm epi}$ (エピ抵抗)と耐圧のトレードオフを改善し、低オン抵抗の要求に対応することができる。図3にVFP-MOSFETの構造を示す。特徴はGate電極の下にSource電位を持つVFP (Vertical Field Plate)を形成することである。これによりエピ層の電界を緩和でき、大幅なオン抵抗の低減を実現している。

図3 VFP-MOSFET のセル部イメージ図

### 4. 低ノイズ化技術

MOSFETの搭載機器では小型化、高効率化が求められている。一般に大電流化やスイッチング周波数を高周波化することで、これらの要求に応えてきた。しかし大電流化や高周波化により、機器から発生するノイズ量が増大し、今やEMI(電磁干渉)対策は非常に重要となっている。EMI対策を軽視することで、開発フェーズの後半に手戻りが発生し、開発期間とコストの両方に大幅な影響を及ぼすことがあるためである。EMI発生の主要因はMOSFETのターンオフ時のスパイクやリンギングノイズであるため、これらを抑制することがEIM対策として非常に重要である。

当社が開発したVFP-MOSFETの最大の特長は低ノイズである。ここでは低ノイズ化によるメリットを説明する。VFP-MOSFETの主な応用先は、コンバータ回路やモータドライバ回路である。これらの回路でもスイッチ

ング時に発生するリンギングや放射ノイズの発生が問題 となっている。

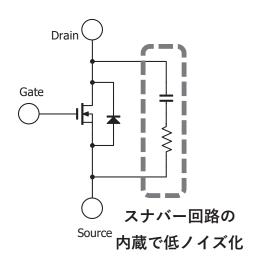

VFP-MOSFETには図4に示すように、ドレイン-ソース間に抵抗とコンデンサーによるスナバー回路が内蔵されている。さらにサンケン電気が独自開発した低ノイズ化技術と組み合わせることによりリンギングやノイズを抑えることに成功した。

図 4 VFP-MOSFET の等価回路図

#

他社A

3.6µsec以上

IS リンギング時間

VDS

Chil 10.0 V M 400ns A Ch4 3 1.30 A

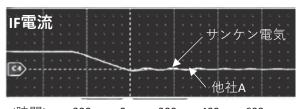

図5 trr (逆回復時間) の波形比較

20.00 %

図5にMOSFETのボディダイオードのリカバリー動作 時のリンギング時間を比較した波形を示す。VFP-MOSFET ではリンギング時間が0.5μsecであり、他社のMOSFET と比較して、大幅にリンギング時間が抑制されている。

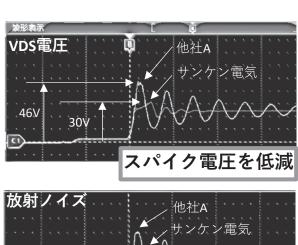

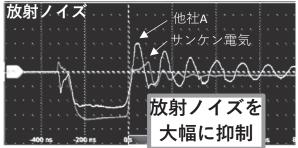

図6にはMOSFETのボディダイオードのリカバリー動作時のスパイク電圧と放射ノイズの波形比較を示す。 VFP-MOSFETではスパイク電圧が低減されており、放射ノイズも大幅に抑制していることから、EMI対策に有効なことが分かる。

(時間) -200ns Ons 200ns 400ns 600ns

図 6 ボディダイオードリカバリー動作時の放射ノイズの測定波形比較

| Part<br>number | VDS  | ID   | RDS (on)<br>(max.)     | Qg    | PKG   | Chip<br>in PKG | Wettable<br>flank |

|----------------|------|------|------------------------|-------|-------|----------------|-------------------|

| GKN04012       | 40V  | 120A | 1.24mΩ                 | 85nC  | DFN56 | 1in1           | 0                 |

| GKN04012N      |      |      |                        |       |       |                | ×                 |

| GKN04020       | 40V  | 90A  | 2.0mΩ                  | 56nC  | DFN56 | 1in1           | 0                 |

| GKN04020N      |      |      |                        |       |       |                | ×                 |

| GKN04050T      | 40V  | 20A  | 5.0mΩ                  | 22nC  | DFN56 | 2in1           | ×                 |

| HKT10018       | 100V | 300A | 1.8mΩ                  | 180nC | TOLL  | 1in1           | 0                 |

| HKT10024       | 100V | 220A | $2.4 \mathrm{m}\Omega$ | 120nC | TOLL  | 1in1           | 0                 |

| HKT10041       | 100V | 120A | 4.1mΩ                  | 70nC  | TOLL  | 1in1           | 0                 |

| GKN10059       | 100V | 90A  | 5.9mΩ                  | 45nC  | DFN56 | 1in1           | 0                 |

| GKN10059N      |      |      |                        |       |       |                | ×                 |

| GKN10026T      | 100V | 20A  | 26.0mΩ                 | 10nC  | DFN56 | 2in1           | ×                 |

図7 VFP-MOSFET 製品ラインアップ

## 5. 開発効果

低ノイズ化技術を採用することで,以下のメリットが 効果として期待されている。

#### 5.1 製品コストの低減

製品側でのスナバー回路の追加が不要となり、部品点数を削減できるため、ユーザー側での製品コストを低減できる。

### 5.2 効率アップと損失低減

VDSの絶対最大定格を超えないように、現行では、高耐圧仕様のMOSFETを採用しているが、スパイク電圧が抑制できたことで、低耐圧仕様も使用できる可能性がある。低耐圧化によって、さらなる低オン抵抗化が可能となり、効率アップや損失低減が期待できる。または、現行特性を維持する場合は、チップサイズを小さくできるので、コストを低減できる。

# 5.3 スイッチング損失抑制

インバータ回路でのゲート抵抗アップが不要となるため,スイッチング損失を抑制できる。

### 5.4 デッドタイム損失抑制

リンギングが少なくなることで、デッドタイムを短くできるため、デッドタイム損失を抑制できる。

# **6.** むすび

当社では市場からのさらなる高性能要求に応えるべく、VFP-MOSFET技術によるMOSFETの製品開発および新たなパッケージの開発に注力している。今後も市場からのニーズに応えるべく、製品開発を進めていく所存である。

<sup>\*</sup> 開発品のため、今後スケジュールに変更が生じる可能性があります