# NR111D Application Note Rev.3.1

# SANKEN ELECTRIC CO., LTD.

http://www.sanken-ele.co.jp

# **CONTENTS**

| General Descriptions                            | 3   |

|-------------------------------------------------|-----|

| 1. Electrical Characteristics                   | 4   |

| 1.1 Absolute Maximum Ratings                    | 4   |

| 1.2 Recommended Operating Conditions            | 4   |

| 1.3 Electrical Characteristics                  | 5   |

| 2. Block Diagram & Pin Functions                | 7   |

| 2.1 Functional Block Diagram                    | 7   |

| 2.2 Pin Asignments & Functions                  | · 7 |

| 3. Example Application Circuit                  | 8   |

| 4. Allowable package power dissipation          | 9   |

| 5. Package Outline                              | 10  |

| Pin assignments & functions                     | 11  |

| 6. Operational Descriptions                     | 12  |

| 6.1 PWM (Pulse Width Modulation) Output Control | 12  |

| 6.2 Power Supply Stability                      | 12  |

| 6.3 Over Current Protection (OCP)               | 13  |

| 6.4 Thermal Shutdown (TSD)                      | 13  |

| 6.5 Soft-Start                                  | 13  |

| 6.6 ON and OFF the Regulator (Enable)           | 14  |

| 6.7 SKIP Mode Operation in the Light Load       | 15  |

| 7. Design Notes                                 | 16  |

| 7.1 External Components                         | 16  |

| 7.2 Pattern Design                              | 22  |

| 7.3 Applied Design                              | 25  |

| IMPORTANT NOTICE                                | 27  |

#### **General Descriptions**

The NR111D is buck regulator ICs integrates High-side power MOSFETs. The feature increasing efficiency at light loads allows the device to be used in the energy-saving applications. With the current mode control, ultra low ESR capacitors such as ceramic capacitors can be used. The Ics have protection functions such as Over-Current Protection (OCP), Under-Voltage Lockout (UVLO) and Thermal Shutdown (TSD). An adjustable Soft-Start by an external capacitor prevents the excessive inrush current at turn-on. The Ics integrate phase compensation circuit which reduces the number of external components and simplifies the design of customer application. The ON/OFF pin (EN Pin) turns the regulator on or off and helps to achieve low power consumption requirements. The NR111D is available in an 8-pin DIP package.

#### **Features & Benefits**

- Current mode PWM control

- Up to 90% Efficiency, (V<sub>IN</sub>=12V,V<sub>O</sub>=5V,I<sub>O</sub>=1A)

Up to 68% Efficiency, (V<sub>IN</sub>=12V,V<sub>O</sub>=5V,I<sub>O</sub>=20mA)

- Stable with low ESR ceramic output capacitors

- Built-in protection function

Over Current Protection (OCP)

Thermal Shutdown (TSD)

Under Voltage Lockout (UVLO)

- Built-in phase compensation

- Adjustable Soft-Start with an external capacitor

- Turn ON/OF the regulator function

#### **Package**

• DIP8 Package

| 1 | BS   | $J_{\mathbf{SS}}$ | 8 |

|---|------|-------------------|---|

| 2 | IN   | EN                | 7 |

| 3 | SW I | SET               | 6 |

| 4 | GND  | FB                | 5 |

#### **Electrical Characteristics**

- 4A output current

- Operating input range  $V_{IN} = 6.5 V \sim 31 V$

- Output adjustable  $V_0 = 0.8V \sim 24V$

- Fixed 350kHz frequency

#### **Applications**

- LCD TV / Blu-Ray / Set top box

- Home appliance

- Green Electronic products

- Other power supply

**Series Lineup**

| Product No. | $ m f_{SW}$ | $f_{ m SW}$ $V_{ m IN}$ $V_{ m O}$ |                 | $I_{O}$ |

|-------------|-------------|------------------------------------|-----------------|---------|

| NR111D      | 350kHz      | 6.5V to 31V                        | 0.8V to 24V (2) | 4A      |

The minimum input voltage shall be either of 6.5V or  $V_0+3V$ , whichever is higher.

$<sup>^{(2)}</sup>$  The I/O condition is limited by the Minimum on-time ( $T_{ON(MIN)}$ ).

#### 1. Electrical Characteristics

# 1.1 Absolute Maximum Ratings

Table 1 Absolute maximum rating of NR111D

| Parameter                                 | _   | Symbol          | Ratings    | Units    | Conditions                                                                                    |

|-------------------------------------------|-----|-----------------|------------|----------|-----------------------------------------------------------------------------------------------|

| DC input voltage                          |     | $V_{IN}$        | 35         | V        |                                                                                               |

| BS Pin voltage                            |     | $V_{BS}$        | 44         | V        |                                                                                               |

| DC CW Din voltage                         |     | V               | 8          | V        | DC                                                                                            |

| BS-SW Pin voltage                         |     | $V_{BS-SW}$     | 12         | <b>"</b> | Pulse width ≤30ns                                                                             |

| SW Pin voltage                            |     | $V_{sw}$        | 35         | V        |                                                                                               |

| FB Pin voltage                            |     | $V_{FB}$        | 5.5        | V        |                                                                                               |

| EN Pin voltage                            |     | $V_{EN}$        | 35         | V        |                                                                                               |

| SS Pin voltage                            |     | V <sub>SS</sub> | 5.5        | V        |                                                                                               |

| Power dissipation                         | (3) | $P_{D}$         | 1.47       | W        | Glass-epoxy board mounting in a 70×60mm. (copper area in a 1310mm²) Max T <sub>J</sub> =150°C |

| Junction temperature                      | (4) | $T_{J}$         | -40 to 150 | °C       |                                                                                               |

| Storage temperature                       |     | $T_{S}$         | -40 to 150 | °C       |                                                                                               |

| Thermal resistance (junction- Pin No. 7)  |     | $	heta_{ m JP}$ | 41         | °C /W    |                                                                                               |

| Thermal resistance (junction-ambient air) |     | $	heta_{ m JA}$ | 85         | °C /W    | Glass-epoxy board mounting in a 70×60mm. (copper area in a 1310mm²)                           |

<sup>(3)</sup> Limited by thermal shutdown.

#### 1.2 Recommended Operating Conditions

Operating IC in recommended operating conditions is required for normal operating of circuit functions shown in Table 3 Electrical characteristics of NR111D.

Table 2 Recommended operating conditions of NR111D

| Donometer                     |            | Cymbol       | Ratii | ngs   | This | Conditions |

|-------------------------------|------------|--------------|-------|-------|------|------------|

| Parameter                     | Symbol     | MIN          | MAX   | Units |      |            |

| DC input voltage              | (5)        | $V_{\rm IN}$ | Vo+3  | 31    | V    |            |

| DC output current             | (6)<br>(7) | Io           | 0     | 4.0   | A    |            |

| Output voltage                |            | Vo           | 0.8   | 24    | V    |            |

| Ambient operating temperature | (7)        | Top          | -40   | 85    | °C   |            |

<sup>&</sup>lt;sup>(5)</sup> The minimum value of input voltage is taken as the larger one of either 6.5V or  $V_0 + 3V$ .

<sup>(4)</sup> The temperature detection of thermal shutdown is about 160°C

<sup>(6)</sup> Recommended circuit refer to Typical Application Circuit (fig.5).

<sup>&</sup>lt;sup>(7)</sup>To be used within the allowable package power dissipation characteristics (fig. 6)

#### 1.3 Electrical Characteristics

Electrical characteristics indicate specific limits, which are guaranteed when IC is operated under the measurement conditions shown in the circuit diagram (fig. 1)

Table 3 Electrical characteristics of NR111D

(Ta=25°C)

| Parameter                                          |                                           | Crymala o 1 | Ratings                     |       | T I '4 | Tt 1't' |                 |                                                                                    |

|----------------------------------------------------|-------------------------------------------|-------------|-----------------------------|-------|--------|---------|-----------------|------------------------------------------------------------------------------------|

|                                                    |                                           | Symbol      | MIN                         | TYP   | MAX    | Units   | Test conditions |                                                                                    |

| Reference vo                                       | oltage                                    |             | $V_{REF}$                   | 0.784 | 0.800  | 0.816   | V               | $V_{IN} = 12V, I_{O} = 1.0A$                                                       |

| Output voltage coefficient                         | ge temperature                            |             | $\angle V_{REF} / \angle T$ |       | ±0.05  |         | mV/°C           | $V_{IN} = 12V, I_O = 1.0A$<br>-40°C to +85°C                                       |

| Switching fr                                       | requency                                  |             | $f_{SW}$                    | -20%  | 350    | +20%    | kHz             | $V_{IN}=12V, V_{O}=5.0V, I_{O}=1^{\circ}$                                          |

| Line regulat                                       | ion                                       | (8)         | $V_{\mathrm{Line}}$         | _     | 50     | _       | mV              | $V_{IN}=8V\sim31V, V_{O}$<br>=5.0V, $I_{O}=1^{\circ}$<br>$V_{IN}=12V, V_{O}=5.0V,$ |

| Load regulat                                       | tion                                      | (8)         | $V_{Load}$                  | _     | 50     | _       | mV              | Io=0.1°∼2.0A                                                                       |

| Overcurrent p                                      | protection                                |             | $I_{S1}$                    | _     | 1.5    | _       |                 | V <sub>IN</sub> =12V, V <sub>O</sub> =5.0V<br>ISET=OPEN                            |

| threshold                                          | •                                         |             | $I_{S2}$                    | _     | 5.5    | _       | A               | $V_{IN} = 12V, V_O = 5.0V$<br>ISET=SHORT                                           |

| Supply Current                                     |                                           |             | $I_{IN}$                    | _     | 1      | _       | mA              | $V_{IN} = 12V$<br>$V_{EN} = 10k\Omega$ pull up to $V_{IN}$                         |

| Shutdown Supply Current                            |                                           |             | $I_{\rm IN(off)}$           | 0     | 1      | _       | μΑ              | $V_{IN} = 12V, I_{O} = 0A, V_{EN} = 0V$                                            |

| SS Pin                                             | Source current<br>at low level<br>voltage |             | I <sub>EN/SS</sub>          | 6     | 10     | 14      | μΑ              | V <sub>SS</sub> =0V, V <sub>IN</sub> =12V                                          |

| EN Pin                                             | Sink current                              |             | $I_{EN}$                    |       | 20     | 50      | μΑ              | $V_{EN}=10V$                                                                       |

| LINFIII                                            | Threshold voltage                         |             | V <sub>C/EH</sub>           | 0.7   | 1.4    | 2.1     | V               | $V_{IN} = 12V$                                                                     |

| ISET Pin                                           | Open voltage                              |             | $V_{ISET}$                  |       | 1.5    |         | V               | $V_{IN} = 12V$                                                                     |

| Max on-duty                                        |                                           | (8)         | $D_{MAX}$                   | _     | 90     | _       | %               |                                                                                    |

| Minimum on-time                                    |                                           | (8)         | T <sub>ON(MIN)</sub>        | _     | 150    |         | nsec            |                                                                                    |

| Thermal shutdown threshold temperature             |                                           | (8)         | TSD                         | 151   | 165    | _       | °C              |                                                                                    |

| Thermal shutdown restart hysteresis of temperature |                                           | (8)         | TSD_hys                     | _     | 20     | _       | °C              |                                                                                    |

<sup>(8)</sup> Guaranteed by design,not tested.

The input and output condition is limited by Minimum on-time.

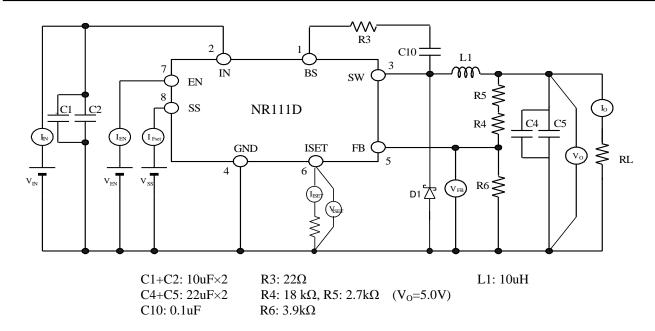

Fig.1 Measurement circuit diagram

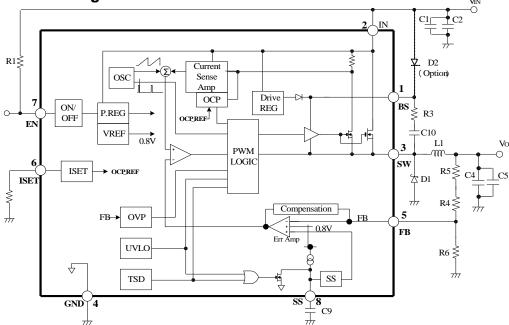

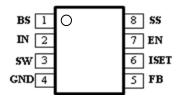

# 2. Block Diagram & Pin Functions

# 2.1 Functional Block Diagram

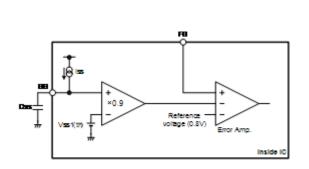

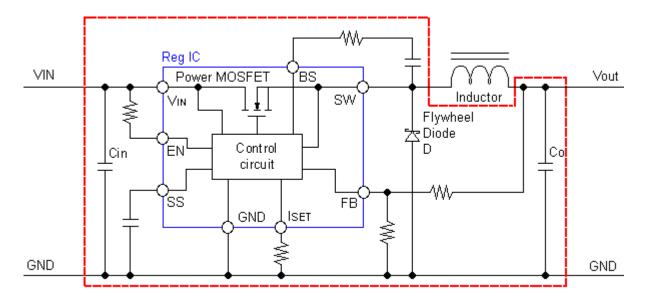

fig.2 Block diagram of NR111D

# 2.2 Pin Asignments & Functions

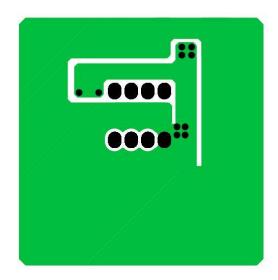

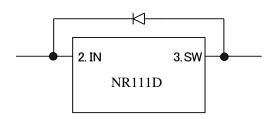

fig.3 Pin Assignments

Table2 Pin assignments & functions of NR111D

| Pin No. | Symbol | Description                                                                                                                                                                                    |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BS     | High-side Boost input. BS supplies the drive for High-side Nch-MOSFET switch. Connect a capacitor and a resistor between SW to BS.                                                             |

| 2       | IN     | Power input. IN supplies the power to the IC as well as the regulator switches                                                                                                                 |

| 3       | SW     | Power switching output. SW supplies power to the output. Connect the LC filter from SW to the output. Note that a capacitor is required from SW to BS to supply the power the High-side switch |

| 4       | GND    | Ground Connect the exposed pad to Pin No.4                                                                                                                                                     |

| 5       | FB     | Feedback input Pin to compare Reference Voltage. The feedback threshold is 0.8V.  To set the output voltage, FB Pin is required to connect between resistive voltage divider R4 and R6.        |

| 6       | ISET   | Adjust Pin of OCP starting current OCP starting current can be adjusted by connecting a resistor to ISET Pin. In the case of using at Maximum Io, ISET Pin is required to connect to GND.      |

| 7       | EN     | Enable input. Drive EN Pin high to turn on the regulator, low to turn it off.                                                                                                                  |

| 8       | SS     | Soft-Start control input.  To set the soft-start period, connect to a capacitor between GND.                                                                                                   |

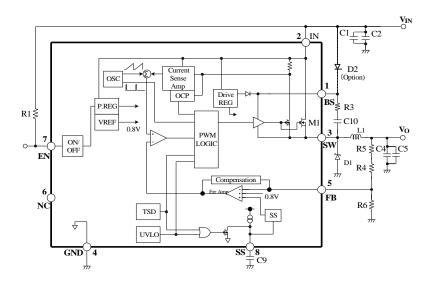

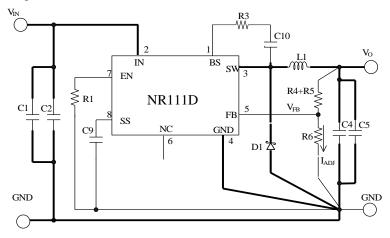

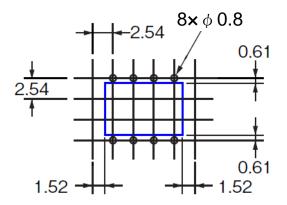

#### 3. Example Application Circuit

Each ground of all components is connected as close as possible to the Pin No.1 at one point.

To help heat dissipation, connect a large copper plane to exposed pad on the back side of the package. The copper plane is required for GND

fig. 4 Typical Application Circuit of NR111D

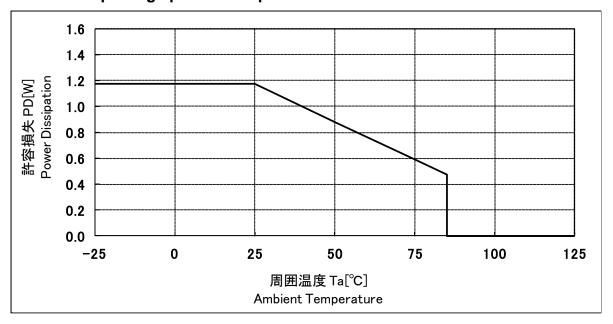

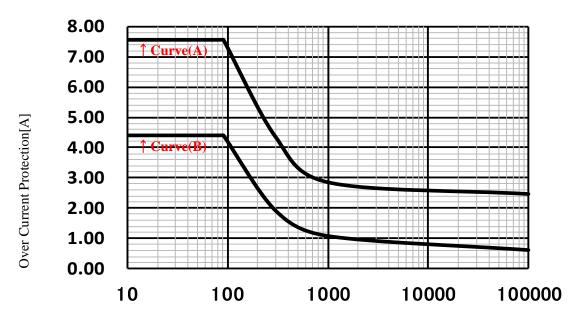

# 4. Allowable package power dissipation

fig. 5 Allowable package powe disspation of NR111D

#### NOTES:

- 1) Glass-epoxy board mounting in a 70×60mm

- 2) copper area: 1310mm<sup>2</sup>

- 3) The power dissipation is calculated at the junction temperature 125  $^{\circ}\text{C}$

- 4) Losses can be calculated by the following equation. As the efficiency is subject to the input voltage and output current, it shall be obtained from the efficiency curve and substituted in percent

$V_F$ : Diode forward voltage SJPB-L4…0.55V( $I_O$ =3A)

5) Thermal design for D1 shall be made separately.

$$P_D = V_O \cdot I_O \left(\frac{100}{\eta x} - 1\right) - V_F \cdot I_O \left(1 - \frac{V_O}{V_{IN}}\right) \qquad \begin{array}{c} V_O \text{: Output voltage} \\ \\ V_{IN} \text{: Input voltage} \\ \\ I_O \text{: Output current} \\ \\ \eta \text{ x: Efficiency(\%)} \end{array}$$

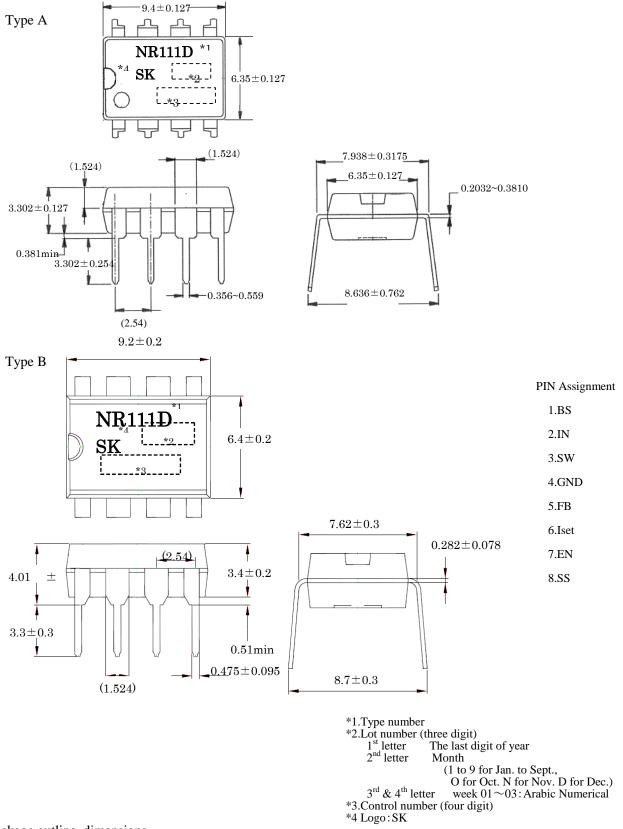

# 5. Package Outline

• Exposed SOIC8 package

An outside size is supplied by either Package type A or Package type B.

Package outline, dimensions

#### Note:

- 1 Dimension is in millimeters.

- 2. Drawing is not to scale.

Fig.7 Marking of NR111D

# Pin assignments & functions

fig. Pin Assignments of NR111D

Table Pin functions of NR111D

| Pin No. | Symbol | Description                                                                                     |

|---------|--------|-------------------------------------------------------------------------------------------------|

| 1       | BS     | High-side Boost input                                                                           |

|         |        | BS supplies the drive for High-side Nch-MOSFET switch.                                          |

|         |        | Connect a capacitor between SW to BS.                                                           |

| 2       | IN     | Power input                                                                                     |

|         |        | VIN supplies the power to the IC.                                                               |

| 3       | SW     | Power switching output                                                                          |

|         |        | SW supplies power to the output.                                                                |

|         |        | Connect the LC filter from SW to the output.                                                    |

|         |        | Note that a capacitor is required from SW to BS to supply the power the High-side switch        |

| 4       | GND    | Ground terminal                                                                                 |

|         |        | Connect the exposed pad to terminal No.4                                                        |

| 5       | FB     | Feedback input to compare Reference Voltage. The feedback threshold is 0.8V.                    |

|         |        | To set the output voltage, FB terminal is required to connect between resistive voltage divider |

|         |        | R4 and R6.                                                                                      |

| 6       | ISET   | Adjust Pin of OCP starting current                                                              |

|         |        | OCP starting current can be adjusted by connecting a resistor to ISET Pin.                      |

|         |        | In the case of Io=4A, ISET Pin is required to connect to GND.                                   |

| 7       | EN     | Enable input                                                                                    |

|         |        | Drive EN terminal high to turn on the regulator, low to turn it off.                            |

| 8       | SS     | Soft-Start control                                                                              |

|         |        | To set the soft-start period, connect to a capacitor between GND.                               |

# 6. Operational Descriptions

#### 6.1 PWM (Pulse Width Modulation) Output Control

The NR111D consist of three blocks; two feedback loops (voltage control and current control) and one slope compensation. The PWM is controlled with the current mode control by calculating the voltage feedback control, and the current feedback control and the slope compensation signals. (fig. 8) For the voltage feedback control, the output voltage feed back to the PWM control. The error amplifier compares the output voltage divided by resistors with the reference voltage  $V_{REF} = 0.8V$ . For the current feedback control, the inductor current feed back to the PWM control. The inductor current divided by Sense-MOSFET is detected with the current sense amplifier. To prevent sub-harmonic oscillations, which is characteristic in current mode control, the slope of current control is compensated.

Fig. 8 Basic Structure of Chopper Type Regulator with PWM Control by Current Control

The NR111D start the switching operation when UVLO is released, or EN or SS Pin voltage exceeds the threshold. Initially, it operates switching with minimum ON duty or maximum ON duty. The high-side switch (M1) is the switching MOSFET that supplies output power. At first, the boost capacitor C10 that drives M1 is charged by internal circuit. When M1 is ON, as the inductor current is increased by applying voltage to SW Pin and the inductor, the output of inductor current sense amplifier is also increased. Sum of the current sense amplifier output and slope compensation signal is compared with the error amplifier output. When the summed signal exceeds the error amplifier (Error Amp.) output voltage, the current comparator output becomes "High" and the RS flip-flop is reset. The regenerative current flows through D1, when the M1 turns OFF.

In NR111D, the set signal is generated in each cycle and RS flip-flop is set. In the case that the summed signal does not exceed the error amplifier (Error Amp.) output voltage, RS flip-flop is reset without fail by the signal from OFF duty circuit.

#### 6.2 Power Supply Stability

The phase characteristics of chopper type regulator are the synthesis of the internal phase characteristics of regulator IC, the combination of output capacitor C4 (C5) and load resistance Rout. The internal phase characteristics of regulator IC are generally determined by the delay time of control block and the phase characteristics of output error amplifier. The phase delay due to the delay time of control block is very small and not problem in actual use. As the built-in phase compensation for output error amplifier, in order to ensure stable operation, refer to "7.1.3 Output Capacitor C4 (C5)" and "7.1.4 Output Voltage Set-up (FB Pin)" for setting output capacitor and the output voltage.

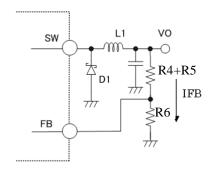

# **6.3 Over Current Protection (OCP)**

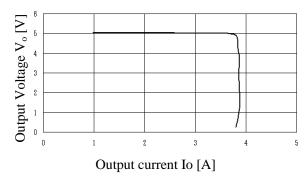

The NR111D integrate the drooping type over-current protection circuit. The peak current of switching transistor is detected. When the peak current exceeds rated value, the over-current protection limits the current by forcibly shortening the ON time of transistor and decreasing the output voltage. It prevents the current increment at low output voltage by decreasing the switching frequency, if the output voltage drops lower. When the over-current state is released, the output voltage automatically returns.

# 6.4 Thermal Shutdown (TSD)

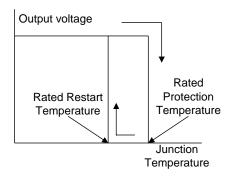

The thermal shutdown circuit detects the IC junction temperature. When the junction temperature exceeds the rated value (around 160°C), it shuts-down the output transistor and turns the output OFF. If the junction temperature falls below the thermal shutdown rated value by around 20°C, the operation returns automatically.

\* (Thermal Shutdown Characteristics) Notes

The circuit protects the IC against temporary heat generation. It does not guarantee the operation including reliabilities under the continuous heat generation conditions, such as short circuit for a long time.

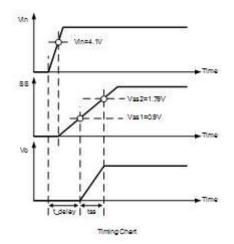

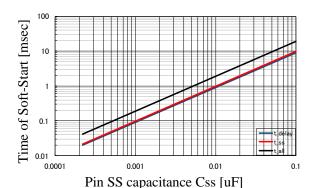

#### 6.5 Soft-Start

By connecting a capacitor between Pin No.8 (SS) and Pin No.4 (GND), Soft-Start operates when the power is supplied to the IC. Output Voltage (Vo) is ramped up by the charge voltage level of Css.

Time of Soft-Start can be calculated from the time constant of charging Css.

A capacitor Css controls OFF period of PWM and then the rise time is determined. The rise time t\_ss and the delay time t\_delay are calculated in following equations.

In the case of operating IC without using Soft-Start function, Pin No.4 is required for open.

$$\begin{split} T_{SS} &= C_{SS} \times (V_{SS2} - V_{SS1}) \, / \, (I_{SS} \times V_{SS1}) \\ &V_{SS1} \, (0.9V) < SS \, Pin \, voltage < V_{SS2} \, (1.79V) \end{split}$$

$$\begin{split} t\_delay &= C_{SS} \times V_{SS1} \ / \ I_{SS} \\ &SS \ Pin \ voltage < V_{SS1}(th) = V_{SS1} \ (0.9V) \end{split}$$

fig.12 Soft-Start operating description

fig.9 OCP Characteristics of NR111D

fig.10 TSD Characteristics of NR111D

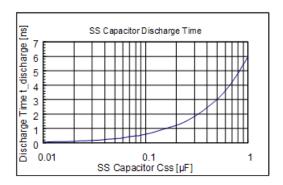

fig.11 SS Pin capacitance C<sub>SS</sub> VS Soft-Start

In the case of without or too small Css, IC starts up at the time constant that output current limited by Is charges output capacitor C2.

Following equation shows the time constant of start up by the output capacitor C2 at no load.

$$T = (C_O \times V_O) / I_S$$

\*At the start up with a load, load current is detracted from Is.

fig.13 Discharge time of SS capacitor

Pin SS Open Voltage: 3V SS Discharge Capability: 500μA

The left graph shows the SS Pin voltage changing

time from 3V to 0V.

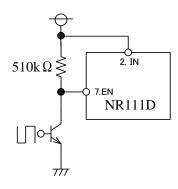

# 6.6 ON and OFF the Regulator (Enable)

EN Pin (Pin No.7) turns the regulator ON or OFF. When drive EN under 1.4V ( $V_{ENL}$ ), output is turned OFF (fig.14). 1.4V ( $V_{ENL}$ ) can be achieved by connecting a bipolar transistor in an open collector configuration.

When the external ON/OFF function isn't used, connect only Pull-up resistor of 510k  $\Omega$  between IN and EN. It starts when a VIN voltage is inputted.

fig. 14 ON / OFF Control

# 6.7 SKIP Mode operation in the Light Load

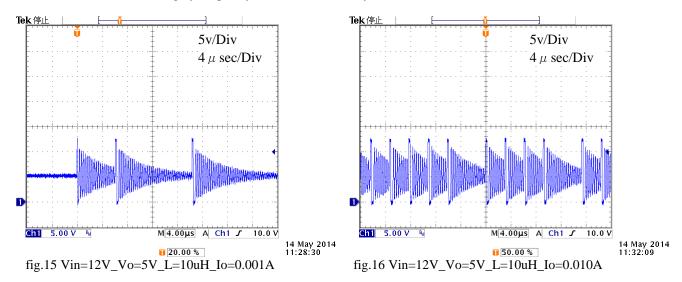

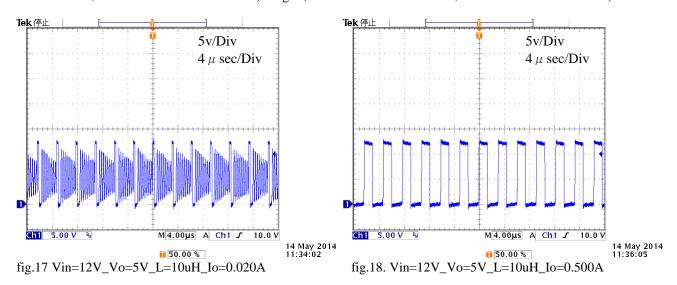

The NR111D has the skip mode (interval oscillation) in the light load. The on-width of the control is decreased in the light load, when it reaches  $T_{ON\,(MIN)}$  =150nsec (Typ),the switching mode shifts to the skip mode (interval oscillation). By shifting the skip mode, the output voltage rising in No-load can be eased. And, "Light load high efficiency" is realized by reducing the switching number of times per unit time. But, for the system which is a simple target,when the condition of the input voltage  $V_{IN}$  and the output voltage  $V_{O}$  changes, because a condition to shift to  $T_{ON} \rightarrow T_{ON\,(MIN)}$  changes,a transition load condition between the normal oscillation and the skip mode sometimes changes.

As for the following figure(fig15-fig18), they are the waveform example of the skip mode in the light load condition and continuous switching by frequency=350kHz in the heavy load condition.

\*fig15(Io=1mA skip mode) → fig16(Io=10mA End of the skip mode) → fig17(Io=20mA Normal oscillation, discontinuous inductor current) → fig18(Io=0.5A Normal oscillation, continuous inductor current)

# 7. Design Notes

#### 7.1 External Components

All components are required for matching to the condition of use.

#### 7.1.1 Choke Coil L1

The choke coil L1 is one of the most important components in the chopper type switching regulators. In order to maintain the stabilized regulator operation, the coil should be carefully selected so it must not enter saturation or over heat excessively at any conditions. The selection points of choke coil are as follows:

1. The coil type is only required for switching regulator.

It is recommended not to use a coil for noise filer since it causes high heat generation due to high power dissipation.

#### b) The sub-harmonic oscillations should be prevented.

Under the peak detection current control, the inductor current may fluctuate at a frequency that is an integer multiple of switching operation frequency. This phenomenon is the known as sub-harmonic oscillation and this phenomenon theoretically occurs in the peak detection current control mode. In order to stabilize the operation, the inductor current compensation is made internally. The inductance corresponding to the output voltage should be selected.

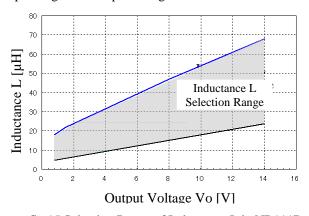

From fig.15 shows the selection range of inductance L to prevent the sub-harmonic oscillations. As for the upper limit of inductance L, the value is for reference, because it may vary depending on input/output conditions and load current.

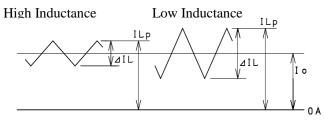

The ripple portion of choke coil current  $\Delta IL$  and the peak current Ilp are calculated from the following equations:

$$\Delta IL = \frac{(V_{\mbox{\footnotesize{IN}}} - V_{\mbox{\footnotesize{O}}}) \cdot V_{\mbox{\footnotesize{O}}}}{L \cdot V_{\mbox{\footnotesize{IN}}} \cdot f} \quad ---- (1)$$

$$IL_p = \frac{\Delta IL}{2} + I_o \qquad ---- (2)$$

The  $\Delta IL$  and Ilp increase when the inductance of the choke coil L becomes smaller.

If the inductance is too small, the regulator operation may be unstable because the choke coil current fluctuates largely. It is necessary to give attention to decreasing of the inductance due to the magnetic saturation such as in overload and load shortage.

fig.15 Selection Range of Inductance L in NR111D

fig.16 Relationship between inductance and ripple current

- c) The coil should be of proper rated current.

- The rated current of the choke coil should be higher than the maximum load current used. If the load current exceeds the rated current of coil, the inductance decreases drastically and eventually enters into the saturation state. In this status, it is necessary to give attention because the high-frequency impedance decreases and the excess current runs.

- d) The magnetic noise should be minimized.

The open magnetic circuit type core like a drum type may generate noise in peripheral circuit due to the magnetic flux passing outside of coil. Coils of closed magnetic circuit type core, such as toroidal type, EI type and EE type are preferable.

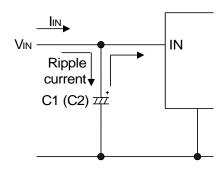

# 7.1.2 Input Capacitor C1 (C2)

The input capacitor operates as a bypass capacitor of input circuit. It supplies the short current pulses to the regulator during switching and compensates the input voltage drop. It should be connected close to the regulator IC. Even if the rectifying capacitor of AC rectifier circuit is in input circuit, the input capacitor cannot be used as a rectifying capacitor unless it is connected near IC.

The selection points of C1 (C2) are as follows:

- a) The capacitor should be of proper breakdown voltage rating

- b) The capacitor should have sufficient allowable ripple current rating

If the input capacitor C1 (C2) is used under the conditions of excessive breakdown voltage or allowable ripple current, or without derating, the regulator may become unstable and the capacitor's lifetime may be greatly reduced. The selection of the capacitor C1 (C2) is required for the sufficient margins to the ripple current. The effective value of ripple current Irms that flows across the input capacitor is calculated from the equation (3):

Irms

$$\approx 1.2 \times \frac{\text{Vo}}{\text{Vin}} \times \text{Io}^{----(3)}$$

In the case of  $V_{IN} = 20V$ ,  $I_0 = 3A$ ,  $V_0 = 5V$ ,

Irms

$$\approx 1.2 \times \frac{5}{20} \times 3 = 0.9$$

A

The capacitor is required for the allowable ripple current of 0.9A or higher.

fig. 17 C1 (C2) Current path

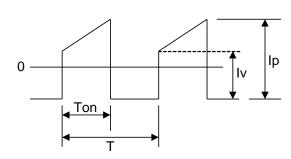

fig.18 C1 (C2) Current Waveform

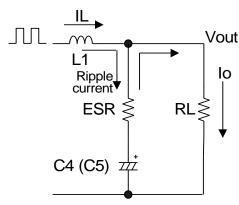

# 7.1.3 Output Capacitor C4 (C5)

In the current control mode, the feedback loop which detects the inductor current is added to the voltage control mode. The stable operation is achieved by adding inductor current to the feedback loop without considering the effect of secondary delay factor of LC filter. It is possible to reduce the capacitance of LC filter that is needed to make compensations for the secondary delay, and the stable operation is achieved even by using the low ESR capacitor (ceramic capacitor).

The output capacitor C4 (C5) comprises the LC low-pass filter with choke coil L1 and works as the rectifying capacitor of switching output. The current equal to ripple portion  $\Delta$ IL of choke coil current charges and discharges the output capacitor. In the same way as the input capacitor, the breakdown voltage and the allowable ripple current should be met with sufficient margins.

The ripple current effective value of output capacitor is calculated from the equation (4):

$$Irms = \frac{\Delta IL}{2\sqrt{3}} - (4)$$

When  $\Delta IL = 0.5A$ .

$$Irms = \frac{0.5}{2\sqrt{3}} = 0.14A$$

Therefore a capacitor with the allowable ripple current of 0.14A or higher is needed.

The output ripple voltage of regulator Vrip is determined by the product of choke current ripple portion  $\Delta IL$  (= C4 (C5) discharge and charge current) and output capacitor C4 (C5) equivalent series resistance ESR.

$$Vrip = \Delta IL \cdot C4_{ESR} \quad ---- (5)$$

It is necessary to select a capacitor with low equivalent series resistance ESR in order to lower the output ripple voltage. As for general electrolytic capacitors of same product series, the ESR shall be lower for products of higher capacitance with same breakdown voltage, or of higher breakdown voltage with same capacitance.

When  $\Delta IL = 0.5A$ , Vrip = 40mV,

$$C4_{ESR} = 40 \div 0.5 = 80 \text{m}\Omega$$

A capacitor with ESR of  $80m\Omega$  or lower should be selected. Since the ESR varies with temperature and increases at low temperature, it is required to check the ESR at the actual operating temperatures. It is recommended to contact capacitor manufacturers for the ESR value since it is peculiar to every capacitor series.

fig. 19 C4 (C5) Current path

fig. 20 C4 (C5) Current Waveform

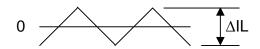

# 7.1.4 Output Voltage Set-up (FB Pin)

The FB Pin is the feedback detection Pin that controls the output voltage. It is recommended to connect close to the output capacitor C4 (C5). If they are not close, the abnormal oscillations may be caused by the poor regulation and the increased switching ripple.

The setting of output voltage is achieved by connecting between resistive voltage divider R4 (R5) and R6. Setting the  $I_{FB}$  to about 0.2mA is recommended.

(The target of  $I_{FB}$  lower limit is 0.2mA, and the upper limit is not defined. However, it is necessary to consider that the circuit current shall increase according to the  $I_{FB}$  value.)

R4 (R5), R6 and the output voltage are calculated from the following equations:

fig. 21 Detection and setting of output voltage

$$\begin{split} I_{FB} &= V_{FB} \, / \, R6 & *V_{FB} = 0.8V \pm 2\% \\ R4 + R5 &= ( \, V_O - VFB \, ) \, / \, I_{FB} \\ R6 &= V_{FB} \, / \, I_{FB} \\ V_O &= ( \, R4 + R5 \, ) \times ( \, VFB \, / \, R6 \, ) + VFB \end{split}$$

R6 is required to connect for the stable operation when set to  $V_0 = 0.8V$ .

Regarding the relation of input / output voltages, it is recommended that setting of the ON width of the SW Pin is more than 200nsec

The PCB circuit traces of FB Pin, R4 (R5) and R6 are required for not parallel to the flywheel diode. The switching noise may affect the detection voltage and the abnormal oscillation may be caused. Especially, it is recommended to design the circuit trace short from FB Pin to R6.

# 7.1.5 Flywheel Diode D1

A shcottky Barrier Diode as a flywheel diode is required for connection between SW Pin and GND.

The flywheel diode D1 is for releasing the energy stored in the choke coil at switching OFF. If a general rectifying diode or a fast recovery diode is used, the IC may fail to operate properly becase of applying reverse voltage due to the recovery and ON voltage. Since the output voltage from the SW Pin (Pin No. 3) is almost equal to the input voltage, it is required to use the flywheel diode with the reverse breakdown voltage of equal or higher than the input voltage. It is recommended not to use ferrite beads for flywheel diode.

#### 7.1.6 Output Voltage Vo and Output Capacitor C4 (C5)

From Table 6 shows the comparison of output voltage and output capacitor, for maintaining the IC stable operations, for reference.

ESR of Electrolytic Capacitor is required from  $100m\ \Omega$  to  $200m\Omega$ .

Regarding the inductance L, it is recommended to select it according to 7.1.1 Choke Coil L1.

Table 6 NR111D ( $f_{SW}$ =350kHz)  $V_O$  and C4 (C5) Comparison

| 14616 6111         | C4 (C5) (µF)      |                                       |  |  |  |

|--------------------|-------------------|---------------------------------------|--|--|--|

| V <sub>O</sub> (V) | Ceramic Capacitor | Electrolytic Capacitor<br>(ESR≒100mΩ) |  |  |  |

| 1.2                | 22 to 100         | 4.7 to 330                            |  |  |  |

| 1.8                | 22 to 100         | 4.7 to 470                            |  |  |  |

| 3.3                | 10 to 68          | 4.7 to 330                            |  |  |  |

| 5                  | 4.7 to 47         | 4.7 to 220                            |  |  |  |

| 9                  | 4.7 to 47         | 4.7 to 220                            |  |  |  |

| 12                 | 4.7 to 47         | 4.7 to 220                            |  |  |  |

| 16                 | 4.7 to 47         | 4.7 to 220                            |  |  |  |

| 20                 | 4.7 to 47         | 4.7 to 220                            |  |  |  |

| 24                 | 4.7 to 47         | 4.7 to 220                            |  |  |  |

#### 7.1.7 External Bootstrap Diode for Low

By connecting a resistor to the terminal 6, the over current value is set up. The relations of the peak electric current become the following characteristics at a resistance level and an overcurrent.

# NR111D Setup Over Current Protection Value

ISET terminal Resistance RISET[k  $\Omega$ ]

fig.22 Setup OverCurrent Protection Value

The vertical axis of the graph becomes the OCP start peak current.

The next expression is an expression to exchanging a peak current (Ilpeak) to for an output current (IO).

IO=Ilpeak  $- \angle$ IL $\times$ 0.5 Only continuous current mode are applied

$\triangle$ IL = Vo $\times$ (1-Vo/VIN)/(L $\times$ fo)

An OCP activation point can be adjusted by the setup value of RISET. However, because OCP-characteristic has the dispersion, the value of the Ip-detection to start OCP, it becomes the dispersion of between the curve(A) and the curve(B).

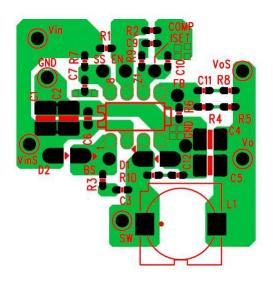

# 7.2 Pattern Design

#### 7.2.1 High Current Line

High current paths in the circuit are marked as bold lines in the circuit diagram below. These paths are required for wide and short trace as possible.

fig.23 Circuit Diagram

#### 7.2.2 Input / Output Capacitors

The input capacitor C1 (C2) and the output capacitor C4 (C5) are required to connect to the IC as short as possible. If the rectifying capacitor for AC rectifier circuit is in the input side, it can be also used as an input capacitor. However, if it is not close to the IC, the input capacitor is required to be connected in addition to the rectifying capacitor. Since the high current is discharged and charged with high speed through the leads of input / output capacitors, make the current paths as short as possible. A similar care should be taken when designing pattern for other capacitors.

fig. 24 Recommended Pattern example

fig. 25 No good pattern example

# 7.2.3 PCB Layout Pattern

Each ground of all components is connected as close as possible to the Pin No.4 at one point.

To help heat dissipation, connect a large copper plane to exposed pad on the back side of the package. The copper plane is required for GND

fig.26 Front Side: Component Side (double sided board)

fig.27 Back Side: GND Side (double sided board)

#### **NOTES:**

Size of the PCB is about 40mm×40mm

#### **NOTES:**

- 1) Dimension is in millimeters, dimension in bracket is in inches.

- 2) Drawing is not to scale.

fig.28 Recommended location of insertion hole

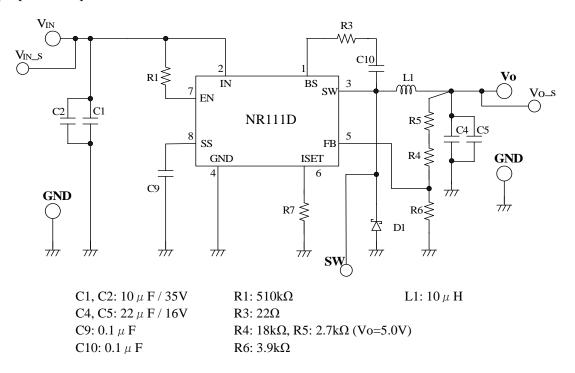

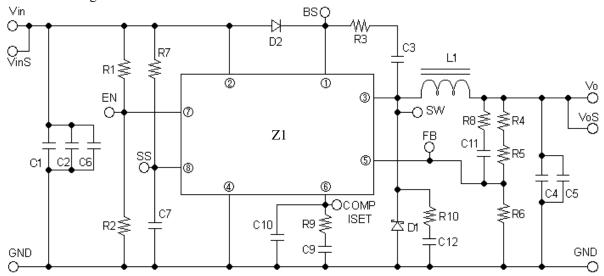

•The circuit diagram of Demo-board for Evaluation

fig.29 The circuit diagram of Demo-board for Evaluation

| C1, C2: 10µF / 35V | R1:510kΩ                   | L1: 10μH         |

|--------------------|----------------------------|------------------|

| C3:0.1µF           | R2: Option                 | D1:SJPW-T4       |

| C4, C5: 22µF / 16V | R3:22Ω                     | (Sanken)         |

| C6:Option          | R4:18kΩ                    | D2:Option        |

| C7: 0.1µF          | R5:2.7k $\Omega$ (Vo=5.0V) | Z1:NR111D        |

| C9: Short          | R6:3.9kΩ                   |                  |

| C10: Open          | R7:Open                    | *R9 refer to     |

| C11: Option        | R8: Option                 | Page20,Setup OCP |

| C12: Option        | R9:For adjust              | value            |

|                    | R10: Option                |                  |

The demonstration boards of the fig 26 and the fig 27 are some kinds of IC common use. This is the circuit board which contains optional part mounting for the experiment.

# 7.3 Applied Design

# 7.3.1 Spike Noise Reduction

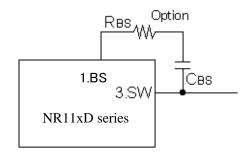

#### •The addition of the BS serial resistor

The "turn-on switching speed" of the internal Power-MOSFETcan be slowed down by inserting  $R_{\rm BS}$  (option) of the fig30.It is tendency that Spike noise becomes small by reducing theswitching-speed. Set up 22-ohm as an upper limit when you use  $R_{\rm BS}$ .

- \*Attention

- 1) When the resistance value of  $R_{BS}$  is enlarged by mistake toomuch, the internal power-MOSFET becomes an under-drive, it may be damaged worst.

- 2) The "defective starting-up" is caused when the resistance value of  $R_{\text{BS}}$  is too big.

- \*The BS serial resistor R<sub>BS</sub> is R3 in the Demonstration Board.

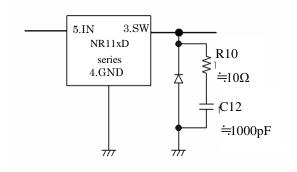

fig.30 The addition of the BS serial resistor

#### •The addition of the Snubber circuit

In order to reduce the spike noise, it is possible to compensate the output waveform and the recovery time of diode by connecting a capacitor and resistor parallel to the freewheel diode (snubber method). This method however may slightly reduce the efficiency.

\* For observing the spike noise with an oscilloscope, the probe lead (GND) should be as short as possible and connected to the root of output capacitor. If the probe GND lead is too long, the lead may act like an antenna and the observed spike noise may be much higher and may not show the real values.

\*The snubber circuit parts are C12 and R10.

fig.31 The addition of the Snubber circuit

#### ·Attention about the insertion of the bead-core

fig.32

#### In the area surrounded by the red dotted line within the fig32, don't insert the bead-core such as Ferrite-bead.

As for the pattern-design of printed-circuit-board, it is recommended that the parasitic-inductance of wiring-pattern is made small for the safety and the stability.

When bead-core was inserted, the inductance of the bead-core is added to parasitic-inductance of the wiring-pattern. By this influence, the surge-voltage occurs often, or , GND of IC becomes unstable, and also, negative voltage occurs often.

Because of this, faulty operation occurs in the IC. The IC has the possibility of damage in the worst case. About the Noise-reduction, fundamentally, Cope by "The addition of CR snubber circuit" and "The addition of BS serial resistor".

#### 7.3.2 Reverse Bias Protection

A diode for reverse bias protection may be required between input and output in case the output voltage is expected to be higher than the input Pin voltage (a common case in battery charger applications).

fig.33 Reverse bias protection diode

#### IMPORTANT NOTICE

- The contents in this document are subject to changes, for improvement and other purposes, without notice. Make sure that this is the latest revision of the document before use.

- Application and operation examples described in this document are quoted for the sole purpose of reference

for the use of the products herein and Sanken can assume no responsibility for any infringement of

industrial property rights, intellectual property rights or any other rights of Sanken or any third party which

may result from its use.

- Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device failure or malfunction.

- Sanken products listed in this document are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.).

- When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), please contact your nearest Sanken sales representative to discuss, prior to the use of the products herein.

- The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required (aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

- In the case that you use Sanken semiconductor products or design your products by using Sanken semiconductor products, the reliability largely depends on the degree of derating to be made to the rated values. Derating may be interpreted as a case that an operation range is set by derating the load from each rated value or surge voltage or noise is considered for derating in order to assure or improve the reliability. In general, derating factors include electric stresses such as electric voltage, electric current, electric power etc., environmental stresses such as ambient temperature, humidity etc. and thermal stress caused due to self-heating of semiconductor products. For these stresses, instantaneous values, maximum values and minimum values must be taken into consideration.

- In addition, it should be noted that since power devices or IC's including power devices have large self-heating value, the degree of derating of junction temperature affects the reliability significantly.

- When using the products specified herein by either (i) combining other products or materials therewith or (ii) physically, chemically or otherwise processing or treating the products, please duly consider all possible risks that may result from all such uses in advance and proceed therewith at your own responsibility.

- Anti radioactive ray design is not considered for the products listed herein.

- Sanken assumes no responsibility for any troubles, such as dropping products caused during transportation out of Sanken's distribution network.

The contents in this document must not be transcribed or copied without Sanken's written consent.