# Description

The SX68200M series are 3-phase brushless motor drivers in which output transistors, pre-drive circuits, bootstrap diodes with current-limiting resistors are highly integrated. Employing a sinusoidal driving strategy with a sensorless vector control, the SX68200M series brings a small-sized, high-efficient, and low-noise motor controlling into your application.

These products can run on a 3-shunt current detection system and optimally control the inverter systems of medium-capacity motors that require universal input standards.

## Features

- Pb-free (RoHS Compliant)

- UL-recognized: UL 60730-1 File No.:E99992 (SX68204M UL Recognition Pending)

- Sinusoidal Current Waveform (Low Noise, High Efficiency) Sensorless Vector Control (High Efficiency at Load

- Variation, Small Size)

- Built-in Bootstrap Diodes with Current-limiting Resistors

- EEPROM as a Control Parameter Storage

- Two Speed Control (PI Control) Modes:

- Analog Voltage Control (VSP Pin)

- Serial Communications Control (I<sup>2</sup>C Compatible)

- 3-shunt Current Detection

- DIAG Pin Fault Signal Output

- Protections Include:

- V3 Pin Undervoltage Protection

- Watchdog Timeout Detection

- Memory Error Detection

- Overvoltage Protection and Undervoltage Lockout for Main Power Supply (VM Pin)

- Soft Overcurrent Protection

- Hard Overcurrent Protection

- Thermal Warning

- Thermal Shutdown

- Undervoltage Lockout for Logic Supply

- Loss-of-Synchronization Protection

# Package

Not to scale

# **Selection Guide**

| Part Number | V <sub>DSS</sub> | Io    |

|-------------|------------------|-------|

| SX68201M    | 250 V            | 2.0 A |

| SX68204M*   | 600 V            | 1.5 A |

| SX68205M    | 600 V            | 2.0 A |

\* Under development

# Applications

For motor drives such as:

- Fan Motor for Air Conditioner

- Fan Motor for Air Purifier and Electric Fan

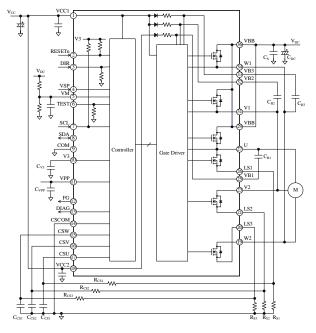

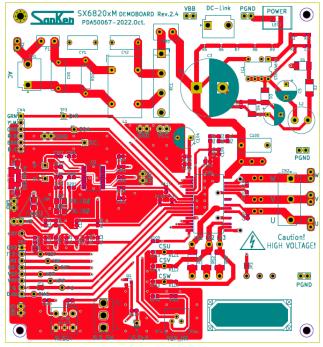

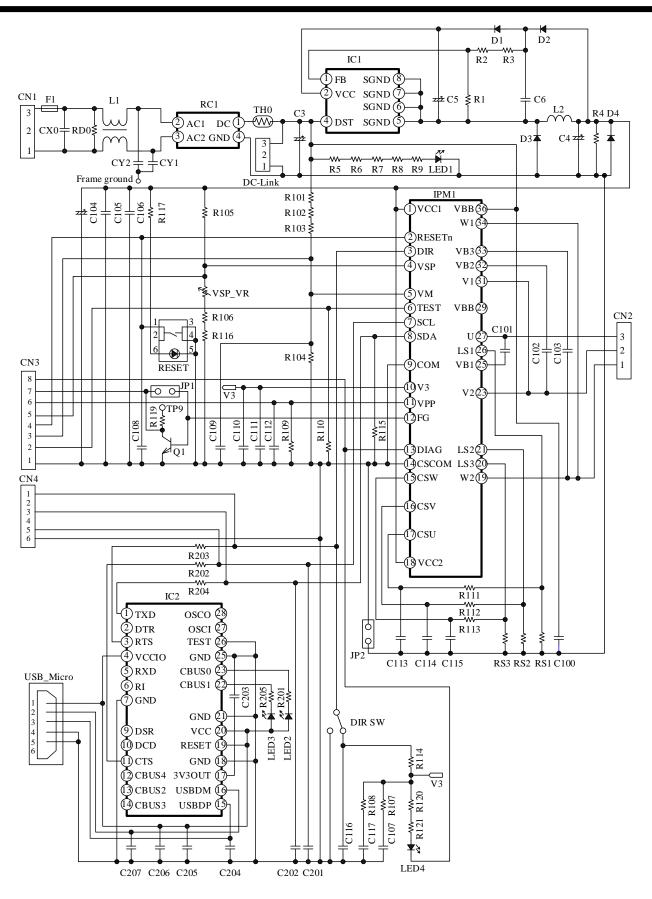

# **Typical Application**

# Contents

| Description                                                                          | 1    |

|--------------------------------------------------------------------------------------|------|

| Contents                                                                             | 2    |

| 1. Absolute Maximum Ratings                                                          | 4    |

| 2. Recommended Operating Conditions                                                  | 5    |

| 3. Electrical Characteristics                                                        |      |

| 3.1. Characteristics of Control Parts                                                | 6    |

| 3.2. Serial Communications                                                           |      |

| 3.3. Transistor Characteristics                                                      |      |

| 3.3.1. SX68201M                                                                      |      |

| 3.3.2. SX68204M                                                                      |      |

| 3.3.3.       SX68205M         3.4.       Bootstrap Diode Characteristics             |      |

| 3.4. Bootstrap Diode Characteristics         3.5. Thermal Resistance Characteristics |      |

| <ol> <li>Mechanical Characteristics</li> </ol>                                       |      |

|                                                                                      |      |

| 5. Reference Register Value                                                          |      |

| 6. Block Diagram                                                                     |      |

| 7. Pin Configuration Definitions                                                     | 15   |

| 8. Typical Application                                                               | 16   |

| 9. Physical Dimensions                                                               | 17   |

| 10. Marking Diagram                                                                  | 18   |

| 11. Functional Descriptions                                                          |      |

| 11.1. Basic Operation                                                                | 19   |

| 11.2. Pin Descriptions                                                               |      |

| 11.2.1. VCC1 and VCC2                                                                |      |

| 11.2.2. RESETn                                                                       | - 19 |

| 11.2.3. DIR                                                                          |      |

| 11.2.4. VSP                                                                          |      |

| 11.2.5. VM                                                                           |      |

| 11.2.6. TEST                                                                         |      |

| 11.2.7. SCL                                                                          |      |

| 11.2.8. SDA                                                                          |      |

| 11.2.9. COM                                                                          |      |

| 11.2.10. V3                                                                          | · 21 |

| 11.2.11. VPP                                                                         |      |

| 11.2.12. FG                                                                          |      |

| 11.2.13. DIAG                                                                        |      |

| 11.2.14. CSCOM                                                                       |      |

| 11.2.16. VBB                                                                         |      |

| 11.2.17. VB1, VB2, and VB3                                                           |      |

| 11.2.18. U, V1, V2, W1, and W2                                                       | 22   |

| 11.2.19. LS1, LS2, and LS3                                                           |      |

| 11.3. Closed-loop Speed Control                                                      | - 23 |

| 11.4. Startup                                                                        | 23   |

| 11.5. Windmilling                                                                    |      |

| 11.6. Motor Control                                                                  |      |

| 11.7. Motor Speed Setting                                                            | 25   |

| 11.8. Low Power Consumption Mode                                                     | 26   |

| 11.9. PWM Control                                                                    |      |

| 11.10.Dead Time                                                                      | - 26 |

| 11.11.PWM Switching Mode                                                       | 26       |

|--------------------------------------------------------------------------------|----------|

| 11.12.Charging of Bootstrap Capacitors                                         | 27       |

| 11.13.Current Detection                                                        | 27       |

| 11.14.Diagnostic Function                                                      | 28       |

| 11.14.1. DIAG Pin Output                                                       | 28       |

| 11.14.2. Diagnostic Register                                                   | 28       |

| 11.14.3. Protective Operations at Fault Detection                              | 28       |

| 11.14.4. Fault Mask Setting                                                    | 29       |

| 11.15.Protection Functions                                                     | 29       |

| 11.15.1. V3 Pin Undervoltage Protection                                        |          |

| 11.15.2. Watchdog Timeout                                                      | 29       |

| 11.15.3. Memory Error                                                          | 29       |

| 11.15.4. Overvoltage Protection and Undervoltage Lockout for Main Power Supply | 30       |

| 11.15.5. Overcurrent Protections                                               | 30       |

| 11.15.6. Soft Overcurrent Protection                                           | 30       |

| 11.15.7. Hard Overcurrent Protection                                           | 31       |

| 11.15.8. Thermal Warning and Thermal Shutdown                                  | 31       |

| 11.15.9. Undervoltage Lockout for Logic Supply                                 | 31       |

| 11.15.10. Loss-of-Synchronization Protection                                   | 32       |

| 11.16.Serial Communications                                                    | 33       |

| 11.17.EEPROM                                                                   |          |

| 11.17.1. Register Data Saving                                                  |          |

| 11.17.2. Locking by Password                                                   |          |

| 11.18.Register Overview                                                        | 37       |

| 11.19.Register Map                                                             | 38       |

| 11.20.Configuration Registers                                                  | 39       |

| 11.20.1. System Configuration Registers                                        | 39       |

| 11.20.2. Startup Setting Registers                                             | 42       |

| 11.20.3. Motor Control Setting Registers                                       | 43       |

| 11.20.4. Speed Setting Registers                                               | 48       |

| 11.20.5. Internal Control Setting Registers                                    | 51       |

| 12. Design Notes                                                               | 55       |

| 12. Design Notes                                                               | 33<br>55 |

| 12.1. Notes on the Sequences for Turning On/On the IC                          | 55<br>55 |

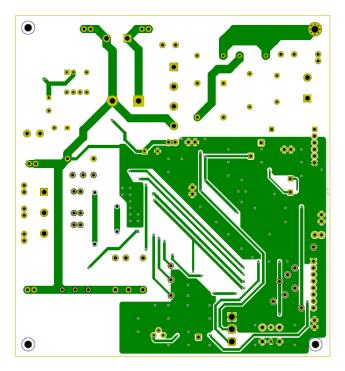

| 12.2. 1 CD Fatterin Layout                                                     |          |

|                                                                                |          |

| 13. Calculating Power Losses and Estimating Junction Temperature               | 56       |

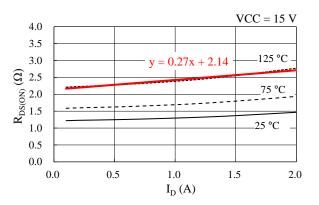

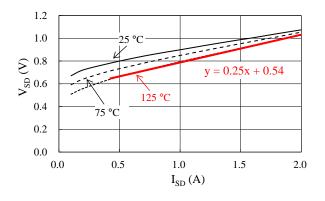

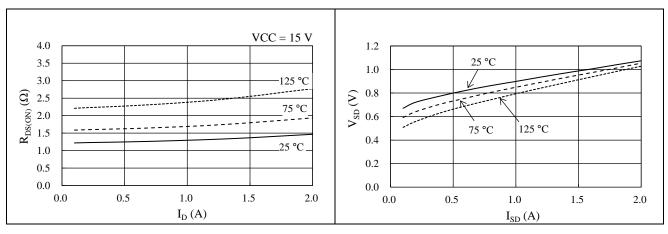

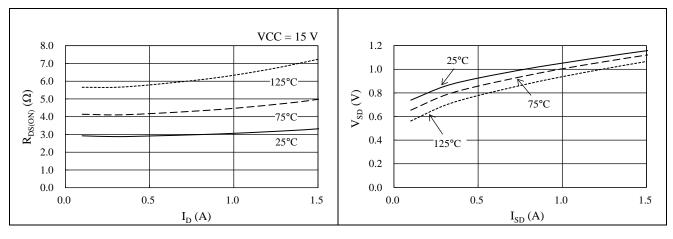

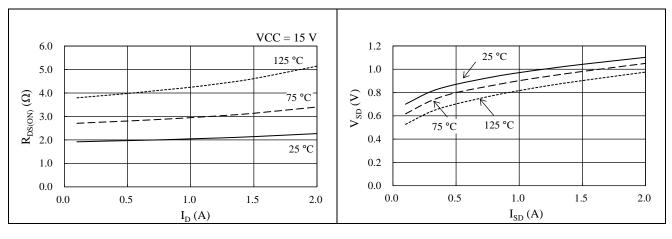

| 13.1. Power MOSFET Steady-state Loss, PRON                                     | 56       |

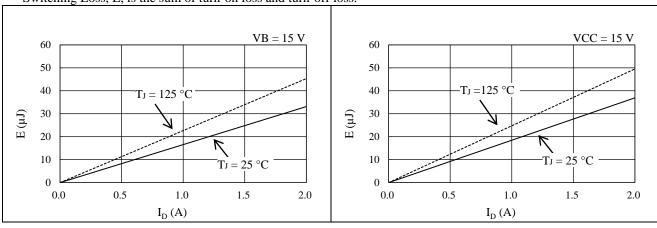

| 13.2. Power MOSFET Switching Loss, Psw                                         | 57       |

| 13.3. Body Diode Steady-state Loss, P <sub>SD</sub>                            | 57       |

| 13.4. Estimating Junction Temperature of Power MOSFET                          | 57       |

| 14. Performance Curves                                                         | 58       |

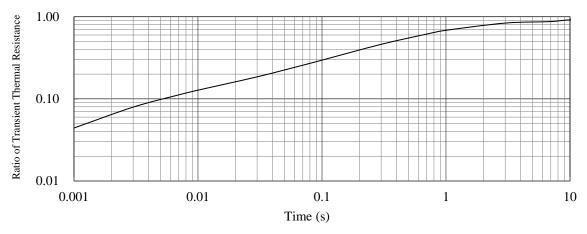

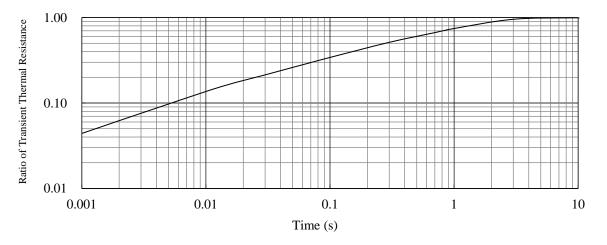

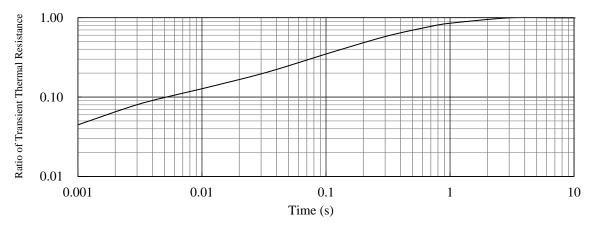

| 14.1. Transient Thermal Resistance Curves                                      |          |

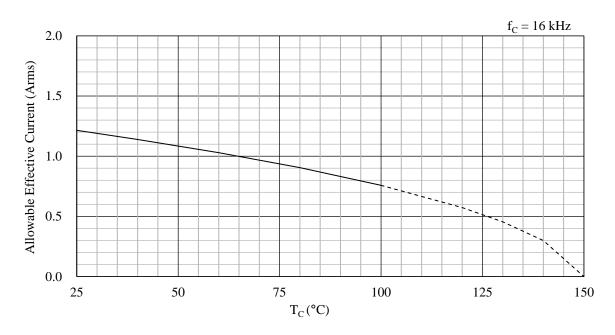

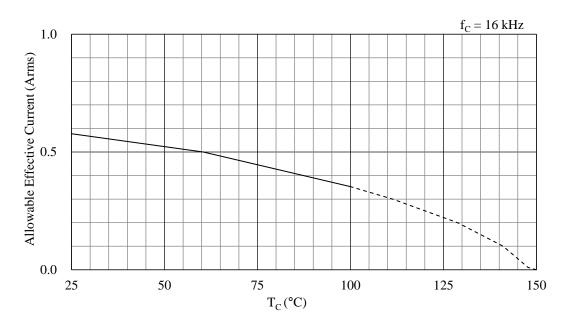

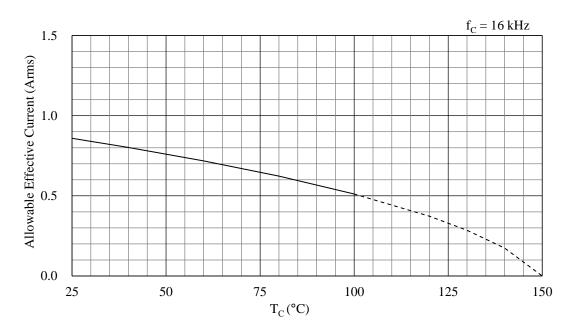

| 14.1. Allowable Effective Current Curves                                       |          |

| 14.2.1. SX68201M                                                               |          |

| 14.2.2. SX68204M                                                               |          |

| 14.2.3. SX68205M                                                               |          |

| 14.3. Performance Curves of Output Parts                                       |          |

| 14.3.1. Output Transistor Performance Curves                                   | 62       |

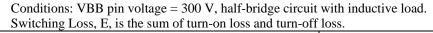

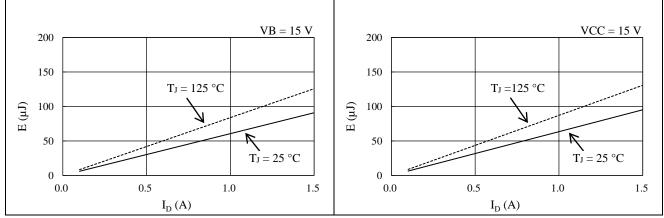

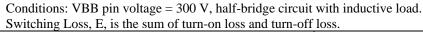

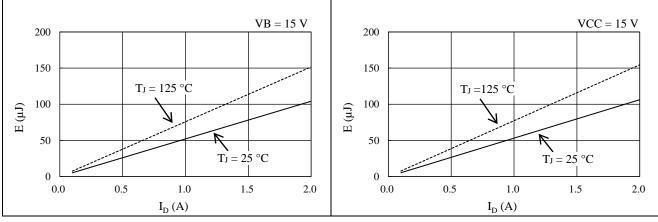

| 14.3.2. Switching Loss Curves                                                  | 64       |

| -                                                                              |          |

| 15. Pattern Layout Example                                                     |          |

| 16. Typical Motor Driver Application                                           | 68       |

| Important Notes                                                                | 70       |

# 1. Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (-).

| Parameter                                                         | Symbol             | Conditions                                                                         | Rating           | Unit | Remarks              |

|-------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------|------------------|------|----------------------|

| Power MOSFET                                                      |                    | $V_{\rm CC} = 15  \rm V,$                                                          | 250              |      | SX68201M             |

| Breakdown Voltage                                                 | V <sub>DSS</sub>   | $I_{\rm D} = 100 \ \mu {\rm A}$                                                    | 600              | V    | SX68204M<br>SX68205M |

|                                                                   | V <sub>CC</sub>    | VCC1–COM,<br>VCC2–COM                                                              | 20               |      |                      |

| Logic Supply Voltage                                              | V <sub>BS</sub>    | VB1–U,<br>VB2–V1,<br>VB3–W1                                                        | 20               | V    |                      |

|                                                                   |                    | $T_{\rm C} = 25 ^{\circ}{\rm C},$                                                  | 1.5              |      | SX68204M             |

| Output Current <sup>(1)</sup>                                     | Io                 | $T_{\rm J}$ < 150 °C                                                               | 2.0              | A    | SX68201M<br>SX68205M |

|                                                                   |                    | $T_{\rm C} = 25 ^{\circ}{\rm C},$                                                  | 2.25             |      | SX68204M             |

| Output Current (Pulse)                                            | I <sub>OP</sub>    | $V_{CC} = 15 \text{ V},$<br>pulse width $\leq 100 \mu\text{s},$<br>duty cycle = 1% | 3                | А    | SX68201M<br>SX68205M |

| Logic Input Voltage                                               | V <sub>IN(1)</sub> | DIR-COM,<br>SCL-COM,<br>SDA-COM                                                    | -0.3 to 5.5      | V    |                      |

|                                                                   | V <sub>IN(2)</sub> | VSP–COM                                                                            | -0.3 to 8.5      | V    |                      |

| Logic Output Voltage                                              | Vo                 | FG–COM,<br>DIAG–COM                                                                | -0.3 to V3 + 0.3 | V    |                      |

| VPP Pin Voltage                                                   | $V_{PP}$           | VPP–COM                                                                            | -0.3 to 28       | V    |                      |

| RESETn Pin Voltage                                                | V <sub>RST</sub>   | RESETn-COM                                                                         | -0.3 to 5.5      | V    |                      |

| VM Pin Voltage                                                    | V <sub>VM</sub>    | VM–COM                                                                             | -0.3 to 4        | V    |                      |

| Input Pin Voltage for<br>Current-sensing<br>Operational Amplifier | V <sub>CSX</sub>   | CSU–COM,<br>CSV–COM,<br>CSW–COM,<br>CSCOM–COM                                      | -2 to 2          | V    |                      |

| Allowable Power<br>Dissipation                                    | P <sub>D</sub>     | $T_A = 25$ °C; when<br>mounted on a board <sup>(2)</sup>                           | 3.5              | W    |                      |

| Operating Case<br>Temperature <sup>(3)</sup>                      | T <sub>C(OP)</sub> |                                                                                    | -25 to 100       | °C   |                      |

| Junction Temperature <sup>(4)</sup>                               | TJ                 |                                                                                    | 150              | °C   |                      |

| Storage Temperature                                               | T <sub>STG</sub>   |                                                                                    | -40 to 150       | °C   |                      |

Unless specifically noted,  $T_A = 25 \text{ °C}$ .

<sup>&</sup>lt;sup>(1)</sup> Should be derated depending on an actual case temperature. See Section 14.2.

<sup>&</sup>lt;sup>(2)</sup> Refers to a 1.6 mm thick CEM3 glass with 35 μm thick copper foil; measured under natural air-cooling without silicone potting.

<sup>&</sup>lt;sup>(3)</sup> Refers to a case temperature measured during IC operation.

<sup>&</sup>lt;sup>(4)</sup> Refers to the junction temperature of each chip built in the IC, including the control stage, gate drive stage, power MOSFETs, and bootstrap diodes.

| Parameter                                            | Symbol             | Conditions                      | Min. | Тур. | Max. | Unit | Remarks              |

|------------------------------------------------------|--------------------|---------------------------------|------|------|------|------|----------------------|

|                                                      |                    |                                 |      | 140  | 200  |      | SX68201M             |

| Main Supply Voltage                                  | $V_{\text{DC}}$    | VBB-COM                         |      | 280  | 400  | V    | SX68204M<br>SX68205M |

| Logic Supply Voltage                                 | V <sub>CC</sub>    | VCC1–COM,<br>VCC2–COM           | 13.5 | _    | 16.5 | V    |                      |

|                                                      | $V_{BS}$           | VB1–U,<br>VB2–V1,<br>VB3–W1     | 13.5 | _    | 16.5 | v    |                      |

| Input Voltage                                        | V <sub>IN(1)</sub> | DIR–COM,<br>SCL–COM,<br>SDA–COM | 0    |      | 5.0  | v    |                      |

|                                                      | V <sub>IN(2)</sub> | VSP-COM                         | 0    | _    | 5.88 | V    |                      |

| EEPRM Write Supply<br>Voltage                        | $V_{PP}$           |                                 |      | 24   |      | V    |                      |

| Wait Time for<br>Programming Supply<br>Voltage Setup | t <sub>PRS</sub>   |                                 | 50   |      | _    | ms   |                      |

| VM Pin Input Voltage<br>Range for Main Supply        | $V_{M}$            |                                 | 0    | _    | 1.8  | V    |                      |

| Dead Time of Input Signal                            | t <sub>DEAD</sub>  | DT[5:0] = [011110]              | 1.5  | —    | —    | μs   |                      |

| Bootstrap Capacitor                                  | C <sub>BOOT</sub>  |                                 | 1    |      | 10   | μF   |                      |

|                                                      |                    | $I_{OP} \leq 3.0 \text{ A}$     | 0.22 |      |      |      | SX68201M             |

| Shunt Resistor*                                      | R <sub>Sx</sub>    | $I_{OP} \le 2.25 \text{ A}$     | 0.29 |      |      | Ω    | SX68204M             |

|                                                      |                    | $I_{OP} \leq 3.0 \text{ A}$     | 0.22 |      |      |      | SX68205M             |

# 2. Recommended Operating Conditions

\* Refers to the reference values calculated with a minimum value of V<sub>TRIPH</sub>; should be a low-inductance resistor.

# 3. Electrical Characteristics

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (-).

Unless specifically noted,  $T_A = 25$  °C,  $V_{CC} = 15$  V.

# **3.1.** Characteristics of Control Parts

| Parameter                                                        | Symbol                | Conditions                                                                                         | Min.        | Тур.        | Max.  | Unit |

|------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|-------------|-------------|-------|------|

| Power Supply Operation                                           | 1                     |                                                                                                    |             |             |       |      |

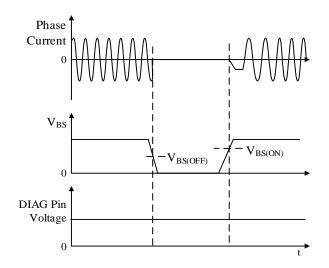

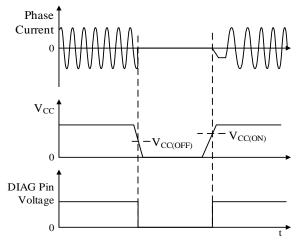

| VCCx Pin Logic Operation Start<br>Voltage                        | V <sub>CC(ON)</sub>   | V <sub>CC</sub> rising;<br>VCC1–COM,<br>VCC2–COM                                                   | 10.5        | 11.5        | 12.5  | V    |

| VCCx Pin Logic Operation Stop<br>Voltage                         | V <sub>CC(OFF)</sub>  | V <sub>CC</sub> falling;<br>VCC1–COM,<br>VCC2–COM                                                  | 10.0        | 11.0        | 12.0  | V    |

| VBx Pin Logic Operation Start<br>Voltage                         | V <sub>BS(ON)</sub>   | V <sub>BS</sub> rising;<br>VB1–U, VB2–V1, VB3–W1                                                   | 9.5         | 10.5        | 11.5  | V    |

| VBx Pin Logic Operation Stop<br>Voltage                          | V <sub>BS(OFF)</sub>  | V <sub>BS</sub> falling;<br>VB1–U, VB2–V1, VB3–W1                                                  | 9.0         | 10.0        | 11.0  | V    |

| VCCx Pin Logic Supply Current (in Operation)                     | I <sub>CC</sub>       | $V_{SP} > V_{SSX}$ with no<br>oscillation; VCC1 = VCC2,<br>VCC pin current in 3-phase<br>operation |             | _           | 30    | mA   |

| VCCx Pin Logic Supply Current<br>(in Low Power Consumption Mode) | I <sub>CCSTBY</sub>   | $V_{SP} < V_{VSSN}$                                                                                |             | _           | 150   | μΑ   |

| VBx Pin Logic Supply Current                                     | I <sub>BS</sub>       | $V_{BS} = 15 \text{ V}, V_{SP} = 5.4 \text{ V};$<br>VBx pin current in 1-phase operation           | 40          | 120         | 350   | μΑ   |

| Regulator Output Voltage                                         | <b>V</b> <sub>3</sub> | No load                                                                                            | 3           | 3.3         | 3.7   | V    |

| Input Current for EEPROM Write<br>Supply Voltage                 | $I_{PP}$              |                                                                                                    |             | 7           |       | mA   |

| VM Pin Input Voltage Range                                       | $V_{M}$               |                                                                                                    | 0           | —           | 1.8   | V    |

| VM Pin Input Current                                             | I <sub>VM</sub>       | $0 < V_M < 1.8 V$                                                                                  | -2.5        |             | 2.5   | μA   |

| VSP Pin Input Current                                            | $I_{VSP}$             | $V_{SP} = 5.5 \text{ V}$                                                                           | 10          | _           | 45    | μA   |

| Input Signal                                                     |                       |                                                                                                    |             |             |       |      |

| DIR Pin Low Level Input Voltage <sup>(1)</sup>                   | V <sub>IL1</sub>      |                                                                                                    |             |             | 0.76  | V    |

| DIR Pin High Level Input Voltage <sup>(1)</sup>                  | V <sub>IH1</sub>      |                                                                                                    | 2.04        |             |       | V    |

| DIR Pin Internal Pull-down Resistor                              | R <sub>PD</sub>       |                                                                                                    | 25          | 50          | 75    | kΩ   |

| RESETn Pin Low Level Input<br>Voltage <sup>(1)</sup>             | V <sub>ILR</sub>      |                                                                                                    |             |             | 0.3   | V    |

| RESETn Pin High Level Input<br>Voltage <sup>(1)</sup>            | V <sub>IHR</sub>      |                                                                                                    | 2.3         |             |       | V    |

| RESETn Pin Internal Pull-up<br>Resistor                          | R <sub>PU</sub>       |                                                                                                    |             | 90          |       | kΩ   |

| FG Pin High Level Output Voltage                                 | V <sub>OH</sub>       | $I_{OH} = -1 \text{ mA}$                                                                           | $V_3 - 0.5$ | $V_3 - 0.2$ | $V_3$ | V    |

| DIAG Pin Internal Pull-up Resistor                               | R <sub>OH</sub>       |                                                                                                    |             | 10          |       | kΩ   |

| DIAG Pin, FG Pin Low Level Output<br>Voltage                     | V <sub>OL1</sub>      | $I_{OH} = 1 \text{ mA}$                                                                            |             | 0.2         | 0.45  | V    |

<sup>(1)</sup> When applying an external voltage, be sure to set the DIR and RESETn pins to logic low during IC startup (i.e., until the V3 pin voltage is established).

| Parameter                                               | Symbol              | Conditions             | Min.    | Тур. | Max.   | Unit              |

|---------------------------------------------------------|---------------------|------------------------|---------|------|--------|-------------------|

|                                                         | Symbol              | Conditions             | IVIIII. | ryp. | Iviax. | Unit              |

| Motor Control                                           | 1                   |                        | 1       | 1    |        |                   |

| VSP Pin Startup Voltage                                 | V <sub>SSX</sub>    | V <sub>SP</sub> rising | 1.13    | 1.26 | 1.4    | V                 |

| Hold Time for Initial Positioning <sup>(2)</sup>        | t <sub>HOLD</sub>   |                        | 282     | 353  | 424    | ms                |

| Dead Time                                               | DT                  |                        | 1.425   | 1.5  | 1.575  | μs                |

| Protection                                              |                     |                        |         |      |        |                   |

| Current Limiting Value <sup>(2)</sup>                   | I <sub>LIM</sub>    |                        | 78      | 80   | 82     | % I <sub>FS</sub> |

| OCP Threshold Voltage <sup>(2)</sup>                    | V <sub>TRIPS</sub>  |                        | 0.39    | 0.40 | 0.41   | V                 |

| VM Pin OVP Threshold Voltage <sup>(2)</sup>             | V <sub>OVM</sub>    |                        | 1.1     | 1.24 | 1.35   | V                 |

| VM Pin UVP Threshold Voltage <sup>(2)</sup>             | V <sub>UVM</sub>    |                        | 0.20    | 0.29 | 0.38   | V                 |

| V3 Pin UVP Threshold Voltage                            | V <sub>3UV</sub>    | V <sub>3</sub> falling |         | 2.8  | _      | V                 |

| V3 Pin UVP Hysteresis                                   | V <sub>3UVHYS</sub> |                        |         | 175  | _      | mV                |

| HOCP Threshold Current <sup>(2)</sup>                   | I <sub>HOCP</sub>   |                        | 130     | 150  | 165    | % I <sub>FS</sub> |

| HOCP Threshold Voltage <sup>(2)</sup>                   | V <sub>TRIPH</sub>  |                        | 650     | 750  | 825    | mV                |

| HOCP Filtering Time <sup>(2)</sup>                      | t <sub>HOCPF</sub>  |                        | 0.75    | 1.00 | 1.25   | μs                |

| TSD Temperature (Gate-drive MIC)                        | T <sub>DHD</sub>    |                        | 120     | 130  |        | °C                |

| TSD Hysteresis Temperature<br>(Gate-drive MIC)          | T <sub>DHYSD</sub>  |                        |         | 40   |        | °C                |

| Thermal Warning Temperature<br>(Control MIC)            | T <sub>WHC</sub>    |                        | 125     | 135  | —      | °C                |

| Thermal Warning Temperature<br>Hysteresis (Control MIC) | T <sub>WHYS</sub>   |                        |         | 15   |        | °C                |

| TSD Temperature (Control MIC)                           | T <sub>DHC</sub>    |                        | 135     | 150  |        | °C                |

| TSD Temperature Hysteresis<br>(Control MIC)             | T <sub>DHCHYS</sub> |                        |         | 35   |        | °C                |

(2) Reference value

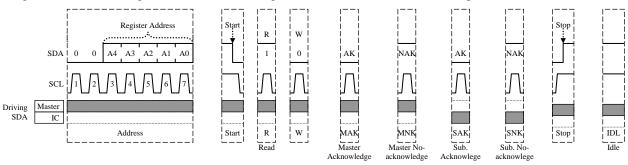

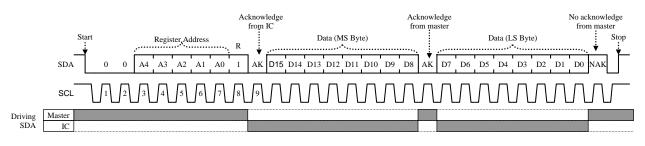

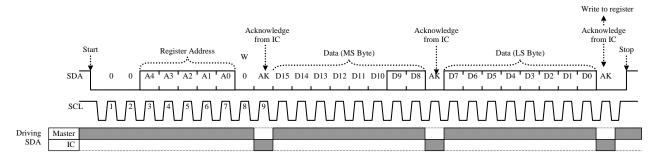

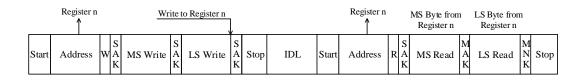

# **3.2.** Serial Communications

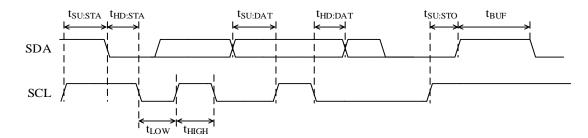

Figure 3-1. Serial Communications Timings

| Parameter                                              | Symbol              | Conditions                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------------|------|------|------|------|

| Glitch Suppression Filter <sup>(1)</sup>               | _                   |                                                                 |      |      | 50   | ns   |

| SCL Pin Clock Frequency                                | f <sub>CLK</sub>    |                                                                 | 0    |      | 400  | kHz  |

| Falling Time of Output                                 | t <sub>OF</sub>     | C = 400  pF,<br>V <sub>pull-up</sub> = 3 V to 3.3 V             |      |      | 250  | ns   |

| Stop-to-Start Bus-free Time                            | t <sub>BUF</sub>    |                                                                 | 1.3  |      |      | μs   |

| Start Condition Hold Time                              | t <sub>HD:STA</sub> |                                                                 | 0.6  |      |      | μs   |

| Start Condition Setting Time                           | t <sub>SU:STA</sub> |                                                                 | 0.6  |      |      | μs   |

| SCL Pin Low Level Time                                 | t <sub>LOW</sub>    |                                                                 | 1.3  |      |      | μs   |

| SCL Pin High Level Time                                | t <sub>HIGH</sub>   |                                                                 | 0.6  |      |      | μs   |

| Data Setup Time                                        | t <sub>su:DAT</sub> |                                                                 | 100  |      |      | ns   |

| Data Hold Time                                         | t <sub>HD:DAT</sub> |                                                                 | 0    |      | 900  | ns   |

| Stop Condition Setting Time                            | t <sub>SU:STO</sub> |                                                                 | 0.6  |      |      | μs   |

| SDA Pin Low Level Output Voltage                       | V <sub>OL</sub>     | $I_{OL} = 3 \text{ mA}$                                         |      |      | 0.45 | V    |

| SDA Pin Output Leakage Current                         | Io                  | $V_0 = 0 V \text{ to } 5.5 V,$<br>$V_3 = 0 V \text{ to } 3.3 V$ | -2.5 |      | 2.5  | μΑ   |

| SDA or SCL Pin Low Level Input<br>Voltage              | V <sub>IL</sub>     |                                                                 |      |      | 0.76 | V    |

| SDA or SCL Pin High Level Input Voltage <sup>(2)</sup> | $V_{\mathrm{IH}}$   |                                                                 | 2.04 |      |      | V    |

| SCL Pin Input Pull-up Resistor <sup>(2)</sup>          | $R_{PU\_S}$         |                                                                 | 45   | 90   | 105  | kΩ   |

<sup>(1)</sup> Refers to a pulse width for suppressing spike noise.

<sup>(2)</sup> When applying an external voltage, be sure to set the SDA and SCL pins to logic low during IC startup (i.e., until the V3 pin voltage is established).

## **3.3.** Transistor Characteristics

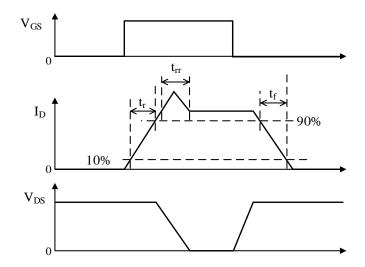

Figure 3-2 provides the definitions of switching characteristics described in this and the following sections.  $V_{GS}$  represents the voltage between the gate and source of an internal power MOSFET.

Figure 3-2. Switching Characteristics Definitions

# 3.3.1. SX68201M

| Parameter                                       | Symbol              | Conditions                                                                                           | Min. | Тур. | Max. | Unit |  |  |

|-------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| Drain-to-Source Leakage Current                 | I <sub>DSS</sub>    | $V_{DS} = 250 \text{ V}$                                                                             |      |      | 100  | μΑ   |  |  |

| Drain-to-Source On-resistance                   | R <sub>DS(ON)</sub> | $I_D = 1 A$                                                                                          |      | 1.25 | 1.5  | Ω    |  |  |

| Source-to-Drain Diode Forward<br>Voltage        | V <sub>SD</sub>     | $I_{SD} = 1 A$                                                                                       |      | 1.1  | 1.5  | V    |  |  |

| High-side Switching                             | High-side Switching |                                                                                                      |      |      |      |      |  |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $V_{DC} = 150 \text{ V},$                                                                            |      | 75   |      | ns   |  |  |

| Rise Time*                                      | t <sub>r</sub>      | $V_{CC} = 15 \text{ V},$<br>$I_D = 1.0 \text{ A}, T_J = 25 \text{ °C},$                              |      | 45   |      | ns   |  |  |

| Fall Time*                                      | t <sub>f</sub>      | inductive load                                                                                       |      | 40   |      | ns   |  |  |

| Low-side Switching                              |                     |                                                                                                      |      |      |      |      |  |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $V_{DC} = 150 \text{ V},$<br>$V_{CC} = 15 \text{ V},$<br>$I_D = 1.0 \text{ A}, T_J = 25 \text{ °C},$ |      | 70   |      | ns   |  |  |

| Rise Time*                                      | t <sub>r</sub>      |                                                                                                      |      | 50   |      | ns   |  |  |

| Fall Time*                                      | t <sub>f</sub>      | inductive load                                                                                       |      | 20   |      | ns   |  |  |

\* Guaranteed by design.

# 3.3.2. SX68204M

| Parameter                                       | Symbol              | Conditions                                                                                                                                         | Min. | Тур. | Max. | Unit |  |

|-------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| Drain-to-Source Leakage Current                 | I <sub>DSS</sub>    | $V_{DS} = 600 \text{ V}$                                                                                                                           |      |      | 100  | μΑ   |  |

| Drain-to-Source On-resistance                   | R <sub>DS(ON)</sub> | $I_D=0.75\ A$                                                                                                                                      |      | 2.9  | 3.6  | Ω    |  |

| Source-to-Drain Diode Forward<br>Voltage        | V <sub>SD</sub>     | $I_{SD}=0.75\ A$                                                                                                                                   |      | 0.95 | 1.5  | V    |  |

| High-side Switching                             |                     |                                                                                                                                                    |      |      |      |      |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $V_{DC} = 300 V,$                                                                                                                                  |      | 125  | _    | ns   |  |

| Rise Time*                                      | tr                  | $V_{CC} = 15 \text{ V},$<br>$I_D = 0.75 \text{ A}, T_J = 25 \text{ °C},$                                                                           |      | 60   | _    | ns   |  |

| Fall Time*                                      | t <sub>f</sub>      | inductive load                                                                                                                                     |      | 25   |      | ns   |  |

| Low-side Switching                              |                     |                                                                                                                                                    |      |      |      |      |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $\label{eq:VDC} \begin{array}{l} V_{DC} = 300 \ V, \\ V_{CC} = 15 \ V, \\ I_D = 0.75 \ A, \ T_J = 25 \ ^{\circ}C, \\ inductive \ load \end{array}$ |      | 130  | _    | ns   |  |

| Rise Time*                                      | tr                  |                                                                                                                                                    |      | 65   |      | ns   |  |

| Fall Time*                                      | t <sub>f</sub>      |                                                                                                                                                    |      | 30   |      | ns   |  |

# 3.3.3. SX68205M

| Parameter                                       | Symbol              | Conditions                                                                                           | Min. | Тур. | Max. | Unit |  |

|-------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| Drain-to-Source Leakage Current                 | I <sub>DSS</sub>    | $V_{DS} = 600 \text{ V}$                                                                             | —    |      | 100  | μΑ   |  |

| Drain-to-Source On-resistance                   | R <sub>DS(ON)</sub> | $I_D = 1 A$                                                                                          | —    | 2.0  | 2.5  | Ω    |  |

| Source-to-Drain Diode Forward<br>Voltage        | V <sub>SD</sub>     | $I_{SD} = 1 A$                                                                                       |      | 1.1  | 1.6  | V    |  |

| High-side Switching                             |                     |                                                                                                      |      |      |      |      |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $V_{DC} = 300 V,$                                                                                    |      | 115  | _    | ns   |  |

| Rise Time*                                      | t <sub>r</sub>      | $V_{CC} = 15 \text{ V},$<br>$I_D = 1.0 \text{ A}, T_J = 25 ^{\circ}\text{C},$                        |      | 50   | _    | ns   |  |

| Fall Time*                                      | t <sub>f</sub>      | inductive load                                                                                       |      | 45   | _    | ns   |  |

| Low-side Switching                              |                     |                                                                                                      |      |      |      |      |  |

| Source-to-Drain Diode Reverse<br>Recovery Time* | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$<br>$V_{CC} = 15 \text{ V},$<br>$I_D = 1.0 \text{ A}, T_J = 25 \text{ °C},$ |      | 115  |      | ns   |  |

| Rise Time*                                      | t <sub>r</sub>      |                                                                                                      | —    | 55   |      | ns   |  |

| Fall Time*                                      | t <sub>f</sub>      | inductive load                                                                                       |      | 40   |      | ns   |  |

| <b>3.4. Bootstrap Diode Characteristics</b> |  |

|---------------------------------------------|--|

|---------------------------------------------|--|

| Parameter                       | Symbol            | Conditions       | Min. | Тур. | Max. | Unit |

|---------------------------------|-------------------|------------------|------|------|------|------|

| Bootstrap Diode Forward Voltage | $V_{FB}$          | $I_{FB}=0.15\ A$ |      | 1.0  | 1.3  | V    |

| Bootstrap Diode Series Resistor | R <sub>BOOT</sub> |                  | 45   | 60   | 75   | Ω    |

# 3.5. Thermal Resistance Characteristics

| Parameter                                             | Symbol           | Conditions                                           | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|------------------|------------------------------------------------------|------|------|------|------|

| Junction-to-Case Thermal<br>Resistance <sup>(2)</sup> | R <sub>J-C</sub> | All power MOSFETs                                    |      |      | 10   | °C/W |

| Junction-to-Ambient Thermal<br>Resistance             | $R_{J-A}$        | operating; when mounted<br>on a board <sup>(3)</sup> |      |      | 35   | °C/W |

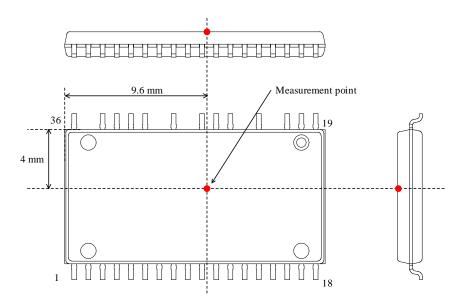

<sup>(2)</sup> Refers to a case temperature at the measurement point described in Figure 3-3.

$^{(3)}$  Refers to a 1.6 mm thick CEM3 glass with 35  $\mu$ m thick copper foil; measured under natural air cooling without silicone potting.

Figure 3-3. Case Temperature Measurement Point

## 4. Mechanical Characteristics

| Parameter      | Conditions | Min. | Тур. | Max. | Unit |

|----------------|------------|------|------|------|------|

| Package Weight |            |      | 1.4  |      | g    |

# 5. Reference Register Value

The table below lists the reference values to be written to the registers. All the values in parentheses are expressed in hexadecimal. The values listed in the table below are only the parameters that the GUI initially displays.

|                   | 15 | 14 | 13 | 12 | 11 | 10 | 9           | 8           | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------------|----|----|----|----|----|----|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Config 0          |    |    |    |    |    |    | CR1         | CR0         | PR7         | PR6         | PR5         | PR4         | PR3         | PR2         | PR1         | PR0         |

| Ref. Value (0047) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 1           | 1           | 1           |

| Config 1          |    |    |    |    |    |    | DT5         | DT4         | DT3         | DT2         | DT1         | DT0         | OHT3        | OHT2        | OHT1        | OHT0        |

| Ref. Value (01E9) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 1           | 1           | 1           | 1           | 0           | 1           | 0           | 0           | 1           |

| Config 2          |    |    |    |    |    |    | CMS1        | CMS0        | RSN1        | RSN0        | OCF1        | OCF0        | CD3         | CD2         | CD1         | CD0         |

| Ref. Value (0363) | 0  | 0  | 0  | 0  | 0  | 0  | 1           | 1           | 0           | 1           | 1           | 0           | 0           | 0           | 1           | 1           |

| Config 3          |    |    |    |    |    |    | MO3         | MO2         | MO1         | MO0         | BCG2        | BCG1        | BCG0        | IWM1        | IWM0        | IHO         |

| Ref. Value (0160) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 1           | 0           | 1           | 1           | 0           | 0           | 0           | 0           | 0           |

| Config 4          |    |    |    |    |    |    | HT5         | HT4         | HT3         | HT2         | HT1         | HT0         | HD3         | HD2         | HD1         | HD0         |

| Ref. Value (0054) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 1           | 0           | 1           | 0           | 1           | 0           | 0           |

| Config 5          |    |    |    |    |    |    | STS4        | STS3        | STS2        | STS1        | STS0        | STD4        | STD3        | STD2        | STD1        | STD0        |

| Ref. Value (0104) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           |

| Config 6          |    |    |    |    |    |    | LS5         | LS4         | LS3         | LS2         | LS1         | LS0         | HS3         | HS2         | HS1         | HS0         |

| Ref. Value (0005) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 1           |

| Config 7          |    |    |    |    |    |    | IM4         | IM3         | IM2         | IM1         | IM0         | IO4         | IO3         | 102         | IO0         | IO0         |

| Ref. Value (00D5) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 1           | 1           | 0           | 1           | 0           | 1           | 0           | 1           |

| Config 8          |    |    |    |    |    |    | UVS         | HR3         | HR2         | HR1         | HR0         | FGS         | SI3         | SI2         | SI1         | SI0         |

| Ref. Value (0106) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 0           |

| Config 9          |    |    |    |    |    |    |             | CP3         | CP2         | CP1         | CP0         | ETR         | CI3         | CI2         | CI1         | CI0         |

| Ref. Value (00C6) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 1           | 1           | 0           | 0           | 0           | 1           | 1           | 0           |

| Config 10         |    |    |    |    |    |    |             | TP3         | TP2         | TP1         | TP0         |             | TI3         | TI2         | TI1         | TI0         |

| Ref. Value (00C6) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 1           | 1           | 0           | 0           | 0           | 1           | 1           | 0           |

| Config 11         |    |    |    |    |    |    | PWD9        | PWD8        | PWD7        | PWD6        | PWD5        | PWD4        | PWD3        | PWD2        | PWD1        | PWD0        |

| Ref. Value (0000) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| Config 12         |    |    |    |    |    |    | LW9         | LW8         | LW7         | LW6         | LW5         | LW4         | LW3         | LW2         | LW1         | LW0         |

| Ref. Value (00C8) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 1           | 1           | 0           | 0           | 1           | 0           | 0           | 0           |

| Config 13         |    |    |    |    |    |    | XWM1        | XWM0        | LHT1        | LHT0        | FW5         | FW4         | FW3         | FW2         | FW1         | FW0         |

| Ref. Value (000D) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 0           | 1           |

| Config 14         |    |    |    |    |    |    | DTC         | VMC         | DG3         | DG2         | DG1         | DG0         | DM3         | DM2         | DM1         | DM0         |

| Ref. Value (0100) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| Config 15         |    |    |    |    |    |    | SCS         |             | PN3         | PN2         | PN1         | PN0         | SU3         | SU2         | SU1         | SU0         |

| Ref. Value (0209) | 0  | 0  | 0  | 0  | 0  | 0  | 1           | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 1           |

| Config 16         |    |    |    |    |    |    | SR9<br>SRH9 | SR8<br>SRH8 | SR7<br>SRH7 | SR6<br>SRH6 | SR5<br>SRH5 | SR4<br>SRH4 | SR3<br>SRH3 | SR2<br>SRH2 | SR1<br>SRH1 | SR0<br>SRH0 |

| Ref. Value (001E) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 1           | 1           | 0           |

| Config 17         |    |    |    |    |    |    | SRL9        | SRL8        | SRL7        | SRL6        | SRL5        | SRL4        | SRL3        | SRL2        | SRL1        | SRL0        |

| Ref. Value (0000) | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

SX68200M-DSE Rev.2.1 S/ May 19, 2023 ht © SANKEN ELECTRIC CO., LTD. 2019

|                                     |    |     | 1  |    |    |    |       |       |      |      |      |       |       |       |      |      |

|-------------------------------------|----|-----|----|----|----|----|-------|-------|------|------|------|-------|-------|-------|------|------|

|                                     | 15 | 14  | 13 | 12 | 11 | 10 | 9     | 8     | 7    | 6    | 5    | 4     | 3     | 2     | 1    | 0    |

| Config 18                           |    |     |    |    |    |    | VX9   | VX8   | VX7  | VX6  | VX5  | VX4   | VX3   | VX2   | VX1  | VX0  |

| Ref. Value (0366)                   | 0  | 0   | 0  | 0  | 0  | 0  | 1     | 1     | 0    | 1    | 1    | 0     | 0     | 1     | 1    | 0    |

| Config 19                           |    |     |    |    |    |    | VS9   | VS8   | VS7  | VS6  | VS5  | VS4   | VS3   | VS2   | VS1  | VS0  |

| Ref. Value (01B3)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 1     | 1    | 0    | 1    | 1     | 0     | 0     | 1    | 1    |

| Config 20                           |    |     |    |    |    |    | VN9   | VN8   | VN7  | VN6  | VN5  | VN4   | VN3   | VN2   | VN10 | VN0  |

| Ref. Value (015C)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 1     | 0    | 1    | 0    | 1     | 1     | 1     | 0    | 0    |

| Config 21                           |    |     |    |    |    |    | VC9   | VC8   | VC7  | VC6  | VC5  | VC4   | VC3   | VC2   | VC11 | VC0  |

| Ref. Value (00AE)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 0     | 1    | 0    | 1    | 0     | 1     | 1     | 1    | 0    |

| Register 28 Write<br>EEPROM Control | 0  | 0   | 0  | 0  | 0  | 0  | SAV   | 0     | 0    | 0    | 0    | 0     | 0     | 0     | 0    | 0    |

| Register 28 Read<br>EEPROM Count    | 0  | 0   | 0  | 0  | 0  | 0  | NVC9  | NVC8  | NVC7 | NVC6 | NVC5 | NVC4  | NVC3  | NVC2  | NVC1 | NVC0 |

| Register 29<br>Fault Mask           |    |     |    |    |    |    | TW    | ОТ    | LOS  | PMF  | HOC  | OVM   | UVM   |       |      |      |

| Ref. Value (0000)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     | 0    | 0    |

| Register 30 Write                   |    |     |    |    |    |    |       |       |      |      |      | DIAG4 | DIAG3 | DIAG2 |      |      |

| Ref. Value (0000)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 0     | 0    | 0    | 0    | 0     | 0     | 0     | 0    | 0    |

| Register 30 Read<br>Diagnostic      | FF | POR | ME | WD | OC | EE | TW    | ОТ    | LOS  | PMF  | НОС  | OVM   | UVM   | 0     | 0    |      |

| Register 31 Run                     |    |     |    |    |    |    | DIAG1 | DIAG0 | RDG  | PMR  | STM  | ESF   | RSC   | BRK   | DIR  | RUN  |

| Ref. Value (0092)                   | 0  | 0   | 0  | 0  | 0  | 0  | 0     | 0     | 1    | 0    | 0    | 1     | 0     | 0     | 1    | 0    |

| Register Read                       | FF | POR | ME | WD | OC | EE |       |       |      |      |      |       |       |       |      |      |

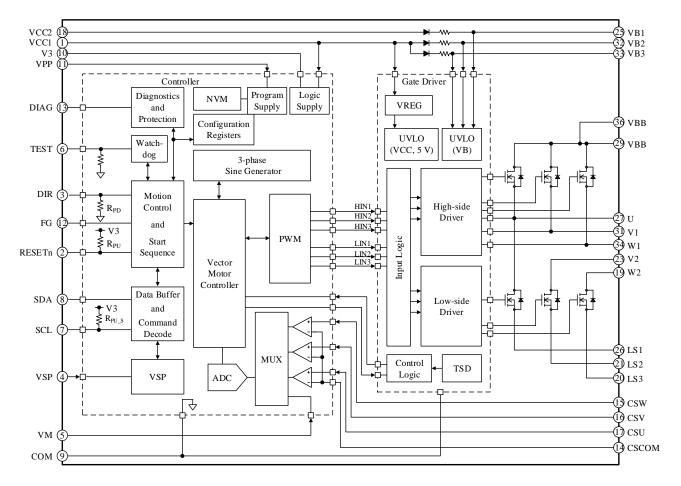

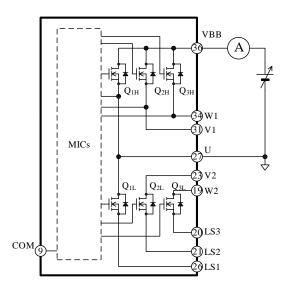

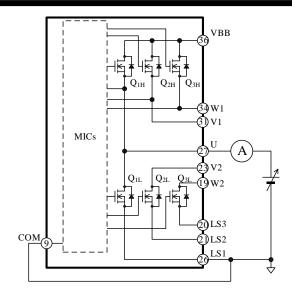

# 6. Block Diagram

# 7. Pin Configuration Definitions

|     | Top View |      |    | Pin    | Pin          | Description                                     |

|-----|----------|------|----|--------|--------------|-------------------------------------------------|

| 1   | VCC1     | VBB  | 36 | Number | Name<br>VCC1 | -                                               |

| 2   | RESETn   |      | 35 | 1      |              | Logic supply voltage input 1                    |

| 3   | DIR      | W1   | 33 | 2      | RESETn       | Reset signal input                              |

|     |          |      |    | 3      | DIR          | Motor direction setting signal input            |

| 4   | VSP      | VB3  | 33 | 4      | VSP          | Motor speed control signal input                |

| 5   | VM       | VB2  | 32 | 5      | VM           | Main supply voltage detection signal input      |

| 6   | TEST     | V1   | 31 | 6      | TEST         | Test input                                      |

| 7   | SCL      |      | 30 | 7      | SCL          | Serial clock input                              |

| 8   | SDA      | VBB  | 29 | 8      | SDA          | Serial data input                               |

| 9 🕅 | СОМ      |      | 28 | 9      | COM          | Logic ground                                    |

| 10  | V3       | U    | 27 | 10     | V3           | Internal regulator ( i.e., V3 regulator) output |

| 11  | VPP      | LS1  | 26 | 11     | VPP          | EEPROM write supply voltage input               |

| 12  | FG       | VB1  | 25 | 12     | FG           | Motor rotation pulse output                     |

| 13  | DIAG     | , 21 | 24 | 13     | DIAG         | Fault signal output                             |

|     | _        | W2   |    | 14     | CSCOM        | Current detection reference voltage input       |

| 14  | CSCOM    | V2   | 23 | 15     | CSW          | W-phase current detection signal input          |

| 15  | CSW      |      | 22 | 16     | CSV          | V-phase current detection signal input          |

| 16  | CSV      | LS2  | 21 | 17     | CSU          | U-phase current detection signal input          |

| 17  | CSU      | LS3  | 20 | 18     | VCC2         | Logic supply voltage input 2                    |

| 18  | VCC2     | W2   | 19 | 19     | W2           | W-phase output (connected to W1 externally)     |

|     |          |      |    | 20     | LS3          | W-phase low-side power MOSFET source            |

|     |          |      |    | 21     | LS2          | V-phase low-side power MOSFET source            |

|     |          |      |    | 22     |              | Pin removed                                     |

|     |          |      |    | 23     | V2           | V-phase output (connected to V1 externally)     |

|     |          |      |    | 24     | _            | Pin removed                                     |

|     |          |      |    | 25     | VB1          | U-phase high-side floating supply voltage input |

|     |          |      |    | 26     | LS1          | U-phase low-side power MOSFET source            |

|     |          |      |    | 27     | U            | U-phase output                                  |

|     |          |      |    | 28     |              | Pin removed                                     |

|     |          |      |    | 29     | VBB          | Positive DC bus supply voltage                  |

|     |          |      |    | 30     |              | Pin removed                                     |

|     |          |      |    | 31     | V1           | V-phase output (connected to V2 externally)     |

|     |          |      |    | 32     | VB2          | V-phase high-side floating supply voltage input |

|     |          |      |    | 33     | VB3          | W-phase high-side floating supply voltage input |

|     |          |      |    | 34     | W1           | W-phase output (connected to W2 externally)     |

|     |          |      |    | 35     |              | Pin removed                                     |

|     |          |      |    | 36     | VBB          | Positive DC bus supply voltage                  |

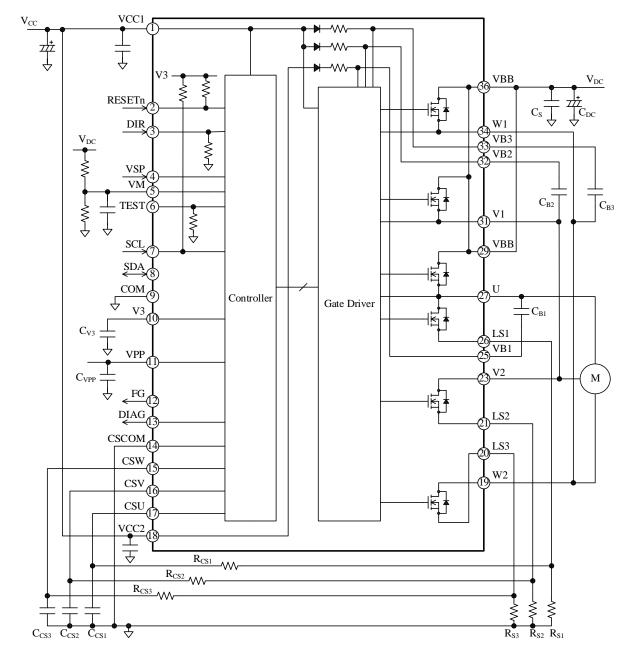

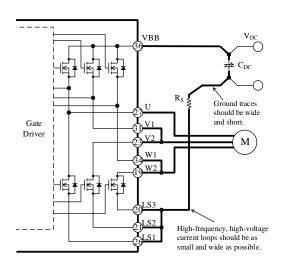

# 8. Typical Application

Figure 8-1. Typical Application

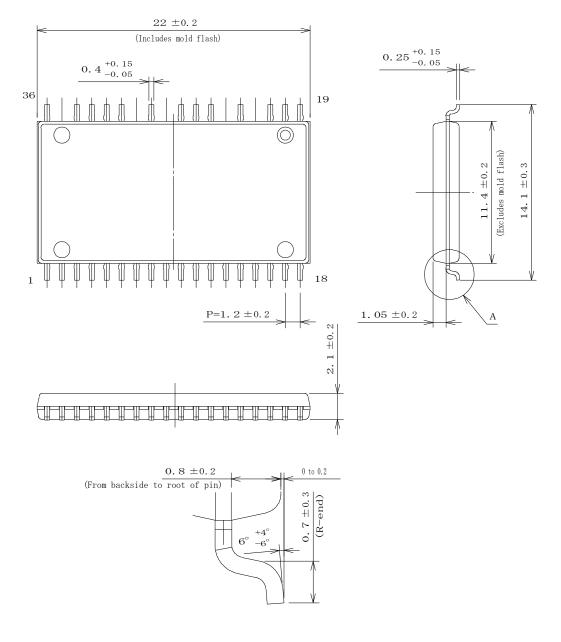

# 9. Physical Dimensions

# • SOP36 Package

Enlarged view of A (S = 20/1)

## NOTES:

- Dimensions in millimeters

- Pb-free (RoHS compliant)

- When soldering the products, it is required to minimize the working time within the following limits: Reflow (MSL3):

Preheating: 180 °C / 90  $\pm$  30 s Solder heating: 250 °C / 10  $\pm$  1 s (260 °C peak, 2 times) Soldering iron: 380  $\pm$  10 °C / 3.5  $\pm$  0.5 s, 1 time

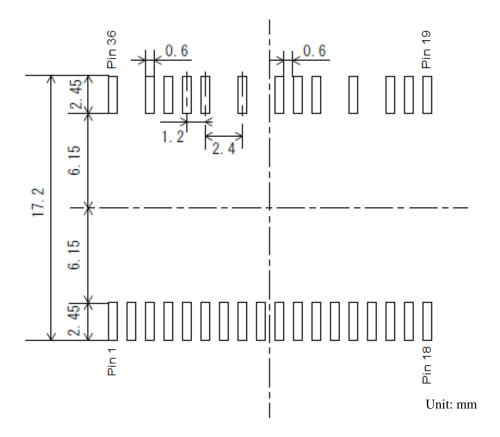

## • Land Pattern Example

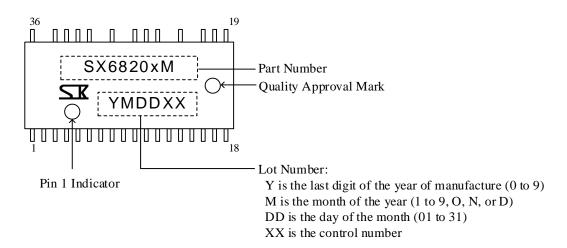

# 10. Marking Diagram

## **11. Functional Descriptions**

Unless specifically noted, this section uses the following definitions:

- All the characteristic values given in this section are typical values.

- For pin and peripheral component descriptions, this section employs a notation system that denotes a pin name with the arbitrary letter "x", depending on context. Thus, "the VCCx pin" is used when referring to either or both of the VCC1 and VCC2 pins.

## **11.1. Basic Operation**

The IC is a 3-phase brushless motor driver operated with sinusoidal current waveforms, where the rotor position is estimated by a sensorless vector control strategy. The rotor positioning system is based on calculations from the voltages applied to the 3-phase motor and the currents through each phase, thus requiring no external position sensor. The internal power MOSFETs consisting of 3-phase bridges supply the currents to the motor. The serial communications feature provides reliable access to the extensive collection of settings pertaining to control systems and diagnostic features. The IC integrates a non-volatile memory (EEPROM), which stores register data, to operate independently of external communications.

The IC has the motor speed control system whose reference speed settings are programmable through the serial communications or by an analog voltage input. In an overcurrent condition, the IC puts a certain limit on the motor current level with its protection function.

The startup operation uses the parameters settable via the serial communications, thus permitting the IC to support a wide range of the combinations of motors and loads. Moreover, the built-in watchdog timer allows the IC to stop the present motor run as the protection against chip-level damage, e.g., a control part in a freeze state.

The fault detection and diagnosis on operational faults such as the VCCx or V3 pin undervoltage protection, thermal shutdown, and so on are carried out based on the detailed diagnostic information accessible through the serial communications. The DIAG pin operates as the fault signal output, whose settings are also programmable by the diagnostic register.

For thorough functional descriptions, see the following sections.

## **11.2.** Pin Descriptions

## 11.2.1. VCC1 and VCC2

These are the logic supply pins for the built-in control ICs. The VCCx pin voltage is used for charging

bootstrap capacitors. In addition, the VCCx pin voltage is internally stepped down (i.e., V3 regulator) to be used as a logic power supply. A 26 V Zener diode is internally connected between the VCCx and COM pins.

The VCC1 and VCC2 pins must be externally connected on a PCB because they are not internally connected. To prevent malfunction induced by supply ripples or other factors, put a capacitor of about 0.01  $\mu$ F to 0.22  $\mu$ F, C<sub>VCC</sub>, near these pins. Voltages to be applied between the VCCx and COM pins should be about 15 V.

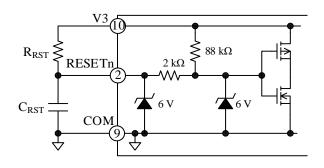

## 11.2.2. RESETn

This pin operates to reset the diagnostic register. When the RESETn pin becomes logic low, the motor operation stops, and the diagnostic register is cleared. Then, the DIAG pin is reset to logic high.

The RESETn pin is internally pulled up to the V3 regulator by the resistor. The RESETn pin should be normally left open.

If any noise-induced malfunction occurs, add  $R_{RST}$  and  $C_{RST}$  as shown in Figure 11-1. When turning on the IC, be sure to check that the RESETn pin is held at logic low. In particular, when applying an external voltage on the RESETn pin, be sure to set the RESETn pin to logic low until the V3 pin voltage is established.

Figure 11-1. Internal Circuit Diagram of RESETn Pin

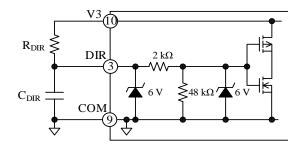

#### 11.2.3. DIR

This is the signal input pin to switch the direction of motor rotation. The motor direction is determined by the logical EXOR (exclusive OR) of the DIR bit in the internal register and the DIR logic input, as in Table 11-1.

Table 11-1.

Logic Levels Defined for Motor Direction

| DIR Bit | DIR Pin | Motor Direction |

|---------|---------|-----------------|

| 0       | L       | Forward         |

| 0       | Н       | Reverse         |

| 1       | L       | Reverse         |

| 1       | Н       | Forward         |

The DIR pin is internally pulled down to the COM pin with the internal resistor. To set the DIR pin to logic low, normally leave the pin open. If any noise-induced malfunction occurs, connect the DIR pin to the COM pin.

To set the DIR pin to logic high, pull up the pin to the V3 pin with  $R_{DIR}$ , as shown in Figure 11-2. If any noise-induced malfunction occurs, add  $C_{DIR}$  between the DIR and COM pins.

When turning on the IC, be sure to check that the DIR pin is held at logic low. In particular, when applying an external voltage on the DIR pin, be sure to set the DIR pin to logic low until the V3 pin voltage is established. Note that the motor operation must be stopped for switching the logic level of input signals to the DIR pin.

Figure 11-2. Internal Circuit Diagram of DIR Pin

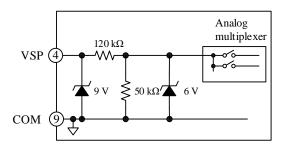

## 11.2.4. VSP

This is the input pin of reference voltage to set the speed of motor rotation. Figure 11-3 shows an internal circuit diagram of the VSP pin.

The reference voltage is input between the VSP and COM pins. When the VSP pin is held at logic low for a certain period of time, the IC enters the low power consumption mode.

Figure 11-3. Internal Circuit Diagram of VSP Pin

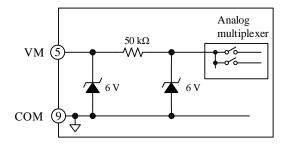

## 11.2.5. VM

This pin monitors the motor driving voltage,  $V_{DC}$ .  $V_{DC}$  divided by a resistive voltage divider is applied to the VM pin. Figure 11-4 illustrates an internal circuit diagram of the VM pin.

The resistor should be set within the range specified

as the absolute maximum rating (-0.3 V to 4 V). The VM pin also has the overvoltage protection and the undervoltage lockout. For more details, see Section 11.15.4.

Figure 11-4. Internal Circuit Diagram of VM Pin

#### 11.2.6. TEST

This is the input pin designed for test use only, not for motor control. When using the TEST pin in your application, leave the pin open or connect a resistor of about 10 k $\Omega$  between the pin and the ground (COM).

If you have any questions about using the TEST pin, please contact our sales representative or distributor.

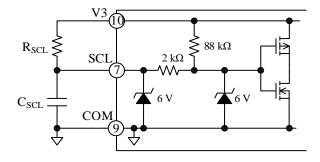

## 11.2.7. SCL

This pin operates as the clock input pin for the serial communications. Figure 11-5 is an internal circuit diagram describing the SCL pin.

While the serial communications are being performed, the power supply (3.3 V to 5.0 V) of the master device must be used. Care must be taken in supplying power to the subordinate and master devices. Be sure to turn on the IC (subordinate) first, and then turn on the master device. The SCL pin should be normally left open.

If any noise-induced malfunction occurs, add  $R_{SCL}$  and  $C_{SCL}$  as shown in Figure 11-5.

When turning on the IC, be sure to check that the SCL pin is held at logic low.

Figure 11-5. Internal Circuit Diagram of SCL Pin

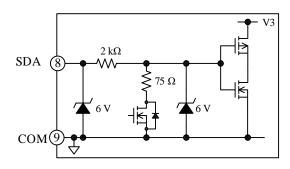

#### 11.2.8. SDA

This is the data input/output pin for the serial communications. Figure 11-6 is an internal circuit diagram describing the SDA pin.

While the serial communications are being performed, the power supply (3.3 V to 5.0 V) of the master device must be used. Care must be taken in supplying power to the subordinate and master devices. Be sure to turn on the IC (subordinate) first, and then turn on the master device. When turning on the IC, be sure to check that the SDA pin is held at logic low.

The SDA pin should be normally left open. If any noise-induced malfunction occurs, connect a resistor of about 10 k $\Omega$  between the SDA and COM pins.

Figure 11-6. Internal Circuit Diagram of SDA Pin

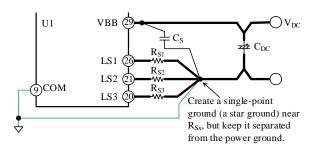

## 11.2.9. COM

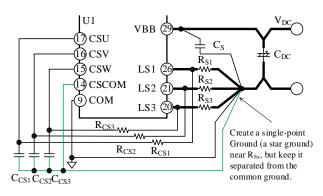

This is the logic ground pin for the built-in control ICs. Varying electric potential of the logic ground can be a cause of improper operations. Therefore, connect the logic ground as close and short as possible to shunt resistors,  $R_{Sx}$ , at a single-point ground (or star ground) which is separated from the power ground (see Figure 11-7).

Figure 11-7. Connections to Logic Ground

# 11.2.10. V3

This pin is the output of the 3.3 V internal regulator. A 6 V Zener diode is internally connected to the V3 pin. Connect a capacitor of about 1.0  $\mu$ F ( $\geq$ 0.47  $\mu$ F) between the V3 and COM pins.

## 11.2.11. VPP

This pin is the input of the programming voltage supply. Writing to the EEPROM requires a programming voltage; therefore, connect a capacitor,  $C_{VPP}$ , of about 0.1 µF and apply a voltage of 24 V to it. The IC uses the VPP pin voltage smoothed by the internal regulator. A 30 V Zener diode is internally connected to the VPP pin. When not using the VPP pin, connect the pin to the VCCx or COM pin (no  $C_{VPP}$  required).

#### 11.2.12. FG

While internal signals of the IC and the motor rotation synchronizes, the FG pin outputs pulses proportionally to a preset motor electrical cycle frequency. The pulse frequency of the FG pin output is set  $\times 1$  or  $\times 3$  of the motor electrical cycle frequency by the FGS bit in the configuration register 8 (Config 8). Figure 11-8 shows an internal circuit diagram of the FG pin

Figure 11-8. Internal Circuit Diagram of FG Pin

## 11.2.13. DIAG

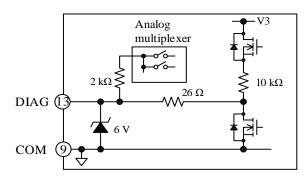

The DIAG pin outputs fault signals. Figure 11-9 is an internal circuit diagram illustrating the DIAG pin. For more details, see Section 11.14.1.

Figure 11-9. Internal Circuit Diagram of DIAG Pin

SX68200M-DSE Rev.2.1

SAN

May 19, 2023

https

© SANKEN ELECTRIC CO., LTD. 2019

#### 11.2.14. CSCOM

This pin serves as the reference input for current detection. Connect the CSCOM pin as close as possible to shunt resistors,  $R_{Sx}$ , whose traces are separated from the common ground.

Figure 11-10. Connections to CSCOM Pin

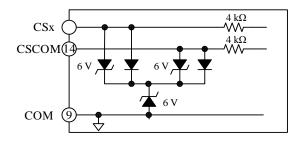

## 11.2.15. CSU, CSV, and CSW

This is the input pin of current detection signals. Figure 11-11 illustrates an internal circuit diagram of the CSx and CSCOM pins.

The CSU, CSV, and CSW pins are, directly but separately, connected to each current detection resistor of the U-, V-, and W-phases. To eliminate signal ringing which may be induced by parasitic capacitance and the impedance in the detection resistors, add an RC low pass filter (i.e.,  $R_{CSx}$  and  $C_{CSx}$  in Figure 11-10) as needed.

Figure 11-11. Internal Circuit of CSx and CSCOM Pins

## 11.2.16. VBB

This is the input pin for the main supply voltage, i.e., the positive DC bus. All of the power MOSFET drains of the high-side are connected to this pin. Voltages between the VBB pin and the ground (COM) should be set within the recommended range of the main supply voltage,  $V_{DC}$ , given in Section 2.

To suppress surge voltages, put a 0.01  $\mu$ F to 0.1  $\mu$ F bypass capacitor, C<sub>S</sub>, near the VBB pin and an electrolytic capacitor, C<sub>DC</sub>, with a minimal length of PCB traces to the VBB pin.

## 11.2.17. VB1, VB2, and VB3

The VB1, VB2, and VB3 pins are connected to bootstrap capacitors,  $C_{Bx}$ , for the high-side floating supply. For proper startup, turn on the low-side transistors first, then fully charge the bootstrap capacitors,  $C_{Bx}$ . Section 11.4 describes the startup sequences of the IC in detail; Section 11.12 explains the procedures to charge the bootstrap capacitors.

$C_{Bx}$  of about 1  $\mu$ F must be placed near the IC, and connected between the VBx and output (U, V1, W1) pins with a minimal length of traces.

## 11.2.18. U, V1, V2, W1, and W2

These pins are the outputs of the three phases, and serve as the connection terminals to the 3-phase motor. The V1 and W1 pins must be connected to the V2 and W2 pins on a PCB, respectively. The U, V, and W1 pins are the grounds for the VB1, VB2, and VB3 pins. The U, V1, and W1 pins are connected to the negative nodes of bootstrap capacitors,  $C_{Bx}$ . Since high voltages are applied to these output pins (U, V1, V2, W1, W2), it is required to take measures for insulating as follows:

- Keep enough distance between the output pins and low-voltage traces.

- Coat the output pins with insulating resin.

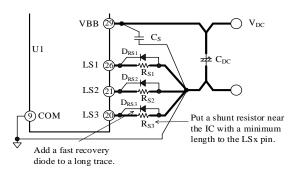

## 11.2.19. LS1, LS2, and LS3

The LS1, LS2, and LS3 pins are internally connected to the low-side power MOSFET sources of the U-, V-, and W-phases, respectively. For current detection, the LSx pin should be externally connected to shunt resistors,  $R_{Sx}$ . When connecting a shunt resistor, use a resistor with low inductance (required), and place it as near as possible to the IC with a minimum length of traces to the LSx and COM pins. Otherwise, malfunction may occur because a longer circuit trace increases its inductance and thus increases its susceptibility to improper operations. In applications where long PCB traces are required, add a fast recovery diode,  $D_{RSx}$ , between the LSx and COM pins in order to prevent the IC from malfunctioning (see Figure 11-12).

Figure 11-12. Connections to LSx Pin

## 11.3. Closed-loop Speed Control

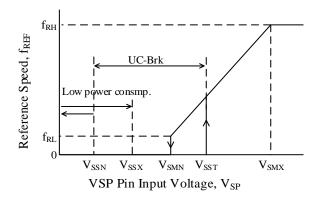

In addition to the vector control system, which is a core element in the control systems, the IC also incorporates a closed-loop speed control. The closed-loop speed control uses a preset reference speed as a target motor speed, determined by a frequency of the 3-phase waveforms (an electrical angle of  $360^{\circ}$ ). The reference speed, f<sub>REF</sub>, is input by either of the following two methods (for the motor speed setting, see Section 11.7):

- Directly inputting the relevant parameter via the serial communications

- Inputting the linear voltage that is proportional to the motor speed into the VSP pin

The reference speed,  $f_{REF}$ , and the feedback speed,  $f_{FBK}$ , are compared inside the IC to obtain a speed difference,  $f_{ERR}$ .  $f_{ERR}$  is then fed into the integrating controller to calculate a reference driving torque used for accelerating or decelerating the motor.

The following bits are for setting the speed control method, reference speed range, and the reference speed, respectively:

- Config 15 SCS Speed control method selection SU[3:0] Speed range multiplier

Config 16

- Config 16

SR[9:0] Reference motor speed

The integral gain,  $K_I$ , used for the speed control is can be adjusted to yield optimum performance by using the SI variable. The rotational inertia of motor load shaft and the desired mechanical response speed determine the SI variable. The following bit is for the SI variable setting:

• Config 8 SI[3:0] Integral gain constant, K<sub>I</sub>, for speed control

# 11.4. Startup

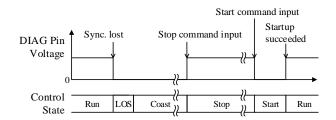

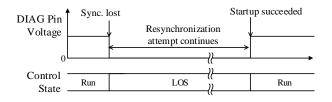

For proper startup, apply voltages to the main power supply of the motor, the VCC pin, and the VSP pin, in that order. The motor starts to operate with the startup sequence (defined below) depending on the VSP pin voltage levels.

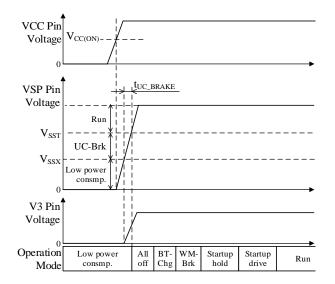

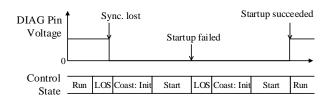

Figure 11-13 explains the startup sequence; Table 11-2 provides the operation modes definitions.

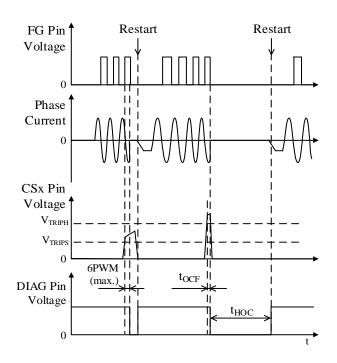

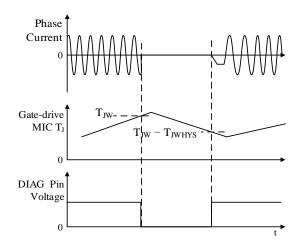

The IC has two startup modes: the DC alignment start mode and the ramp-up start mode. The STM bit in the Run register (Register 31) selects which mode to be enabled. Note that the motor may still be coasting or may be forced to rotate by the operation of a motor load before the startup. Therefore, either of the two startup modes requires the motor to be as stationary as possible in its very first stage. To apply a braking force to the stop the motor, the IC increases the duty cycle of a predetermined PWM period and turns on all the low-side power MOSFETs. During this braking operation, the IC monitors and limits the currents through the motor. The braking force maximizes at the duty cycle increased up to 100%. When the current detected reaches zero, the braking operation completes. The operations after the braking operation are as follows:

## • DC Alignment Start Mode

As soon as the braking period ends, the direct current of a preset value flows through the motor coil for a predefined hold time. The direct current increases from zero to a maximum value (i.e., the hold current) and remains in this condition for the hold time. This allows the rotor to be aligned to an initial position. In the DC alignment start mode, the hold time and hold current must be large enough to align the rotor to the initial position.

After the hold time ends, the motor rotates at a constant speed which is controlled with a PWM duty cycle generated by the closed-loop speed control system. The initial value of the PWM duty cycle must be set to generate an average voltage equal to the BEMF amplitude at the startup speed.

#### • Ramp-up Start Mode

The ramp-up start mode operation follows the braking period. During the period internally set to about 5 seconds, the excitation switching speed of phase currents gradually increases from 25% to 100% of the start speed (this is defined as a ramp-up period). During the rampup period, the rotor position is controlled without feedback. When the excitation switching speed reaches the maximum startup speed, the IC estimates a rotor position by its internal circuits.