# PSJGaN HEMT の開発

## Development of PSJGaN HEMT

伊藤 裕規\*

Hironori Ito

**概要** (株) パウデックの独自技術であるPSJGaN技術を用い、デバイス試作をおこなった。PSJGaNは、分極により生じる電子および正孔によって形成される超接合構造による電界分布の均一化を利用することで、耐圧の向上および、電流コラプスの抑制効果が期待される。これらの効果を確認するため、試作およびデバイス評価をおこない、従来のGaN HEMTと比較を行ったところ、耐圧および電流コラプス特性で優位性を示唆するデータが得られた。さらにカスコード接続によるSW動作では、SJMOSよりも優れた特性を示す結果が得られた。引き続き、MOSFETや制御ICと組み合わせた統合型デバイスの製品化へ向けて検討を進めていく。

### 1. まえがき

表1に示すようにGaNの材料特性は、広いバンドギャップ、高電子移動度、高絶縁破壊電界を有しており、従来のSiデバイスと比較して優れた電力密度とスイッチング性能を発揮するデバイスを作ることが可能である。近年、電力変換装置の高効率化および小型化に対する要求が高まる中、パワー半導体デバイスとしてGaN(窒化ガリウム)HEMT(High Electron Mobility Transistor)に注目が集まっている。

表1. 各半導体材料の物性

|                             | Si   | 4H-SiC | GaN  |

|-----------------------------|------|--------|------|

| バンドギャップ (eV)                | 1.12 | 3.26   | 3.39 |

| 電子移動度 (cm <sup>2</sup> /Vs) | 1350 | 700    | 1500 |

| 絶縁破壊電界 (MV/cm)              | 0.3  | 3.0    | 3.3  |

| バリガ指数                       | 1    | 439    | 1128 |

ただし、高耐圧かつ低オン抵抗という相反する特性の両立は大きな課題であり、デバイス構造の革新が求められている。こうした課題に対する新たなアプローチとして、当社は(株)パウデック(サンケン電気(株)に吸収合併)の独自技術である分極超接合(Polarization Super Junction, PSJ)構造を導入したGaN HEMT(PSJGaN)の

開発をおこなっている。PSJGaNは、GaN系材料に特有の分極効果を活用し、スーパージャンクション構造に類似した電界緩和を実現することで、低オン抵抗と高耐圧の両立を可能にする。さらに、支持基板にサファイアを用いることで、従来のシリコンを用いた場合(GaN on Si)に比べ、エピ厚削減によるコスト低減と、GaN on Siでは困難である1200V以上の超高耐圧デバイスの実現が可能となる。一方で、絶縁基板であるため、電流コラプス特性においては不利になる懸念がある。

本報告では、PSJGaNの設計、試作、評価を通じて、その性能と応用展望を明らかにし、実用化に向けた有効性を示す。

### 2. PSJGaNの構造と特徴

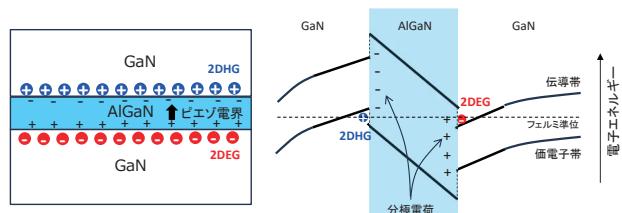

図1に示すようにGaN/AlGaN/GaN積層構造を形成すると、圧電分極により発生するAlGaN中の内部電界(ピエゾ電界)により、AlGaN上のGaN界面付近には正孔が、AlGaN下のGaN界面付近には電子が発生する。

\*技術開発本部プロセス技術統括部

GaNデバイス開発部 GaNデバイス開発課

図1. GaN/AlGaN/GaN構造とエネルギー-band図

発生した電子と正孔は平面状に広がることから二次元正孔ガス (two dimensional hall gas, 2DHG) と二次元電子ガス (two dimensional electron gas, 2DEG) と呼ばれ、AlGaN を介した分極超接合構造を形成している<sup>1)</sup>。

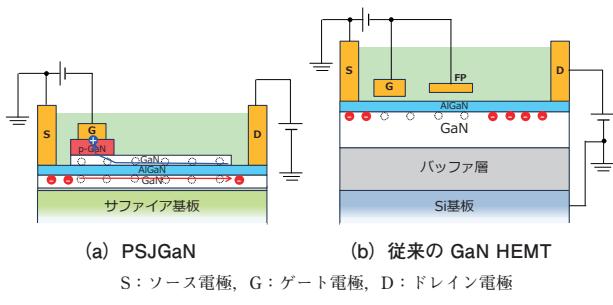

この2DEGは電荷密度が高く、かつ移動度も高いため、オン抵抗が低いデバイスを実現することができる。さらに、2DHGを利用し、PSJ構造をとることで高耐圧デバイスが実現できる。図2にオフ状態におけるデバイス構造を示す。図2(a)に示すようにPSJGaNはゲート電極に負バイアスを印加することにより、上部GaN領域の2DHGの正孔が引き抜かれ、それに伴い2DEGの電子が空乏化する。その結果、PSJ構造の領域(PSJ領域)全体で一様な電界分布を持ち、高耐圧にすることができる。ただし、2DHGによりゲート駆動させるため、オン時にはゲートに正のバイアスを印可する必要がある。

図2. オフ状態におけるキャリア分布イメージ

一方、図2(b)に示すように、従来のGaN HEMTはGaN on Siを用い、ゲート端への電界集中による耐圧低下をフィールドプレート(FP)を備えることで改善している。しかしながら、ドレイン電極とSi基板間に高電圧が生じることから、現状では800V以下の使用に限定されている。

また、GaN HEMTでは電流コラプスと呼ばれる、スイッチング動作中に電流が流れにくくなる現象があり、オン抵抗の増加を引き起こす。電流コラプスは、オフ時にゲート端部の電界集中により、AlGaN層や層間膜界面等に電子が捕獲され、仮想ゲートを作り出すことにより引き起こされる。対策としては、電界集中を緩和するためのFP構造を用いるなどの手法がとられている。一方、PSJGaNでは一様な電界分布が実現できることから、従来のGaN HEMTよりも電流コラプスの発生が抑制されることが期待される。

### 3. 試作評価結果

#### 3.1. 耐圧特性

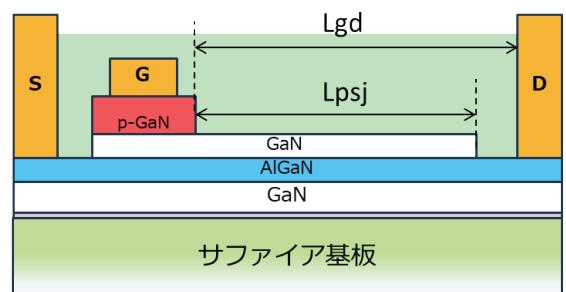

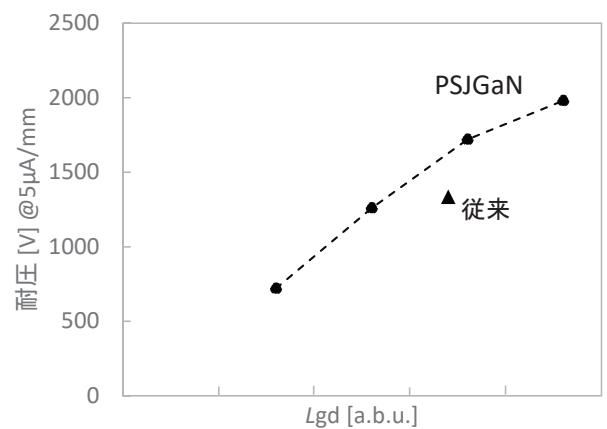

図3におけるPSJ構造の長さ( $L_{psj}$ )を変化させ、耐圧特性を評価した。 $L_{psj}$ が長くなるにつれ耐圧も大きくなる傾向が得られ、耐圧のGD間距離( $L_{gd}$ )依存性は図4となる。従来のGaN HEMTと比較すると、PSJGaNがより高耐圧を示しており、優位性を示唆する結果が得られた。

図3. PSJGaNの断面図

図4.  $L_{psj}$ を変化させたPSJGaNの耐圧特性

#### 3.2. 電流コラプス特性

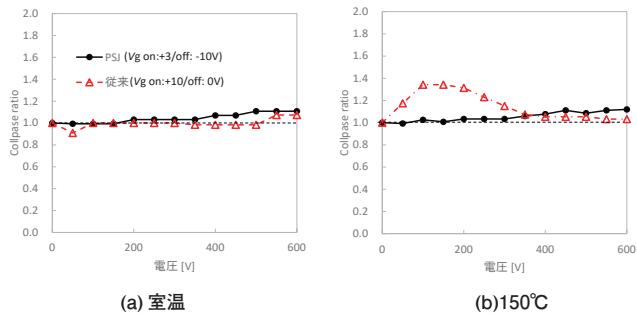

電流コラプス特性の定量評価には、パルスIV測定法を用いた。ゲート電圧をon/offの2値で切り替えるパルス信号を用い、ドレイン側には定電圧を印加した。パルス幅は25μsとし、オン後20μsのドレイン電流および電圧を測定し、電流コラプスを評価した。

評価指標としては、初期状態のオン抵抗 $R_0$ に対するパルス印加時のオン抵抗 $R_{on}$ (dynamic)の相対変化率を電流コラプス指標(collapse ratio)として定義した。この指標が1に近いほど電流コラプスが小さくなる。

$$\{\text{collapse ratio}\} = R_{on}(\text{dynamic}) / R_0$$

図 5. PSJGaN の電流コラプス特性

試作したPSJGaNおよび従来のGaN HEMTの電流コラプス特性を図5に示す。

従来のGaN HEMTと比較すると、サファイア基板を使用しているにもかかわらず、同等以上の電流コラプス特性が得られ、PSJ構造による効果が示された。

### 3.3. カスコード接続の動的特性

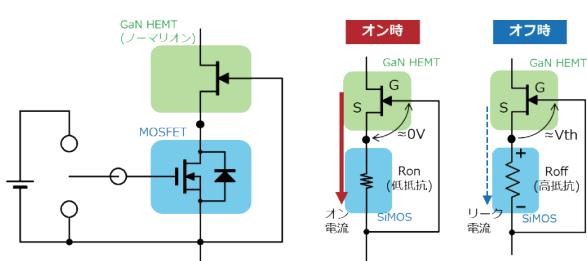

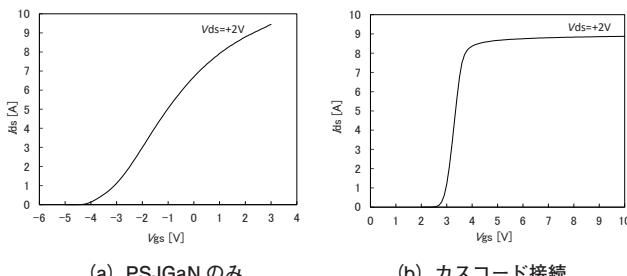

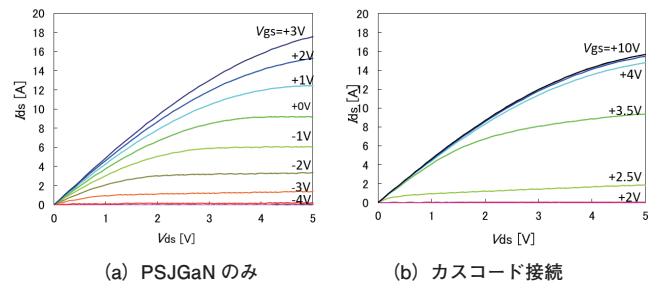

図6に示すように、ノーマリオン型のGaN HEMTとMOSFETを直列接続し、さらにGaN HEMTのゲートを接地（カスコード接続）することで、従来のノーマリオフデバイスと同等に扱うことができる。図7、図8にノーマリオン型のPSJGaNをカスコード接続（PSJGaNカスコード）した際に得られた特性を示す。

図 6. ノーマリオン型 GaN HEMT のカスコード接続

図 7. 伝達特性

図 8.  $I$ - $V$  特性

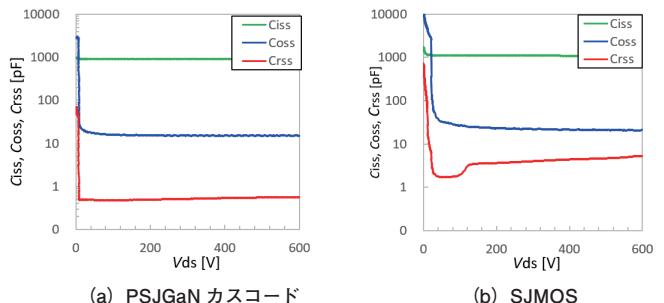

PSJGaNは、PSJ領域全体をゲート駆動するため、ゲート電荷量（ $Q_g$ ）が従来のGaN HEMTに比べ大きくなってしまう。しかし、カスコード接続にすることで、PSJGaNのゲートが接地されMOSFETを駆動することになるので、これによる容量特性やSW速度への悪影響は軽減されることが期待できる。図9にPSJGaNカスコードとスーパージャンクションMOSFET（SJMOS）の容量特性を示す。Coss, CrssにおいてSJMOSよりも優れた容量特性を示すことが確認できた。

図 9. 容量特性

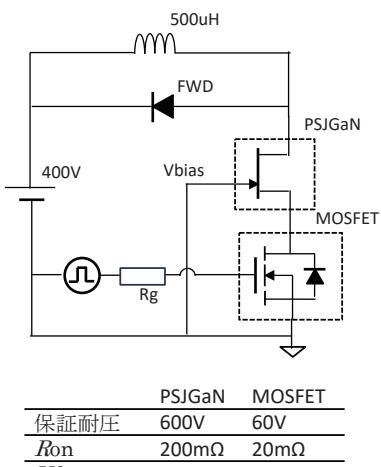

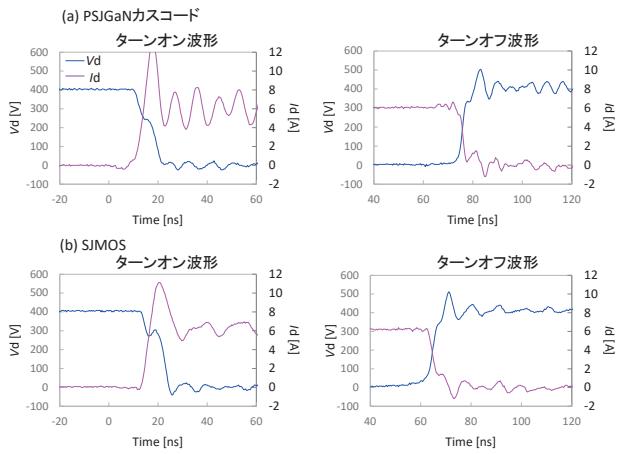

次に、L負荷ハードスイッチング条件下でスイッチング特性を評価した（図10）。評価結果の一例として、400V, 6A動作時のSW波形を図11に示す。

図 10. PSJGaN カスコードの SW 評価回路

図 11. (a) PSJGaN カスコードおよび (b) SJMOS の SW 波形

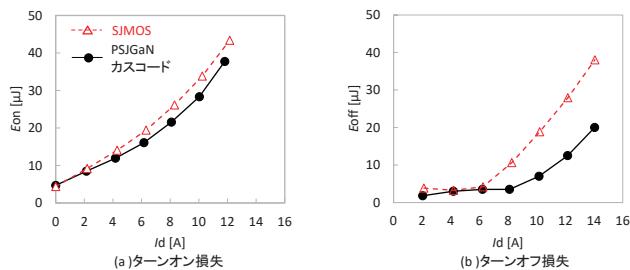

これらのSW特性の評価結果から得られたPSJGaNカスコードおよびSJMOSのターンオン、ターンオフにおけるエネルギー損失は、図12のようになる。この結果から、SW特性におけるPSJGaNカスコードのSJMOSに対する優位性が示された。

図 12. PSJGaN カスコードおよび SJMOS の SW エネルギー損失

#### 4. デバイスシミュレーション検討状況

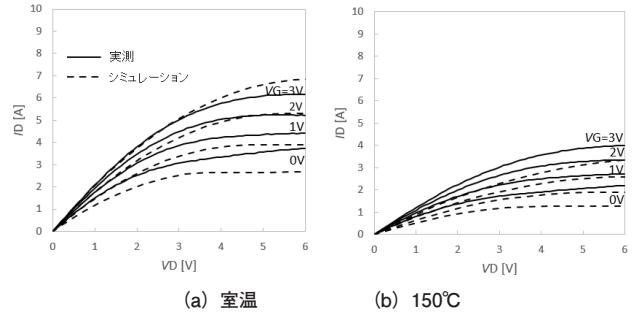

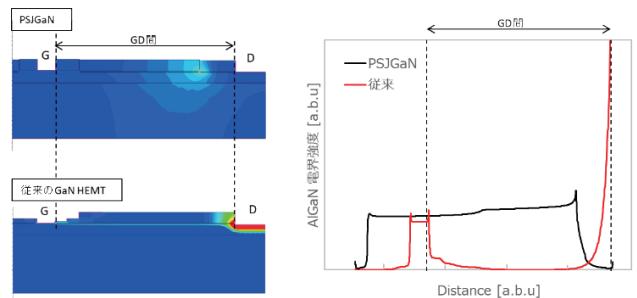

現在、TCADを用いたPSJGaNのデバイスシミュレーションモデルの検討を行っている。図13に示すように、I-V特性においては、室温では比較的良好な再現性が得られているが、高温ではまだ乖離が見られる。一方オフ動作時における電界強度分布の計算結果を図14に示す。FPを有する従来のGaN HEMTに比べ、より均一な電界強度分布を示す結果が得られている。今後は物理モデルの妥当性検証など、シミュレーションモデルの精度向上を進め、設計に活用していく予定である。

図 13. PSJGaN の I-V 特性

図 14. オフ時高電圧印可時の電界強度分布シミュレーション結果

#### 5. むすび

本稿では、電力変換ロスの小さいデバイスが作製可能な材料であるGaNを用いたPSJGaNについて紹介した。試作評価を行い、従来のGaN HEMTに対する耐圧、電流コラップスにおける優位性を示した。さらに、PSJGaNカスコードにおいてSJMOSに対する容量特性、SW特性の優位性を示した。PSJGaNのさらなる性能改善に加え、PSJGaNの性能を最大限に引き出すための駆動用ICの開発も同時に進めていく。また、TCADを用いたデバイスシミュレーションの検討をおこなっており、デバイス設計に活用することで、統合型デバイスの製品化へ向けて開発を進めていく。

#### 参考資料

- (1) 佐藤他, 豊田合成技報, Vol. 63, p. 41-45 (2021)