# ドッキング接続時の汎用化パフォーマンスボード設計

## Generalized Performance Board Design for Docking Interfaces

木村 将吾\*

Shougo Kimura

真尾 麻美\*

Asami Sanao

**概要** 当社はIPMやパワーマネジメントICなどのパワー半導体を取り扱っている。その半導体製造の前工程の一つであるウェーハテストには品質とスループット向上が常に要求されている。

このスループット向上には「半導体検査装置（ATE: Automated Test Equipment）」や「プローバ」が持つ複数チップを一度に検査する同時測定機能を使用して応える。同時に測定をするチップ数が増えることによりパフォーマンスボードやプローブカードなどのコンポーネントも大型化する傾向がある。大型のコンポーネントを製品毎に製造した場合はコストが増大することから、それを抑制するためにコンポーネントの汎用化設計をおこなった。本稿ではその事例について報告する。

### 1. まえがき

当社はIPM（Intelligent Power Module）やパワーマネジメントICなどのパワー半導体を取り扱っている。そしてそれらの製品に組み込まれる多様な半導体チップの電気的特性や機能などの検査（ウェーハテスト）もおこなっている。

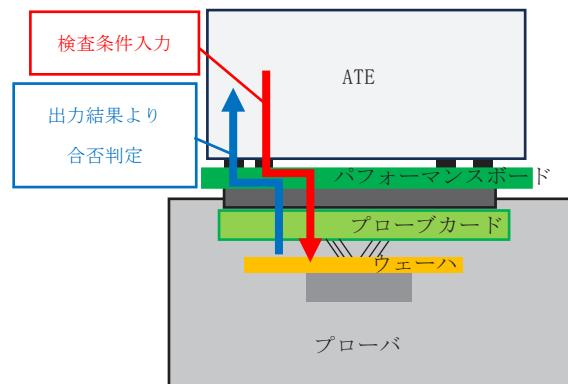

このウェーハテストでは、検査条件を入力し出力結果から合否判定をおこなうATEと、ウェーハの搬送や位置決めなどをおこなうプローバの二つの装置を用いる。しかしこれら装置だけではウェーハテストは成立しない。その他にもパフォーマンスボード（PB: Performance Board）とプローブカードという二つの重要なコンポーネントがある。これらは検査品質や製造工場のランニングコストに大きく関与する。

PBは測定対象チップの検査に必要な電子部品を搭載するインターフェース基板である。PBは電気信号をATEから受けとりプローブカードに渡す。一方、プローブカードはプローブ（探針）を搭載したインターフェース基板である。受け取った電気信号をチップに伝達する役割がある。

ウェーハテストにおいて、これらのインターフェース基板と装置の接続には二つの方式が広く用いられる。それはケーブル接続方式とドッキング接続方式である。

ケーブル接続方式は、その名の通りATEとPBをケーブルで接続する方式である。この接続方式をおこなう場合、ATEはデバイスから数m離れた位置に設置する。

一方、ドッキング接続方式はATEに直接PBを取り付ける（図1）。ケーブル接続方式に比べてデバイスまでの配線が数十cmと短い。そのため配線の寄生容量が小さく測定への影響を抑制することにつながる。さらに、この方式はケーブル接続方式のようなコネクタをほとんど用いない。したがって抜き差しによる接続不具合や断線リスクの低減になる。

利点の多いドッキング接続方式だが課題もある。PBやプローブカードが大型となり基板一枚当たりの製作費用が高額となる。従来、当社ではドッキング接続方式にて機能が異なる製品群毎にPBを設計、製作していた。そのためコスト増となっていた。またATEからデバイ

図1 ドッキング接続方式 模式図

\*技術開発本部プロセス技術統括部

ICデバイス開発部 テスト課

スマートでは構造が非常に密接でオシロスコープのプローブを自由にあてられるスペースがない。よって波形観測は容易ではなく特性評価の効率はケーブル接続方式に比べ低くなる傾向にあった。

## 2. 汎用化PB設計

従来、当社では機能が異なる製品群毎にPBを設計、製作していたが大型基板でありコスト増となっていた。

そこで当社製品の半導体チップを一つのPBで検査する（汎用化）という目標を立てPBを設計した。

### 2.1. 汎用化設計

生産性向上には汎用化とスループット向上を両立させる必要がある。パフォーマンスボードを汎用化することはATE搭載のリソース（電源、計測器、信号線など）をチップの端子へ適切に割り当てる、当社の半導体チップを一つのPBで検査できるようにすることである。

またスループット向上には複数のチップを一度に検査する同時測定機能を使用して、かつ同時測定数の最大化を図る必要がある。そのためにはATE搭載のリソースを無駄なく活用することが重要となる。

以上から汎用化とスループット向上を両立させるにはリソースを適切に割り振ることが設計のポイントとなることが分かる。その方法について検討をおこなった。

一般に半導体チップの電気的特性検査は複数の検査から成る。それらを一連のシーケンスで実行し、このシーケンス全体を考えてすべての端子にリソースを繋ぐ。それに加えて同時測定により複数のチップを検査すると必要なリソース数はさらに増加する。しかしATEの搭載リソースには限度がある。すべての端子に常時リソースを繋ぐと端子数の多い半導体チップでは同時測定数を多くすることはできない。

一方で、一つ一つの電気的特性検査では必ずしも全ての端子に常時リソースを繋いでおく必要はない。適切にリソースを割り振る上で、この点に着目した。ここで重要なことは、各端子における検査条件である。

当社で近年開発した半導体チップの端子と検査条件を分析した。その結果から汎用化とスループット向上を両立できるよう各検査に必要なリソースを割り出し、分岐回路などでリソースを無駄なく端子に割り当てる設計をおこなった。

### 2.2. 高耐圧への対応

当社で取り扱う製品は600Vを超える高耐圧製品のパワー半導体が多く高耐圧の基板設計が必要である。

高耐圧の基板設計には注意すべきことがある。それは

基板内に高耐圧配線パターンを形成した場合、絶縁破壊防止の観点から沿面距離を考慮することである。沿面距離を考慮するということは他の配線パターンや電子部品配置の自由度を下げ、汎用化を妨げる要因となる。そこで高耐圧配線は配線パターンではなく高耐圧用のワイヤーを用いた。これにより沿面距離を考慮する箇所が少なくなり、配線パターンや電子部品配置の自由度が高まつた。

### 2.3. 汎用化の効果

以上を踏まえて、汎用性のあるPBを製作した。これによって当社製品のほとんどの半導体チップを一つのPBで検査することが可能となった。

なお汎用化によりPBを複数保管することが不要になり理工数や保管場所の削減にもつながる。また製品群毎のPB設計の工数が少なくなり検査立ち上げの時間短縮につながる。

しかし製品に特化した専用回路を要求される場合がある。それについては製品に特化した専用回路を実装したPBを設計したので次の章で説明する。

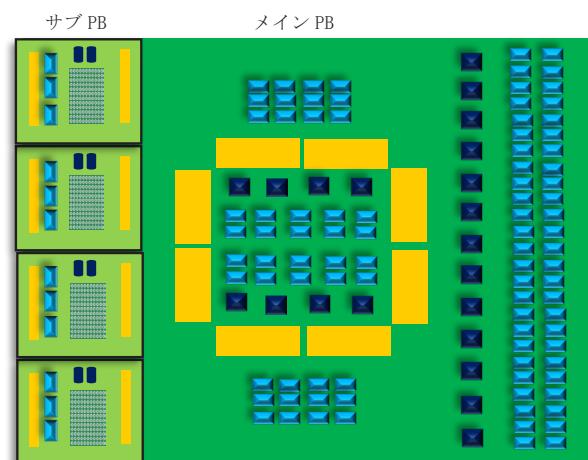

## 3. サブPB設計

ここまで述べた汎用化設計をおこなったPBのことをメインPB、製品に特化した専用回路を実装したPBのことをサブPBと呼ぶ（図2）。

図2 パフォーマンスボード 模式図

### 3.1. サブPB

サブPBは汎用化したメインPBと組み合わせて使用する。従来は全てのDUT（Device Under Test：被測定対象）分の検査回路を一つのPBに実装していたが、このサブPBはその回路の一部をDUT毎に分離したものである。

特性評価時にはPBの回路修正をおこなう場合が少なからずあるが、全てのDUT分の回路修正を待たずに特性評価ができることが利点の一つである。

またサブPBの設計は一つのDUT分のみでよい。プリント基板での製作により予備基板の製作も容易である。

量産時にも利点がある。サブPBの何れかに故障が発生した場合、予備基板に交換することで速やかに量産への復帰をおこなうことができる点である。

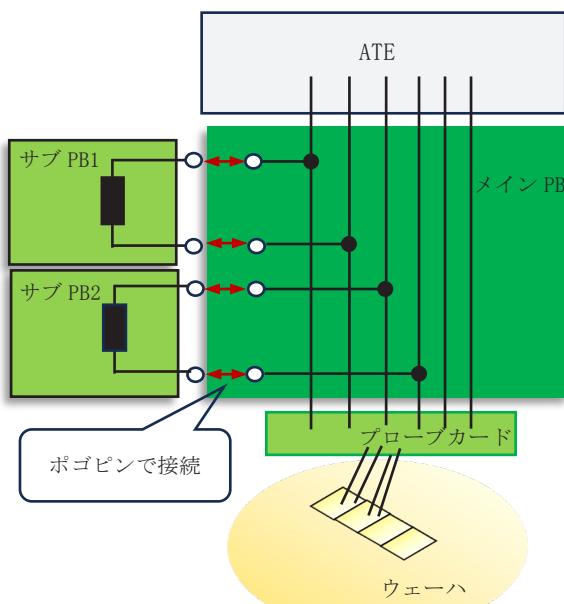

### 3.2. メインPBとサブPBの接続

サブPBはメインPBと組み合わせて使用するが、その接続をするためのポイントは二つある。

一つ目は、メインPBの回路にサブPBの回路を後付けできる設計としたことである。メインPBに予めサブPBと接続可能な配線を配置した（図3）。これによりメインPBの回路を変更せず回路の拡張が可能となる。またメインPBからサブPBへの繋がる配線の長さは電気的特性検査に影響の無い範囲に留めた。

図3 配線模式図

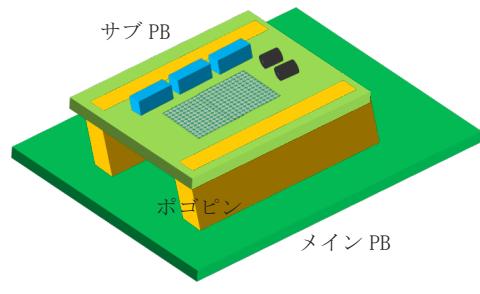

二つ目は、接続不具合を低減したことである。サブPBは製品群毎に設計することを想定した基板であり交換頻度が高い見込みである。そのような交換頻度が高い接続部に機械的寿命が短いコネクタを用いると故障リスクが大きくなる。それゆえ比較して接点が長寿命であるポゴピンを選定した（図4）。

図4 PB接続模式図

### 3.3. 交換作業の容易性

ウェーハテストでは製品群Aから製品群Bに検査対象を変更するときはコンポーネントも交換することが一般的である。当社でも製品群毎にPBとプローブカードを交換していた。しかし大型PBの交換は重量が重く作業効率が悪い。一方、サブPBの基板面積はメインPBの約二十分の一と小型で軽量である。サブPBを交換する方がより作業性が良い。

このようにサブPBをメインPBに後付けできることで製品に特化した検査要求へ柔軟な対応が可能となった。

## 4. モニタPB

ドッキング接続方式はATEと半導体チップとの距離が近いのでケーブルの影響は小さい。反面、一章でも述べたように構造上の理由によりオシロスコープなどの外部計測器での波形観測は容易ではない。それにより特性評価の効率が悪いという課題がある。このような背景から、当社ではモニタPBという観測専用のコンポーネントを製作した。

このモニタPBは特性評価時の波形観測のみPBに取り付ける。また着脱も容易である。この結果、特性評価の効率は飛躍的に向上した。

## 5. 今後の課題

今回汎用化パフォーマンスボード（メインPB）、サブPB、モニタPBを設計した。

しかし、もう一つ重要なコンポーネントの課題がある。それはプローブカードの汎用化である。

プローブカードの汎用化は、PBより複雑である。その一番の要因は高耐圧製品を検査することにある。高耐圧検査では基板沿面距離の確保が必要である。しかしプローブカードはPBに比べ基板寸法と実装可能面積が小さい。さらに汎用化をより難しくしている原因是半導体チップ上の高圧端子が多種多様な配列になっていることである。

PB同様に製作コストや開発リードタイム短縮の観点からもプロープカードの汎用化は重要な課題である。複雑ではあるが、引き続き汎用性を高める設計検討を進めます。

## 6. むすび

ウェーハテストで重要なコンポーネントであるパフォー

マンスボードの汎用化設計をおこなった。これにより大型であるメインPBを交換する事や複数枚製作をすることもなくなり作業性は向上し、コストも抑制した。

今後はプロープカードも汎用化設計を進めてさらなるコスト低減をおこない、お客様に満足のいく製品を提供していく。