# パワエレ制御向け RISC-V マイコン MD6605 の開発

## RISC-V Microcontroller MD6605 for Power Electronics Control

山崎 尊永\*

Takanaga Yamazaki

宍戸 仁美\*\*

Hitomi Shishido

**概要** サンケン電気は電源やモータなどの先進的なパワエレ制御システム向けに、RISC-V CPUコア、22nm超低リークプロセス、およびReRAM不揮発メモリ技術を使用したマイコンMD6605を開発した。MD6605はRISC-V CPUコアに加え、デジタルフィルタ演算用DSPと高速タスク・スイッチが可能なEPU(Event Processing Unit)によるヘテロジニアスマルチコア構成を採用しており、パワエレ制御システムの高効率化と高機能化を実現する。MD6605の製造には、マイコンとしては最先端の22nm超低リーク・プロセス技術と不揮発メモリReRAM(抵抗変化型メモリ)を採用した。サンケン電気は、MD6605を活用し、各種パワエレ制御システム向けの製品群を積極的に展開する予定である。

### 1. まえがき

近年の脱炭素に向けたGX(Green Transformation)活動推進の中で、電子機器の省エネ性能が従来以上に厳しく求められている。特に生成AIの普及に伴い増加するデータセンターではその電力消費量の多さから、パワーデリバリ経路の電力ロスの削減、すなわち高効率化が強く求められている。それだけではなく、世の中に広く普及する家電製品や産業機器などの電源システムにも絶え間ない高効率化が要求されている。さらに最近のAIプロセッサや高性能SoC(System on a Chip)は超微細プロセスの採用と動作クロック周波数の向上から、電源の低電圧化と大電流化が著しく、そうした厳しい条件のもとで高精度な電源が要求されている。

こうした高効率かつ高精度な電源の実現方法として、サンケン電気は電源のデジタル制御方式に長く取り組んでおり、最近のより厳しい要求にも応えられる先進型のデジタル電源制御向けマイコンMD6605を開発した。

MD6605は電源制御だけでなく、白物家電や専業機器に広く用いられるブラシレスDC(BLDC)モータ制御にも活用でき、その効率向上を実現するとともに、開発を容易化するパラメータ自動調整機能も提供する。

### 2. 電源のデジタル制御とそのメリット

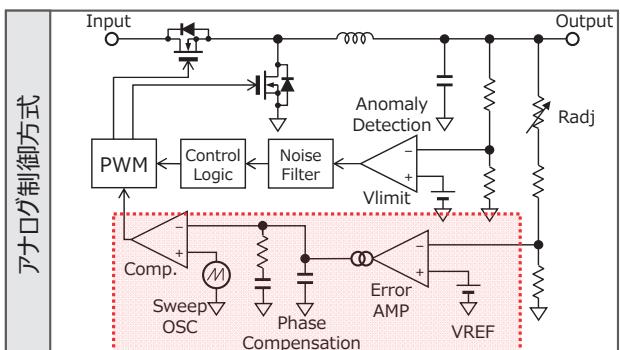

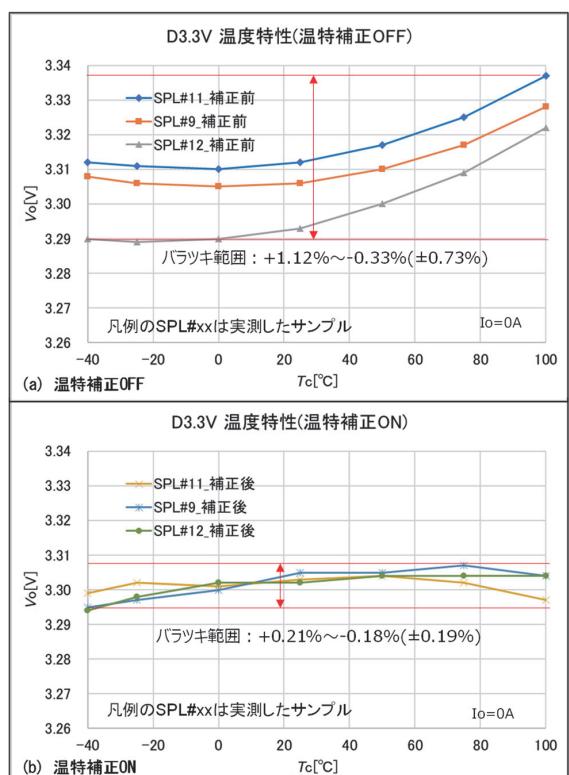

電源は図1に示すアナログ方式で制御されることが多い。古くから使われる実績のある方式で、比較的小規模のハードウェアで実現できる。一方、抵抗や容量による線形な位相補償のため特性パラメータ範囲に制限があり、コンバータのトポロジが固定化され、また最適制御の効率改善には複雑なハードウェアが必要となる。ノイズ対策はハードウェア手法のみのため、ノイズ対策用追加部品が多数必要である。外部との通信やインテリジェント機能の実現も困難である。特に高出力電源では、全負荷領域での損失低減が難しいため大きなヒートシンクが必要となり、システムコストが増大するなどのデメリットがある。

図1 電源(降圧Buckコンバータ)のアナログ制御方式の例

\* 技術開発本部パワーデバイス開発統括部

システム開発部

\*\* 技術開発本部パワーデバイス開発統括部

システム開発部 デジタル開発課

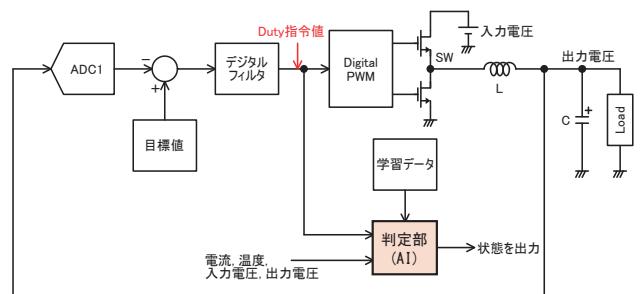

図2 電源（降圧 Buck コンバータ）のデジタル制御方式の例

図2はデジタル制御方式の電源を示す。アナログでは実現できない数値演算による線形または非線形なフレキシブル制御を実現する。DSP (Digital Signal Processor)などの演算器を使用するため、アナログ方式よりはハードウェア量は増える。一方で、任意の電源トポロジに対応可能、高度な制御アルゴリズムにより高精度かつ高速応答性を実現、負荷状態などに応じた最適制御により高効率を実現、ソフトウェアによりノイズ対策を臨機応変に対策可能、外部との通信とインテリジェント機能を実現、高効率化によるヒートシンクの削減とノイズ対策部品の削減、特に高出力・高精度電源においてシステムコストを削減可能、などのメリットがある。このため、サーバセンター向け電源や大型AV機器などの高出力電源や、高性能AIプロセッサ向けの低電圧・大電流電源にはデジタル制御方式を採用することが多い。

以下、デジタル制御方式のメリットのいくつかを具体的に説明する。

### (1) 任意の電源トポロジに対応可能

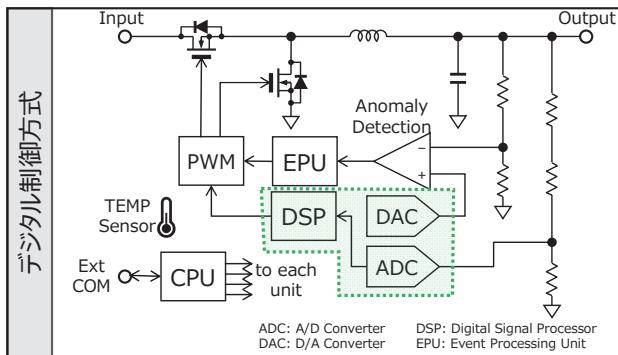

デジタル電源制御は基本的にソフトウェアによる制御であり、制御器のハードウェアを基本的に変えることなく、図2の降圧Buckコンバータに加え図3に示す様々な電源トポロジに対応可能である。

図3 デジタル電源が対応できる様々な電源トポロジ

### (2) 高精度な出力電圧を実現可能

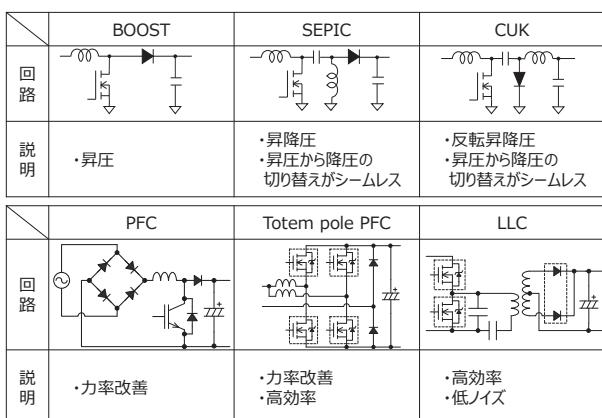

温度センサーで周囲温度をリアルタイムに検出して補正をかけることで、図4に示すような温度変動特性が極めて少ない電源を実現できる。

### (3) 全負荷領域での効率向上

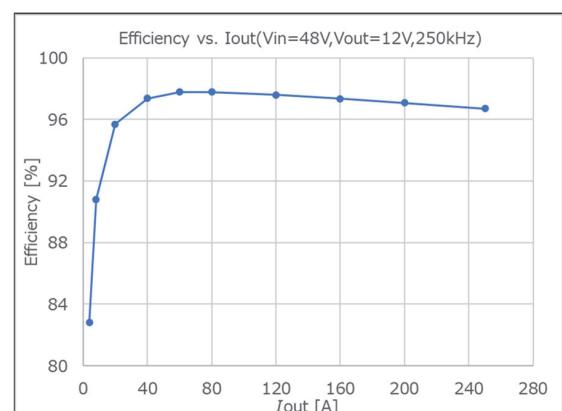

一般に電源は軽負荷領域で効率が低下する傾向にあるが、デジタル制御では負荷状態に応じたきめ細かい最適制御により全負荷領域での効率向上を図れる。例えば、低負荷領域ではスイッチング周波数を低下させるきめ細かい制御を行う。図5はデジタル制御による高効率電源（DC-DC中間バスコンバータ）の効率の例である。

図4 デジタル制御による温度補正の効果

図5 デジタル制御による高効率電源（DC-DC）の効率

#### (4) 高度な現代制御を実装可能

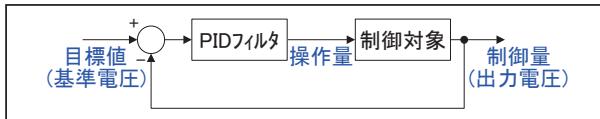

図6はアナログ制御方式で多く用いられるPID制御(古典制御)のブロック図を示す。目標値と出力電圧が等しくなるようにフィルタを介してフィードバック制御を行う。大電力で負荷変動が激しく、高精度な出力電圧を要求する電源系では、本方式は目標を達成しにくい。

図6 一般的なPID制御(古典制御)

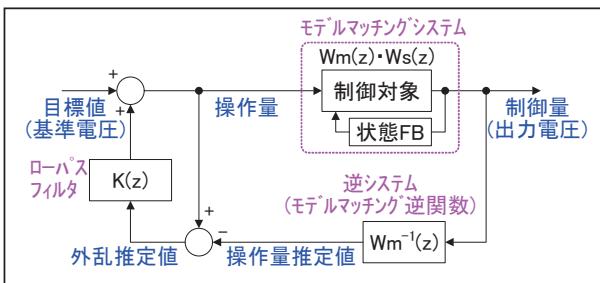

これを解決する手段が図7に示す近似的2自由度制御(現代制御)である。外乱推定値を目標値に加算することで外乱を打ち消すように制御する。数値演算が必要であり、デジタル制御でないと実現できない。

図7 近似的2自由度制御(現代制御)

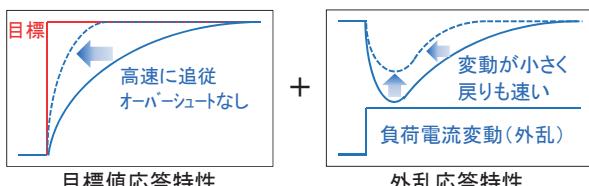

近似的2自由度制御の効果を図8に示す。目標値応答特性と外乱応答特性を同時に改善できる。本方式は、大規模AIプロセッサのような低電圧・高精度(0.5V~0.9V, ±20mV)かつ大電流(~100A以上)な負荷デバイスの電源の制御方式として有効である。

図8 近似的2自由度制御の効果

#### (5) 故障判定・故障予測が可能

デジタル制御を使うことで、電源の異常の予兆を早期に検出することが可能になる。

- FFT処理：電源出力電圧の波形をA/D変換器でサンプリングした結果を、FFT処理して周波数成分の変化から異常の予兆を検出する。

- エッジAIの活用：PWMのデューティ指令値のリアル

図9 エッジAIによる故障予測

タイムな時系列パターンから、エッジAIが学習データをもとにして異常の予兆を検出する(図9)。

#### (6) インテリジェント電源の実現

マイコン(CPU)を使うデジタル制御方式では、複雑なシステム処理が可能になる。

- 多出力電源のシーケンス制御：複数の電源出力レーンの、立上げ・立下げシーケンスを任意に設定可能。

- 通信制御：外部との通信で出力電圧の変更、ON/OFF制御、電流制限値の変更、電源動作状態のモニタなどが可能(PMBUS, AVSBUS)。

- 運転ログ管理：電源の動作状況や異常検出状況を不揮発メモリにログとして記録可能。

- 自己診断：マイコンチップそのものの自己診断、および電源システム全体の自己診断が可能。異常があれば、外部にレポートするか、または自動的に遮断可能。

### 3. 電源制御用マイコンに必要な機能

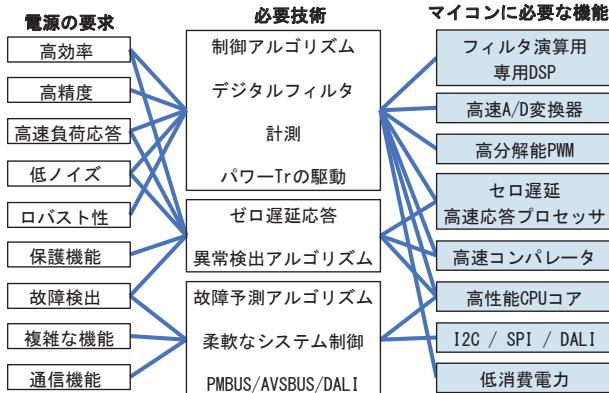

上記に示したデジタル制御をフレキシブルに実現するには、専用マイコンが必要である(図10)。電源制御は、制御対象が電気回路であり応答性が速いため、メカを相手にするモータ制御よりは格段に制御周期が短くなる。このため、高速DSPによる演算処理能力と高速A/D変換器が必須である。またPWMキャリア周波数も向上するためPWMタイマの高分解能化も欠かせない。くわえて、電源システムには、例えば、過電圧・過電流発生時の対応、電圧・電流のゼロクロス時の応答、異常や故障の監視と検出など、各イベントに対して高速に応答できる機能が必須で、シンプルな動作はハードウェアにより直接対応できるが、フレキシビリティが必要な複雑なケースは、CPUの割込み処理だとレイテンシが長すぎるため、特別な高速応答プロセッサが必要となる。このため、電源制御用マイコンは、単一のCPUコアだけでなく、DSPコア、高速応答プロセッサから構成されるヘテロジニアスマルチコアシステムが必要である。

図10 電源制御用マイコンに必要な機能

#### 4. パワエレ制御用マイコンMD6605

サンケン電気は、上記で説明した電源制御マイコンの次世代品としてMD6605を開発した。モータと電源を同時に制御するアプリケーションも視野に入れ、モータ制御に必要な機能も搭載し、総合的なパワエレ制御用マイコンとして開発を進めた。

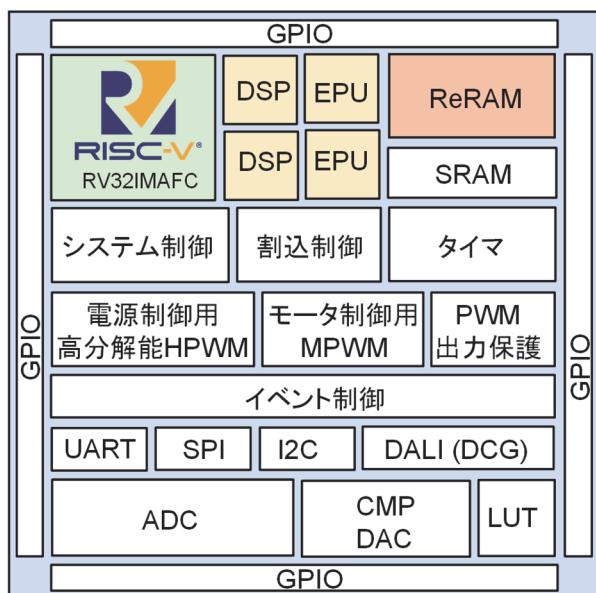

図11 MD6605のブロック図

図11にMD6605のブロック図を表1に仕様一覧を示す。以下、MD6605の主要な特長について説明する。

#### 5. ヘテロジニアスマルチコア

前述したとおり、MD6605は高効率・高精度なパワエレ制御のため異なる特長を持つ下記3種のコアにより並列処理するヘテロジニアスマルチコア構成を採用した。

- (1) CPU (Central Processing Unit) : 通信制御、運転記録、故障診断、非定常時の制御など、システム

表1 MD6605の仕様概要

| 項目         | 仕様                                    |

|------------|---------------------------------------|

| RISC-V CPU | 命令セットRV32IMAF、デバッガI/F=cJTAG           |

| DSP        | 2ユニット 浮動小数点演算                         |

| EPU        | 2ユニット 高速応答プロセッサ                       |

| ROM        | ReRAM(抵抗変化型メモリ) 128KB+ECC             |

| RAM        | 8KB+ECC                               |

| 割込み        | 64要因 優先レベル×16 周期割込みタイマ                |

| システム制御     | 内蔵発振器 PLL 低電力制御 機能安全                  |

| タイマ        | 汎用16ビットタイマ 低電力タイマ WDT                 |

| HPWM(電源用)  | 高分解能PWM 出力×8                          |

| MPWM(モータ用) | 相補PWM 出力×6                            |

| イベント制御     | チップ内イベントスイッチ網 イベント加工                  |

| シリアル通信     | UART×3ch SPI×1ch I2C×1ch DALI(DCG)    |

| ADC        | 3ユニット 12ビット 3MSPS 8入力/ユニット            |

| コンバーティ     | 6ユニット 10ビットDAC付き 出力論理演算               |

| GPIO       | 汎用入出力、全端子に任意周辺機能設定可                   |

| 動作条件       | 66.6MHz, V <sub>DD</sub> =3.3V 単一電源動作 |

| 製造プロセス     | TSMC 22nm ULLプロセス ReRAM混載             |

全体を制御する役割を担う。プログラム規模が増えており、高性能32ビットCPUが必要である。デジタルフィルタ処理やモータのベクトル制御では、固定小数点演算を使うとダイナミックレンジの低下やオーバフロー・アンダーフローの対策が必要なため、演算には浮動小数点処理が要求される。このためCPUにも浮動小数点演算命令の実装が必要である。

- (2) DSP (Digital Signal Processor) : パワエレ制御のデジタルフィルタ演算を直接担うコアで、制御サンプリング周波数の向上に伴い高速な演算処理が必要である。整数演算に加えて浮動小数点演算でも、積和命令を1サイクルで処理する性能が必要である。

- (3) EPU (Event Processing Unit) : コンバータ回路の電流や電圧がゼロクロスしたときのコンバータの反転イベントへの応答、A/D変換器の変換終了やPWMタイミングの時間イベントに伴うデータ転送とデータ演算加工など、パワエレ制御には多くのイベントに対する高速応答性が要求される。これをCPUの割込み処理で実現しようとすると汎用レジスタの退避などによるレイテンシが大きく間に合わない。このため複数のイベントに応答してゼロ時間でタスク切替え対応できる専用プロセッサが必要である。

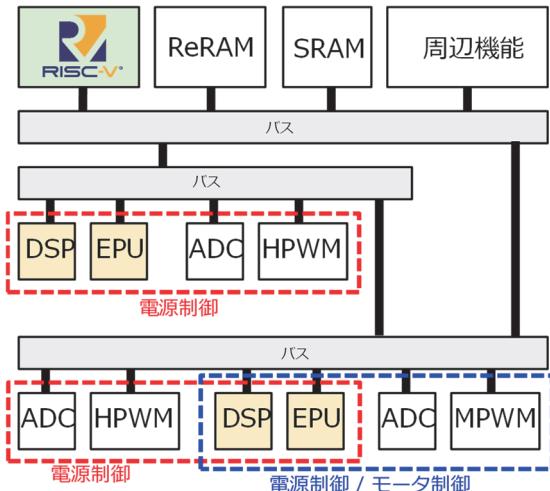

図12にMD6605のヘテロジニアスマルチコア構成を示す。パワエレ制御において、DSPとEPUは頻繁にA/D

変換器とPWMタイマと連携するので、それらを専用バスで接続した。DSPとEPUはそれぞれ2ユニット搭載し、CPUとあわせて合計5個のコアで並列処理を行う。

並列処理化により動作周波数を上げることなくシステム性能を向上できる。MD6605の動作周波数は66.6MHzであるが、ヘテロジニアス構造により浮動小数点演算性能は400MFLOPS、整数演算性能は600MOPSに達する。

図12 MD6605のヘテロジニアスマルチコアの構成

## 6. 32ビットRISC-V CPUコアの搭載

MD6605のメインCPUとしては、最新アーキテクチャであるRISC-V<sup>\*</sup>を採用した。RISC-Vは命令セットアーキテクチャがオープンに公開されており、誰もが自由に設計することができる。市販のIPコアもあるが、サンケン電気はこれを独自に開発した。RISC-Vは命令セットがシンプルで、処理性能も高くコード高率も高い。開発環境などアーキテクチャを取り巻くエコシステムも充実してきており、今後の普及が期待されている。表2にMD6605に搭載したRISC-V CPUコアの仕様を示す。

表2 MD6605に搭載したRISC-V CPUコアの仕様

| 項目            | 仕様                                              |

|---------------|-------------------------------------------------|

| 命令セット         | RV32IMAF(C(高速乗算、高速浮動小数点演算))                     |

| パイプライン        | 整数:3~5ステージ 浮動小数点:5~6ステージ                        |

| 整数乗算          | 1cyc                                            |

| 浮動小数点         | 加算/減算/乗算/積和: 1cyc                               |

| デバッガ          | 2-wire cJTAG ハードウェアブレーク×4                       |

| 割込み           | 標準×3本 + 拡張×64本(優先レベル×16)                        |

| Dhrystone 2.1 | 1.6 DMIPS/MHz                                   |

| Coremark 1.0  | 3.30 Coremark/MHz                               |

| 開発環境          | ・MD Studio (Eclipseベース)<br>・3rd Party製開発環境(計画中) |

\* RISC-VはRISC-V InternationalとKrsti Asanović氏の登録商標である。

## 7. 高機能化したDSPコアとEPUコア

MD6605は独自開発のDSPとEPUを2ユニットずつ搭載している。表3にDSPとEPUの仕様を示す。

表3 DSPとEPUの仕様

| 項目         | DSP                                            | EPU              |

|------------|------------------------------------------------|------------------|

| 用途         | CPUと独立した高速演算                                   | パワエレ制御イベントへの高速応答 |

| 搭載コア数      | 2コア                                            | 2コア              |

| スレッド数      | 1スレッド                                          | 2スレッド            |

| 命令セット      | 16ビット固定長                                       |                  |

| パイプライン     | 3~5段                                           |                  |

| イベント応答     | イベント待ち、タイマ待ち、イベント出力(リアルタイム応用性能向上)              |                  |

| スレッド制御     | なし                                             | ゼロ時間スレッド切替       |

| 32ビット固定小数点 | 加算/減算/乗算/積和: 1cyc<br>除算: 8cyc (Newton-Raphson) |                  |

| 32ビット浮動小数点 | 加算/減算/乗算/積和: 1cyc<br>除算: 8cyc (Newton-Raphson) | なし               |

| デバッグ       | ステップ動作/PCブレーク/データ・ブレーク/ソフトウェア・ブレーク             |                  |

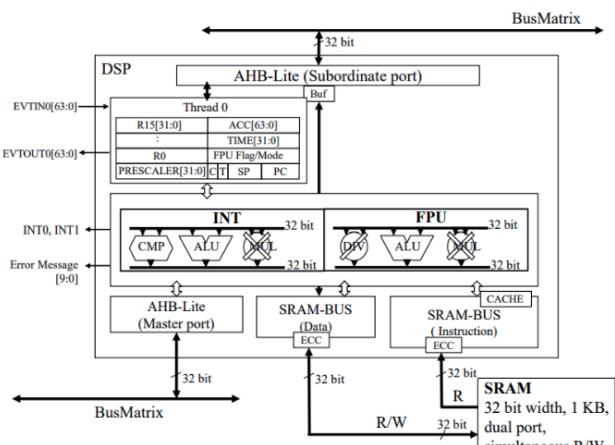

DSPは32ビット浮動小数点および固定小数点の演算ユニットを持つプロセッサである。図13にDSPのブロック図を示す。DSPはCPUを介さずにイベント入力に応じて演算・論理処理・データ転送を実行できる。浮動小数点、固定小数点とともに加減乗算や積和演算を1サイクルで処理でき、位相補償演算、ベクトル制御など高精度な制御にも対応可能である。ニュートン・ラプソン法による除算は8サイクルで実行可能である。

図13 DSPのブロック図

次にEPUを紹介する。DSPとEPUは浮動小数点器の有無とスレッド数が異なる(表3参照)。

EPUは、2つのスレッド、1つの固定小数点の演算ユニットを持つプロセッサである。スレッドは、汎用レジスタ16個やタイマ、プログラムカウンタなどを持つ。EPUは、スレッドに割り当てられたタスク(プログラム)

を1つの演算ユニットで優先順位に従って順番に実行する。前述したとおり、パワエレ制御には多くのイベントに対する高速応答性が要求される。EPUはイベント信号を受信すると瞬時に、そのイベントに対応するタスクを実行することが可能である。

次にイベント応答によるタスク切替えについて説明する。スレッドが汎用レジスタなどのリソースを持つことで、タスク切替え時にも、そのタスクが使用中のスレッドのデータはそのまま保持される。そのため、データの退避が不要である。CPUのように割込み時にデータを退避・復帰する操作が不要であるため、EPUはゼロ時間でのタスク切替えが可能である。

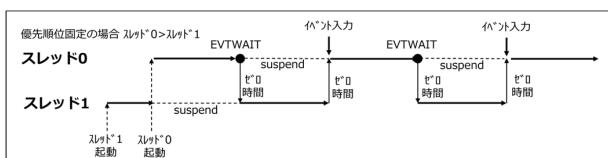

ゼロ時間でのタスク切替えの例を図14で示す。この例では優先順位に固定優先（常にスレッド0 > スレッド1の優先順位）を選択している。スレッド0が起動前やイベント待ちの状態のときには、スレッド1の命令を実行する。イベント待ち状態のスレッド0にイベントが入力された場合には、スレッド0の命令を実行する。このスレッド切替え時には、ゼロ時間での切替えがおこなわれる。

図14 ゼロ時間タスク切替え

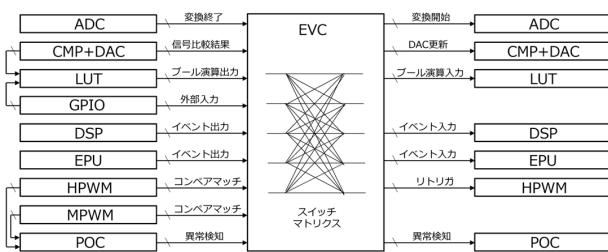

EPUの特長の一つは、イベント入出力を命令により制御可能であることである。ここでMD6605のチップ内イベント接続についても紹介する。パワエレ制御用マイコンには、各モジュールがタイミングを合わせた同期動作が要求される。それを実現するのが、各モジュールに入出力されるイベントである。図15のようにMD6605のチップ内には、A/D変換終了やコンパレータ反転など、多種類のイベント信号が行き交っている。イベント信号の接続は、EVC(Event Controller)により自由に選択でき、各モジュールが同期動作することができる。

図15 チップ内イベント接続

## 8. 周辺機能とその特徴

MD6605に搭載した主要な周辺機能を紹介する。

### (1) HPWM：高分解能 PWM

HPWMは、電源制御用の高分解能PWMである。前述のとおり、電源制御では制御周期が短く、PWMキャリア周波数の向上のため高分解能化が重要である。MD6605に搭載されているHPWMは分解能が1ns未満であり、細やかなデューティの調整が可能となる。

HPWMは16ビットカウンタを持ち、カウンタ値と比較値との比較により、周期やデューティを決定する。また、カウンタはアップカウントモードとアップ・ダウンカウントモードの両方をサポートしている。

さらに、HPWMは電源制御における過電圧・過電流発生時の保護動作や、電圧・電流のゼロクロス時の応答を可能とするリトリガ機能を搭載している。このリトリガ機能により、イベントに応じてカウンタ動作をリアルタイムで変更することで、HPWMの停止やデューティカット、サイクルカットを行うことができる。

### (2) MPWM：モータ用 PWM

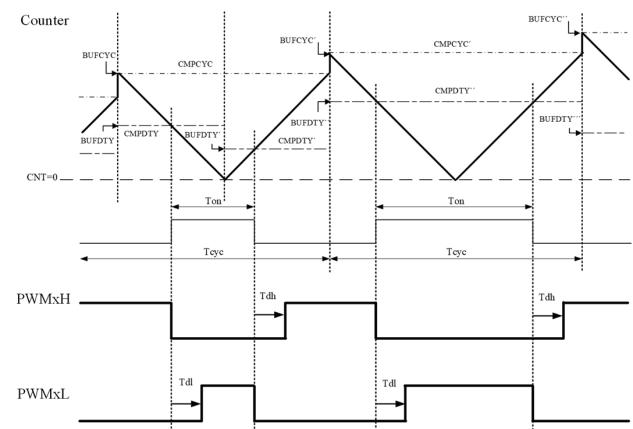

MPWMは、モータ制御用のPWMである。32ビットアップダウンカウンタを持ち、6本（3ペア）のPWM信号を生成できる。

図16のように、MPWMの信号生成には、モータ制御においてノイズ耐性が高く、精密な制御に適したカウントアップとダウンを繰り返すセンターライメント方式を採用している。また、デューティ範囲は0%～100%で調整可能であり、スイッチの同時ONを防ぐためのデットタイム機能を備えている。

図16 MPWM のカウンタと出力波形

### (3) POC (PWM Output Controller) : PWM出力コントローラ

POCは、コンパレータやルックアップテーブルの出力信号の変化やEVCからのイベントに応じて、PWM出力端子をあらかじめ設定した端子状態に固定する。電源の異常状態に対応する際には、PWMの制御よりも先にPWM出力を固定することで、最短時間での保護処理を実現する。MD6605はPOCを2ユニット搭載しており、POC0がHPWMの出力制御、POC1はMPWMの出力制御をおこなう。

### (4) A/D変換器

MD6605に搭載したA/D変換器は、12ビットの分解能をもつ逐次比較型である。3ユニット搭載されており、電源制御では3コンバータの制御が可能であり、モータ制御では3相電流の同時サンプリングが可能である。

パワエレ制御における制御サンプリング周波数の向上に伴い、高速なA/D変換器が求められている。本A/D変換器は、小型化、高速化、低消費電力を実現しており、クロック周波数が66MHzのとき、最高変換速度は3MSPSである。

### (5) LPTMR：低電力タイマ

LPTMRは低電力モードから復帰するためのタイマである。パワエレ制御では、システム全体がアイドル状態のときなど、特定の条件下でマイコンを低電力モードに移行させる場合がある。MD6605には、以下の低電力モードと、それぞれの復帰要因がある。

- ①スリープモード：割込みで復帰

- ②スタンバイモード：GPIO割込み、CMPレベル割込み、LPTMR、DCG（DALI Control Gear）で復帰

- \* ノーマルスタンバイ（GPIO、CMP）

- \* LPTMRスタンバイ（GPIO、CMP、LPTMR）

- \* DCGスタンバイ（GPIO、CMP、DCG）

低電力モードの使用においては、一定時間の低電力モードの後に復帰し、タスクを実行するという処理が行われることがある。LPTMRはこのような周期的な低電力モードからの復帰に使用することができる。

## 9. TSMC 22nmプロセスとReRAMの採用

MD6605は、マイコンとしては最先端となる22nm ULL (Ultra Low Leak) プロセスとReRAM（抵抗変化型メモリ）を採用し台湾TSMCで製造する。

22nmプロセスは、①チップサイズ縮小によるコスト

低減、②ULLプロセスとHVT (High Vt) トランジスタによる消費電力の低減、③プレーナプロセスの最終世代であり将来の長期供給が確実、を理由として採用した。

プログラムを格納する不揮発メモリとしてはReRAMを採用した。22nm世代では下地構造が複雑なFLASHメモリの実装は困難であり、配線層に記憶材料を構築するシンプルな構造のReRAMが好適である。ReRAMは、①追加マスク枚数が少なくコスト面で有利、②FLASHメモリのようなブロック消去をせずにカラム単位での上書きができるためユーザの使い勝手が向上、③信頼性（データ保持特性）はFLASHメモリと同等以上の実力、という特長がある。

微細プロセス向けの不揮発メモリの選択肢としては、MRAM（磁気抵抗メモリ）もあるが、コスト優位性の面から車載向けを含めReRAMの採用例が増えている。

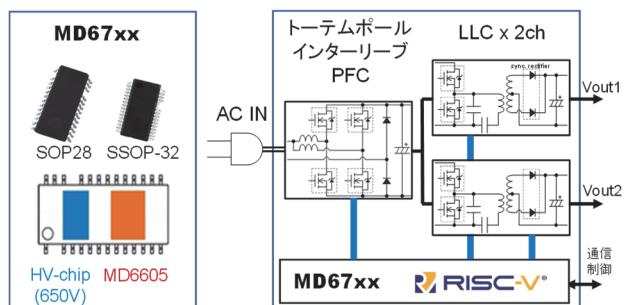

## 10. AC-DC電源IC製品への展開

MD6605は単独のマイコンとして製品化する予定はなく、システム内で使い勝手を向上させるため、ゲートドライバなどを搭載した高耐圧チップと一緒にワンパッケージ化した製品として量産予定である。

図17はAC-DC電源のPSU (Power Supply Unit) 向けの展開製品MD67xxを示す。MD6605を内蔵したMD67xxが、トーテムポールPFCと、電流共振LLCコンバータ×2チャネルを同時に制御できる。PSUに応用了MD67xxのメリットを以下に示す。

- (1) ブリッジレスのトーテムポールPFC、ゼロ・クロス・スイッチング、負荷状態に応じた最適制御により全負荷領域で高い効率（> 98%）を実現。

- (2) PFCの高速最適制御による低THDを実現。

- (3) LLCの高度な電流モード制御で高速応答を実現。

- (4) 高速スイッチング可能なGaN/SiCの活用により、ヒートシンクの小型化やプラットフォームの小型化を実現。

- (5) 通信制御、運転ログ管理、故障診断などの高機能化。

図17 MD6605のPSUへの応用例

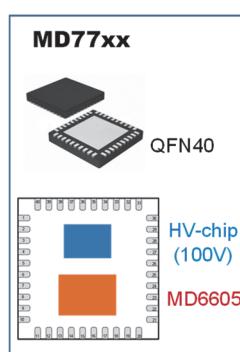

## 11. DC-DC電源IC製品への展開

図18はDC-DC電源の中間バスコンバータIBC(Intermediate Bus Converter)向けの展開製品MD77xxを示す。MD6605を内蔵したMD770xが、高効率ハイブリッドコンバータを複数チャネル並列化して制御する。IBUに応用したMD77xxのメリットを以下に示す。

- (1) 先進ハイブリッドコンバータにより、高いステップ・ダウン比率においても98%以上の高効率を実現。

- (2) 複数チャネルのコンバータを並列多相動作させ、電流バランスを精密制御することで出力200A以上の大电流化を実現。

- (3) MD770xひとつで、複数種類のコンバータ制御が可能（例：デュアルIBC、またはシングルIBC+POL x 6ch、など）。

- (4) PMBUS/AVB BUSの通信による電源制御が可能。

図18 MD6605のIBCへの応用例

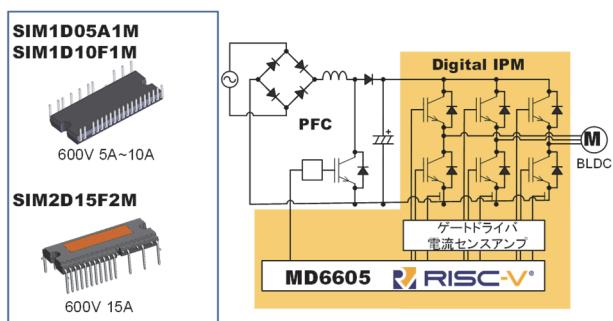

## 12. モータ制御向け製品への展開

図19は産業分野や白物家電分野に使うブラシレスDCモータ(BLDC)制御へのMD6605の応用例を示す。一般的のIPM(Intelligent Power Module)はパワー素子とゲートドライバを内蔵するが、さらにMD6605も搭載したデジタルIPMとして製品化し、モータをドライブするだけでなく回転数やトルクの制御も可能にする。MD6605の処理能力の高さからモータ制御と同時に電源制御(PFC制御など)も行うことができる。MD6605を搭載

したデジタルIPMの特長を以下に示す。

- (1) センサレスベクトル制御機能と、自動的にモータパラメータを抽出して最適制御を行うオートセルフアライメント機能を搭載し、高効率化を実現。

- (2) ゲート駆動波形のdv/dtが調整することで、低ノイズ化を実現。

- (3) モータと電源(PFC)の同時制御により部品点数を削減し基板サイズとシステムコストを低減。

- (4) モータパラメータの自動チューニング用GUIアプリの提供により、開発効率を向上。

- (5) 通信機能、故障検出機能、故障予測機能などによるインテリジェント化。

図19 MD6605のモータ制御への応用例

## 13. むすび

先進的なパワエレ制御システム向けに、RISC-V CPUコア、22nm超低リークプロセス、およびReRAM不揮発メモリ技術を使用したマイコンMD6605を開発した。CPU、DSP、EPUによるヘテロジニアスマルチコア構成により高い処理性能を実現している。今後、MD6605を活用した高効率パワエレ制御向けICの展開を継続し、脱炭素社会を目指すGXへの取り組みに貢献していく。

## 参考文献

- 1) The RISC-V Instruction Set Manual Volume I Unprivileged Architecture, May 2025, RISC-V International.

- 2) The RISC-V Instruction Set Manual Volume II Privileged Architecture, May 2025, RISC-V International.