# スマート SiC-IC の高速駆動と短絡保護技術

～誰もが簡単に超高速スイッチング性能を引き出せる SiC-MOSFET ～

## High-Speed Driving and Short-Circuit-Free Protection Technology for Smart SiC-IC

横井 魁人\*

Kaito Yokoi

町田 修\*\*

Osamu Machida

**概要** SiC MOSFETは高耐圧でありながら小型化ができるため、高圧回路で大電流の高速なスイッチングが可能となる。特にSiC MOSFETのソース電極に、主電流の流れないゲート用ソース端子を用いることで、低インダクタンスのゲート制御が可能となり、高速なスイッチングを実現できる。しかし、高圧スイッチング中に短絡が発生した場合、SiC-MOSFETには数千A/μsの高速で短絡電流が流れ、1μs以下の短絡破壊が発生する。このような4端子(4P)駆動に対して、Si-IGBTでは一般的な3端子(3P)駆動をSiC-MOSFETでおこなった場合、スイッチング速度は大幅に低下するが、短絡電流も制限されて短絡耐量時間が数倍延びることが確認された。この4P駆動による高速スイッチングと3P駆動による短絡保護を、両立する駆動方法を開発した。

### 1. まえがき

SiCはSiの約10倍の破壊電界を有し、高耐圧デバイスに応用した場合、素子サイズを数分の一に小型化できるポテンシャルを有している。しかし、従来のSi素子に最適化された高圧回路の中に単純に置き換えた場合、その性能が出しきれないため、SiCデバイスを最適に設計し、駆動する必要がある。

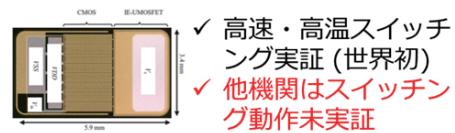

図1に示す通り、産業技術総合研究所(産総研)では超高速スイッチングを可能とするSiC-CMOS内蔵MOSFETの開発をおこなっている。このチップはSiC-MOSFETのゲート配線による浮遊インダクタンスを最小にする狙いで、SiC-MOSFETのチップ内にゲート駆動用のCMOSを有している。この技術により1200Vの電圧を数nsでスイッチングすることに成功している。<sup>1), 2), 3), 4)</sup>

一方、このような高速な素子を高圧回路に用いた場合、様々なサージが問題となるが、その中でも、短絡時のサージ電流は大きな問題である。短絡時に高速なスイッチ

グにより非常に短時間で短絡電流がピークとなり、短絡破壊に至るためである。<sup>5), 6), 7)</sup>

この課題に対し、安全に保護するゲート駆動技術の開発を産総研と当社が研究しており、“誰もが簡単に超高速スイッチング性能を引き出せるSiC-MOSFET”の実現を目指している。

#### 産総研のSiCパワーIC技術

- ✓ 高速・高温スイッチング実証(世界初)

- ✓ 他機関はスイッチング動作未実証

・NEパワーレアード2021 最優秀賞

・ISPSD2021 Best Paper Award

#### サンケン電気の外部保護回路技術

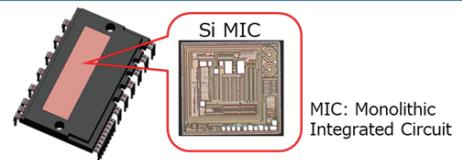

世界最高レベルの小型・省エネルギー化可能なSi MIC搭載モジュール製品

\* 技術開発本部プロセス技術統括部

\*\* 技術開発本部プロセス技術統括部

## 2. 高速スイッチングと短絡耐量の関係

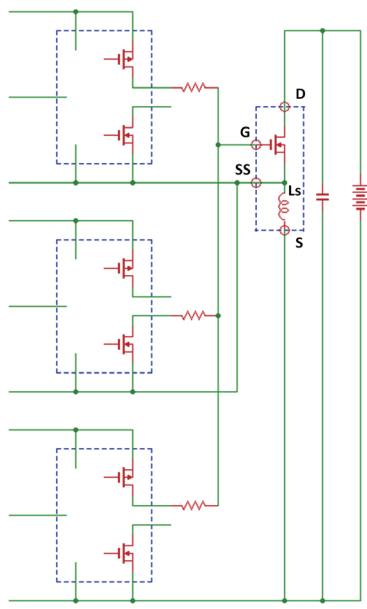

図2にSiC-MOSFETの短絡評価に用いた回路図を示す。DUTのMOSFETにはソース電流が流れ込まないセンスソース(SS)端子が存在し、通常のソース端子(S)と切り替えて評価可能な回路である。

図2 SiC-MOSFETの短絡評価回路

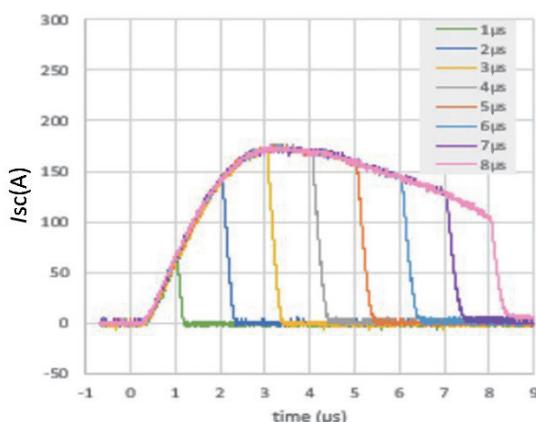

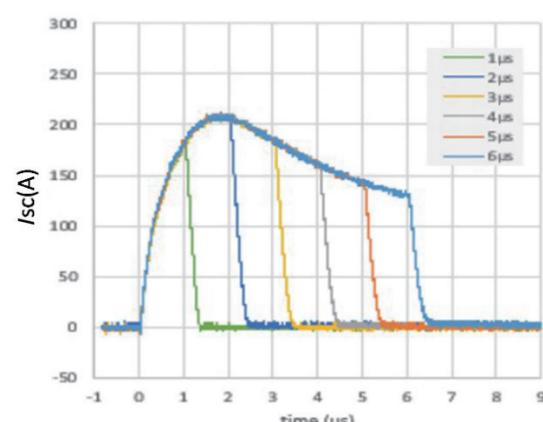

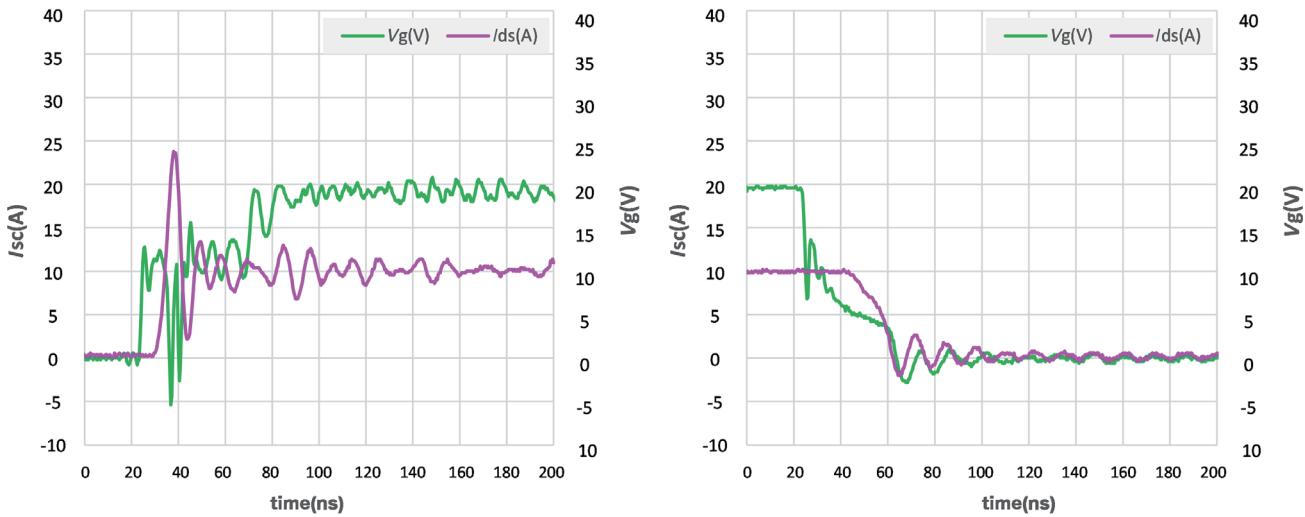

また、図3にSiC-MOSFETの典型的な短絡電流波形で $R_g = 470\Omega$ と $R_g = 10\Omega$ の場合をそれぞれ示す。ゲートの駆動端子にはS端子を使用し、3P駆動している。

SiC-MOSFETは1200V、40mΩで、 $V_d = 600V$ で負荷短絡した状態を再現している。 $R_g = 470\Omega$ を介してSiC-MOSFETをスイッチングした場合、3μs程度で電流最大となり、その後、8μsにかけて、SiC-MOSFETの自己

発熱で電流が低下し、短絡耐量が低い素子の場合は破壊に至る。

これに対して、 $R_g = 10\Omega$ に変えた場合、SiC-MOSFETのスイッチング速度が速まるため、急速に短絡電流が上昇し、2μsで電流ピークに達し、 $R_g = 470\Omega$ の場合よりも高くなっている。その後、SiC-MOSFETの温度上昇により急速に電流が減少しており、短絡時間が減少する。

短絡破壊は、短絡電流×短絡電圧×短絡時間による消費エネルギーによるものであり、図3に示すように、 $R_g$ を低くしてスイッチングスピードを速めると、短時間で電流がピークに達し、破壊リスクが高まることがわかる。

## 3. 4P駆動と3P駆動について

一方、SiC等の化合物半導体のパッケージは、高速にスイッチングするためにソース電流を流さないゲート駆動用ソース端子(SS)を設けた4端子パッケージが主流となっている(図2)。

4P駆動は寄生インダクタンスが無く、高速にスイッチングできるが、前述同様に短絡破壊に至るまでの時間、短絡耐量時間が減少する。3P駆動は寄生インダクタンスに発生する電圧によって電流変化が抑制され、短絡耐量に優れるがスイッチングが遅い。

今回、この様な高速スイッチングによる短絡耐量時間が極端に短くなる問題に対し、ソース端子を4P接続と3P接続の切替をすることで改善する技術を開発した。

スイッチング時はゲート駆動の接続をセンスソースに繋ぐ4P接続で高速スイッチングをおこない、その後の定常時は3端子のソースに繋ぎ変えることで、短絡耐量が向上することが期待される。このソース端子の切替手法の最適化をおこない、SiC-MOSFETの最速のスイッチングと短絡耐量時間の大幅な延長の両立を狙った。

(a)  $R_g = 470\Omega$

(b)  $R_g = 10\Omega$

図3 SiC-MOSFETの短絡電流例

#### 4. 新規Monolithic IC (MIC) 紹介

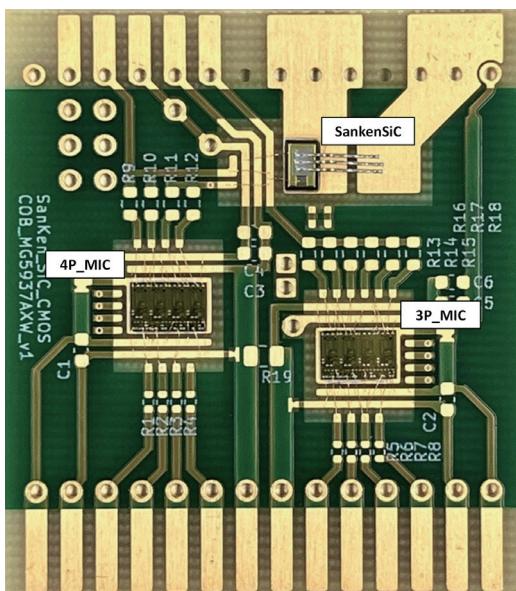

図4に4P, 3P切替機能を有するMICのSiC-MOSFET評価ボードを示す。MICには、4P駆動用のチャンネルが3つと3P駆動用チャンネルが1つある。4P駆動用3チャンネルは、産総研のCMOSドライバー搭載SiC-MOSFETのP channel-MOSFET, N channel-MOSFET, 及び、パワーSiC-MOSFETのゲートを直接駆動するチャネルであり、ソース電流が流れないSS端子に接続して4P駆動する。一方、残りの1チャンネルもパワーSiC-MOSFETのゲートを直接駆動するが、ソース端子がS端子となり3P駆動する。

図4 SiC-MOSFETの短絡評価ボード写真

本MICは、短絡電流の急激な $di/dt$ をSS端子とS端子間の浮遊インダクタンスで発生する起電圧 $V_{ls}$ で検出して短絡遮断することを想定している。

MIC出力のDelay時間は300ns程度であり、短絡時に検出回路のDelay時間500ns以内を含めて、1μs以内に短絡保護が可能なMICである。さらに、並列で駆動した場合、いずれかのSiC-MOSFETの $V_{ls}$ で短絡を検出すると、同期して遮断できる機能も想定している。

1つのMICで産総研のCMOSドライバー搭載SiC-MOSFETを駆動できる設計だが、今回の評価ボードでは、4P駆動の高速化と3P駆動の短絡保護の効果を評価し易くするため、4P駆動と3P駆動のMICでそれぞれ2チップ構成とした。さらに、各チャンネルの出力は、SourceとSinkが個別に出力できるため、ON時の高速スイッチング時の $R_g$ を多段で切り替え可能であり、OFF時も同様に多段での切り替えが可能である。

#### 5. 実験結果

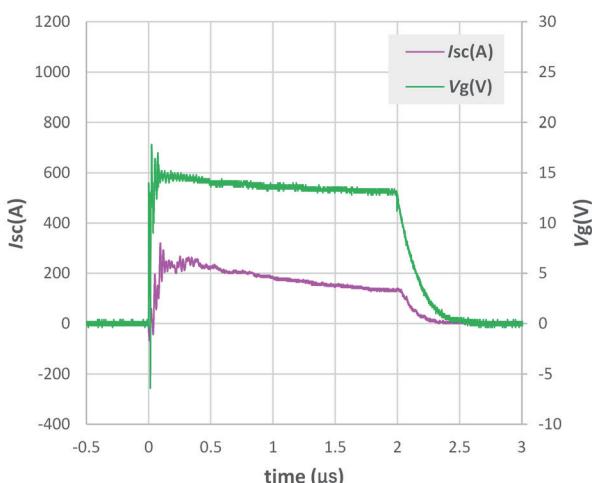

##### 5.1. 4P駆動の短絡波形

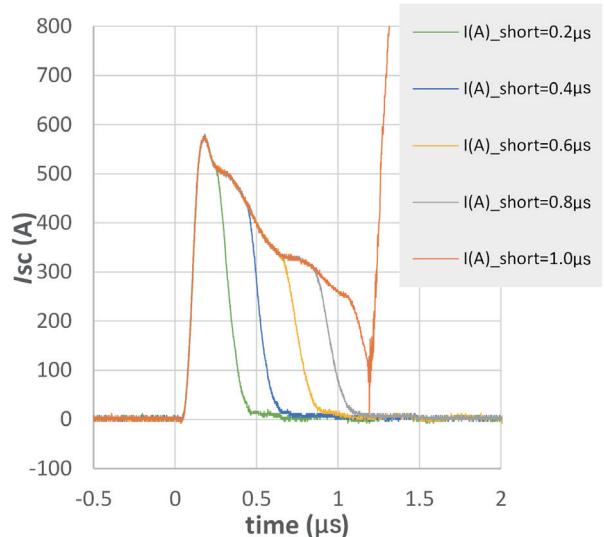

図5に4P駆動で高速スイッチングの回路構成で短絡した場合の短絡波形を示す。4P駆動では、200ns程度で短絡電流 $I_{sc}$ がピークに達し、約600Aまで増加している。その後、デバイスの発熱で急激に電流が減少し、短絡発生後1μsで破壊していることがわかる。

図5 4P構成の短絡電流波形

##### 5.2. 4P/3P切替駆動時の短絡保護と課題

図6に4P/3P駆動時の短絡波形を示す。切替手法は4P/3P同時駆動し、100ns後に4P駆動がオフとなり、3P駆動による短絡保護に切り換わる。

オン時の4P/3P駆動中に $di/dt$ が大きいため、ゲート電圧 $V_g$ の立ち上がりが遅れている。その結果、100nsの

図6 4P/3P切替駆動時の短絡電流波形

図7 改善後の4P/3P切替駆動のスイッチング測定波形

時点での $V_g=13V$ に留まっている。これは $di/dt$ が大きいことにより、3P駆動でのゲート電圧の立ち上がり抑制の効果である。

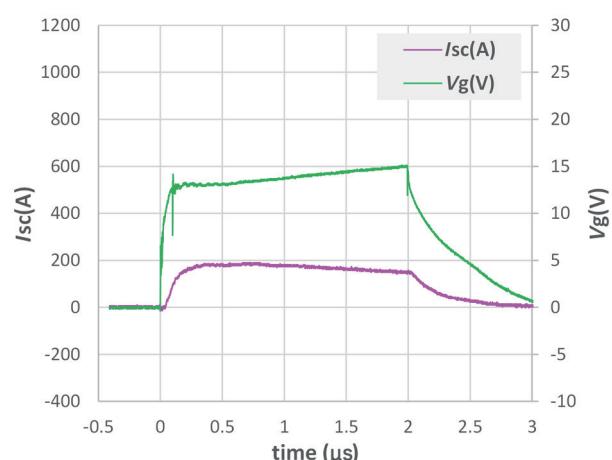

### 5.3. 改善後の4P/3P切替駆動時の短絡保護

前述の切替手法に対して、以下の変更を加えた。初期状態では4P駆動のみとする。一方、3P駆動は4P駆動のオフ時に駆動する。

図8に改善した4P/3P切替スイッチング測定波形を示す。定常駆動条件として $I_{ds}$ 電流を10Aに設定し、ハーフブリッジ回路のローサイドにてスイッチングを行った。

図8に定常駆動と同一の駆動条件下における4P/3P切替の短絡測定波形を示す。短絡時には大電流が瞬時に流れることでソースインダクタンス $L_s$ に負電位が発生

図8 改善後の4P/3P切替駆動の短絡測定波形

する。その際、ゲート電圧が十分に上昇する前に3Pへと切り替えておくことで、短絡時のゲート電圧 $V_g$ の上昇が抑制され、短絡電流 $I_{sc}$ が低減した。結果、4P駆動単体の場合よりも短絡耐量が大幅に向上了。

## 6. むすび

本研究ではSiC-MOSFETの高速スイッチングを維持し、短絡耐量を兼ね備えることの課題について検討し、4P/3P切替駆動により実証した。その結果、4P駆動では短絡耐量1μsのデバイスを4P/3P切替駆動によって2μs以上に延長することを達成した。

これらの結果を踏まえ、さらなる“誰もが簡便に超高速スイッチング性能を引き出せるSiC-MOSFET”の実現を目指していく。

## 7. 謝辞

この成果の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構（NEDO）の委託事業（JPNP 14004）の結果得られたものです。

## 参考文献

- Atsushi Yao, High-speed switching operation for a SiC CMOS and power module. IEICE Electronics Express, Vol. 18, No. 14, pp. 1–5, 2021.

- Atsushi Yao, High-speed and high-temperature switching operations of a SiC power MOSFET using a SiC CMOS gate driver installed inside a power module. Solid State Phenomena, Vol. 360, pp. 81–87, 9 2024.

- Mitsuo Okamoto, First Demonstration of a Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS

- Gate Buffer. 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 71–74, 2021.

- 4) Atsushi Yao, High-Speed and High-Temperature Switching Operations of a SiC Power MOSFET Using a SiC CMOS Gate Driver Installed inside a Power Module. Solid State Phenomena, Vol. 360, pp. 81–87, 2024.

- 5) Anas El Boubkari, CMOS Gate Driver with Integrated Ultra-Accurate and Fast Gate Charge Sensor for Robust and Ultra-Fast Short Circuit Detection of SiC power modules. In *2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, Vol. 2023-May, pp. 68–71. IEEE, may 2023.

- 6) Zhiqiang Wang, Design and Performance Evaluation of Overcurrent Protection Schemes for Silicon Carbide (SiC) Power MOSFETs. *IEEE Transactions on Industrial Electronics*, Vol. 61, No. 10, pp. 5570–5581, oct 2014.

- 7) Yuxiang Shi, Switching Characterization and Short-Circuit Protection of 1200 V SiC MOSFET T-Type Module in PV Inverter Application. *IEEE Transactions on Industrial Electronics*, Vol. 64, No. 11, pp. 9135–9143, 2017.