# サンケン技報

## Sanken Technical Report

2025.11, vol.57

# サンケン技報

— 第 57 卷

目次

論文および資料

- |                                                                   |                     |      |

|-------------------------------------------------------------------|---------------------|------|

| PSJGaN HEMTの開発                                                    | 伊藤 裕規               | 1-1  |

| パワエレ制御向けRISC-VマイコンMD6605の開発                                       | 山崎 尊永 宍戸 仁美         | 2-1  |

| 48V車載用MOSFET Module SAM4L10M30Z1の開発                               | 鈴木 誠司               | 3-1  |

| 車載向け1200V IPMシリーズ搭載パワーデバイスの開発                                     | 石井 孝明 山田 隼人         | 4-1  |

| スマートSiC-ICの高速駆動と短絡保護技術<br>～誰もが簡便に超高速スイッチング性能を<br>引き出せるSiC-MOSFET～ | 横井 魁人 町田 修          | 5-1  |

| 裏面漏光防止型赤外チップLEDの開発                                                | 野田 耕作               | 6-1  |

| RGB蛍光体を用いたRGB-LEDの開発                                              | 梅津 陽介               | 7-1  |

| 非絶縁コンバータ電源IC STR5M400シリーズの開発                                      | 伊藤 公一 塩津 興一<br>早川 章 | 8-1  |

| 非絶縁フライバック電源IC STR5A300シリーズの開発                                     | 田畠 鉄哉 塩津 興一<br>早川 章 | 9-1  |

| ドッキング接続時の汎用化パフォーマンスボード設計                                          | 木村 将吾 真尾 麻美         | 10-1 |

# PSJGaN HEMT の開発

## Development of PSJGaN HEMT

伊藤 裕規\*

Hironori Ito

**概要** (株) パウデックの独自技術であるPSJGaN技術を用い、デバイス試作をおこなった。PSJGaNは、分極により生じる電子および正孔によって形成される超接合構造による電界分布の均一化を利用することで、耐圧の向上および、電流コラプスの抑制効果が期待される。これらの効果を確認するため、試作およびデバイス評価をおこない、従来のGaN HEMTと比較を行ったところ、耐圧および電流コラプス特性で優位性を示唆するデータが得られた。さらにカスコード接続によるSW動作では、SJMOSよりも優れた特性を示す結果が得られた。引き続き、MOSFETや制御ICと組み合わせた統合型デバイスの製品化へ向けて検討を進めていく。

### 1. まえがき

表1に示すようにGaNの材料特性は、広いバンドギャップ、高電子移動度、高絶縁破壊電界を有しており、従来のSiデバイスと比較して優れた電力密度とスイッチング性能を発揮するデバイスを作ることが可能である。近年、電力変換装置の高効率化および小型化に対する要求が高まる中、パワー半導体デバイスとしてGaN(窒化ガリウム)HEMT(High Electron Mobility Transistor)に注目が集まっている。

表1. 各半導体材料の物性

|                             | Si   | 4H-SiC | GaN  |

|-----------------------------|------|--------|------|

| バンドギャップ (eV)                | 1.12 | 3.26   | 3.39 |

| 電子移動度 (cm <sup>2</sup> /Vs) | 1350 | 700    | 1500 |

| 絶縁破壊電界 (MV/cm)              | 0.3  | 3.0    | 3.3  |

| バリガ指数                       | 1    | 439    | 1128 |

ただし、高耐圧かつ低オン抵抗という相反する特性の両立は大きな課題であり、デバイス構造の革新が求められている。こうした課題に対する新たなアプローチとして、当社は(株)パウデック(サンケン電気(株)に吸収合併)の独自技術である分極超接合(Polarization Super Junction, PSJ)構造を導入したGaN HEMT(PSJGaN)の

開発をおこなっている。PSJGaNは、GaN系材料に特有の分極効果を活用し、スーパージャンクション構造に類似した電界緩和を実現することで、低オン抵抗と高耐圧の両立を可能にする。さらに、支持基板にサファイアを用いることで、従来のシリコンを用いた場合(GaN on Si)に比べ、エピ厚削減によるコスト低減と、GaN on Siでは困難である1200V以上の超高耐圧デバイスの実現が可能となる。一方で、絶縁基板であるため、電流コラプス特性においては不利になる懸念がある。

本報告では、PSJGaNの設計、試作、評価を通じて、その性能と応用展望を明らかにし、実用化に向けた有効性を示す。

### 2. PSJGaNの構造と特徴

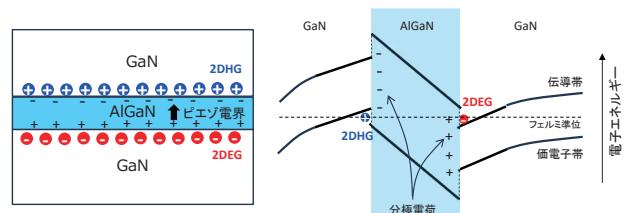

図1に示すようにGaN/AlGaN/GaN積層構造を形成すると、圧電分極により発生するAlGaN中の内部電界(ピエゾ電界)により、AlGaN上のGaN界面付近には正孔が、AlGaN下のGaN界面付近には電子が発生する。

\*技術開発本部プロセス技術統括部

GaNデバイス開発部 GaNデバイス開発課

図1. GaN/AlGaN/GaN構造とエネルギー-band図

発生した電子と正孔は平面状に広がることから二次元正孔ガス (two dimensional hall gas, 2DHG) と二次元電子ガス (two dimensional electron gas, 2DEG) と呼ばれ、AlGaN を介した分極超接合構造を形成している<sup>1)</sup>。

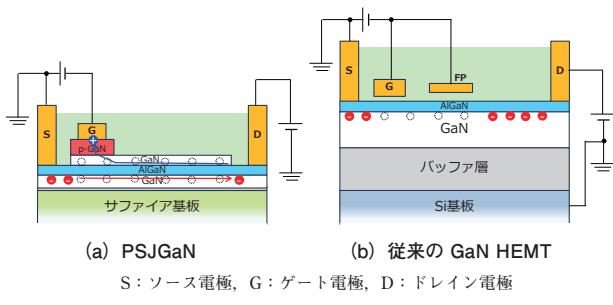

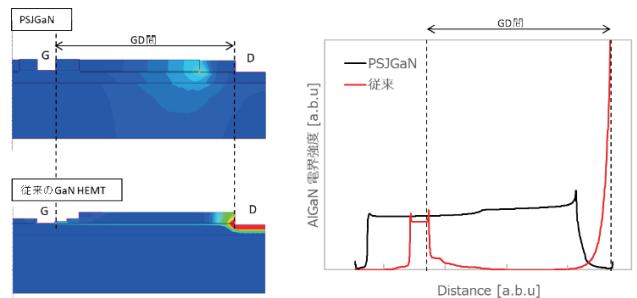

この2DEGは電荷密度が高く、かつ移動度も高いため、オン抵抗が低いデバイスを実現することができる。さらに、2DHGを利用し、PSJ構造をとることで高耐圧デバイスが実現できる。図2にオフ状態におけるデバイス構造を示す。図2(a)に示すようにPSJGaNはゲート電極に負バイアスを印加することにより、上部GaN領域の2DHGの正孔が引き抜かれ、それに伴い2DEGの電子が空乏化する。その結果、PSJ構造の領域(PSJ領域)全体で一様な電界分布を持ち、高耐圧にすることができる。ただし、2DHGによりゲート駆動させるため、オン時にはゲートに正のバイアスを印可する必要がある。

図2. オフ状態におけるキャリア分布イメージ

一方、図2(b)に示すように、従来のGaN HEMTはGaN on Siを用い、ゲート端への電界集中による耐圧低下をフィールドプレート(FP)を備えることで改善している。しかしながら、ドレイン電極とSi基板間に高電圧が生じることから、現状では800V以下の使用に限定されている。

また、GaN HEMTでは電流コラプスと呼ばれる、スイッチング動作中に電流が流れにくくなる現象があり、オン抵抗の増加を引き起こす。電流コラプスは、オフ時にゲート端部の電界集中により、AlGaN層や層間膜界面等に電子が捕獲され、仮想ゲートを作り出すことにより引き起こされる。対策としては、電界集中を緩和するためのFP構造を用いるなどの手法がとられている。一方、PSJGaNでは一様な電界分布が実現できることから、従来のGaN HEMTよりも電流コラプスの発生が抑制されることが期待される。

### 3. 試作評価結果

#### 3.1. 耐圧特性

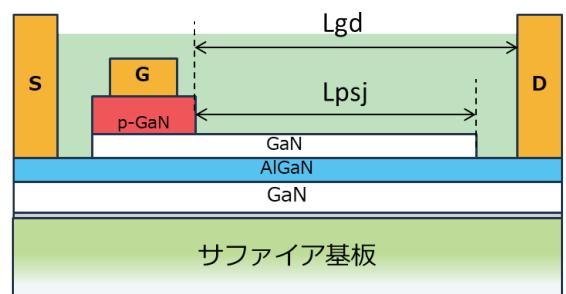

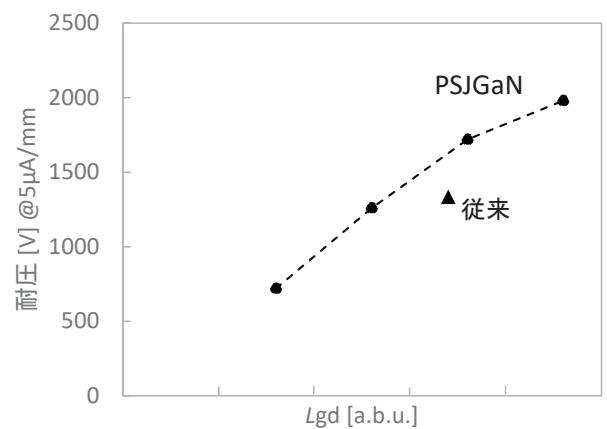

図3におけるPSJ構造の長さ( $L_{psj}$ )を変化させ、耐圧特性を評価した。 $L_{psj}$ が長くなるにつれ耐圧も大きくなる傾向が得られ、耐圧のGD間距離( $L_{gd}$ )依存性は図4となる。従来のGaN HEMTと比較すると、PSJGaNがより高耐圧を示しており、優位性を示唆する結果が得られた。

図3. PSJGaN の断面図

図4.  $L_{psj}$ を変化させた PSJGaN の耐圧特性

#### 3.2. 電流コラプス特性

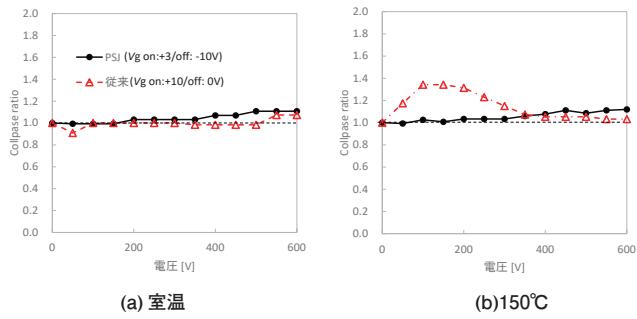

電流コラプス特性の定量評価には、パルスIV測定法を用いた。ゲート電圧をon/offの2値で切り替えるパルス信号を用い、ドレイン側には定電圧を印加した。パルス幅は25μsとし、オン後20μsのドレイン電流および電圧を測定し、電流コラプスを評価した。

評価指標としては、初期状態のオン抵抗 $R_0$ に対するパルス印加時のオン抵抗 $R_{on}$ (dynamic)の相対変化率を電流コラプス指標(collapse ratio)として定義した。この指標が1に近いほど電流コラプスが小さくなる。

$$\{\text{collapse ratio}\} = R_{on}(\text{dynamic}) / R_0$$

図 5. PSJGaN の電流コラプス特性

試作したPSJGaNおよび従来のGaN HEMTの電流コラプス特性を図5に示す。

従来のGaN HEMTと比較すると、サファイア基板を使用しているにもかかわらず、同等以上の電流コラプス特性が得られ、PSJ構造による効果が示された。

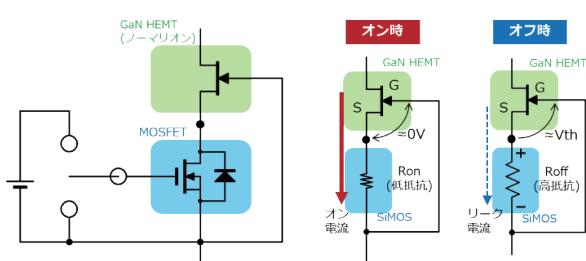

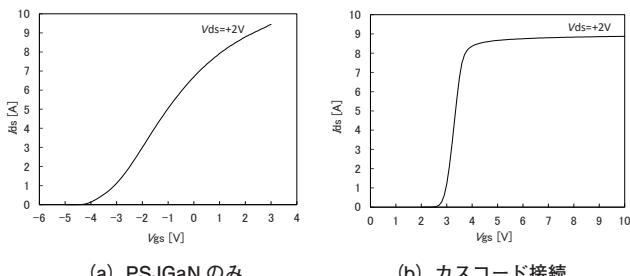

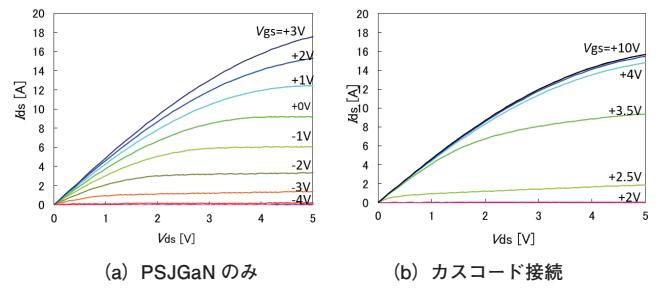

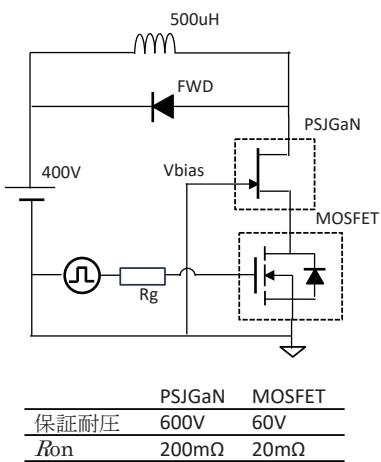

### 3.3. カスコード接続の動的特性

図6に示すように、ノーマリオン型のGaN HEMTとMOSFETを直列接続し、さらにGaN HEMTのゲートを接地（カスコード接続）することで、従来のノーマリオフデバイスと同等に扱うことができる。図7、図8にノーマリオン型のPSJGaNをカスコード接続（PSJGaNカスコード）した際に得られた特性を示す。

図 6. ノーマリオン型 GaN HEMT のカスコード接続

図 7. 伝達特性

図 8.  $I$ - $V$  特性

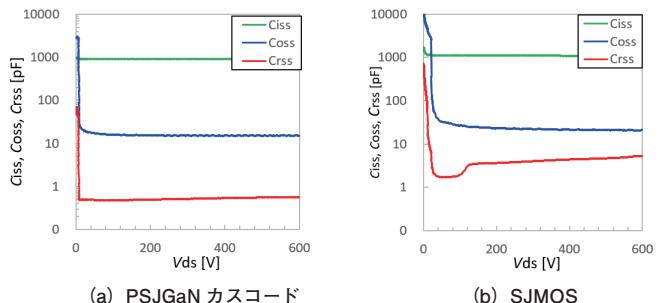

PSJGaNは、PSJ領域全体をゲート駆動するため、ゲート電荷量（ $Q_g$ ）が従来のGaN HEMTに比べ大きくなってしまう。しかし、カスコード接続にすることで、PSJGaNのゲートが接地されMOSFETを駆動することになるので、これによる容量特性やSW速度への悪影響は軽減されることが期待できる。図9にPSJGaNカスコードとスーパージャンクションMOSFET（SJMOS）の容量特性を示す。Coss, CrssにおいてSJMOSよりも優れた容量特性を示すことが確認できた。

図 9. 容量特性

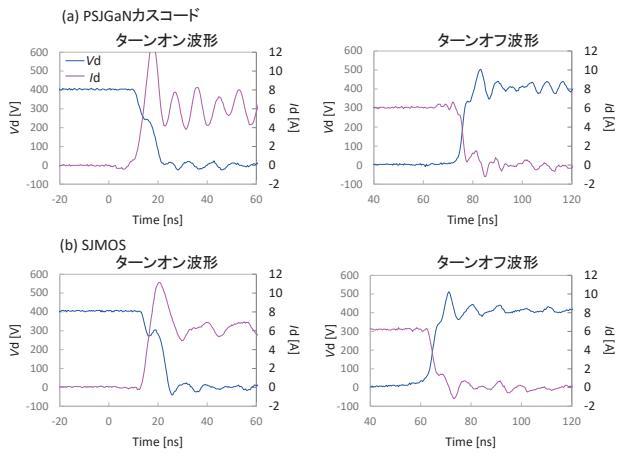

次に、L負荷ハードスイッチング条件下でスイッチング特性を評価した（図10）。評価結果の一例として、400V, 6A動作時のSW波形を図11に示す。

図 10. PSJGaN カスコードの SW 評価回路

図 11. (a) PSJGaN カスコードおよび (b) SJMOS の SW 波形

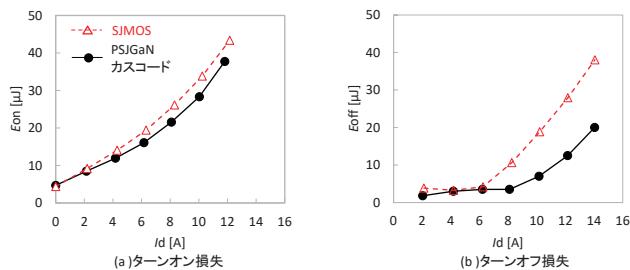

これらのSW特性の評価結果から得られたPSJGaNカスコードおよびSJMOSのターンオン、ターンオフにおけるエネルギー損失は、図12のようになる。この結果から、SW特性におけるPSJGaNカスコードのSJMOSに対する優位性が示された。

図 12. PSJGaN カスコードおよび SJMOS の SW エネルギー損失

#### 4. デバイスシミュレーション検討状況

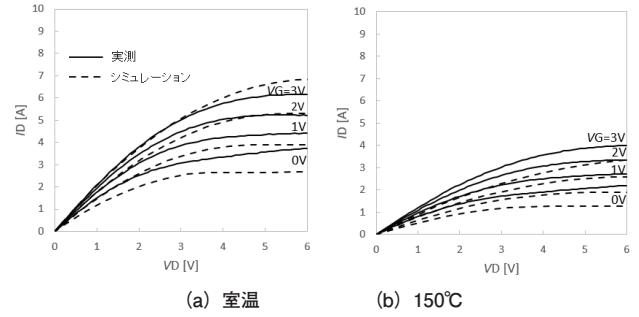

現在、TCADを用いたPSJGaNのデバイスシミュレーションモデルの検討を行っている。図13に示すように、I-V特性においては、室温では比較的良好な再現性が得られているが、高温ではまだ乖離が見られる。一方オフ動作時における電界強度分布の計算結果を図14に示す。FPを有する従来のGaN HEMTに比べ、より均一な電界強度分布を示す結果が得られている。今後は物理モデルの妥当性検証など、シミュレーションモデルの精度向上を進め、設計に活用していく予定である。

図 13. PSJGaN の I-V 特性

図 14. オフ時高電圧印可時の電界強度分布シミュレーション結果

#### 5. むすび

本稿では、電力変換ロスの小さいデバイスが作製可能な材料であるGaNを用いたPSJGaNについて紹介した。試作評価を行い、従来のGaN HEMTに対する耐圧、電流コラップスにおける優位性を示した。さらに、PSJGaNカスコードにおいてSJMOSに対する容量特性、SW特性の優位性を示した。PSJGaNのさらなる性能改善に加え、PSJGaNの性能を最大限に引き出すための駆動用ICの開発も同時に進めていく。また、TCADを用いたデバイスシミュレーションの検討をおこなっており、デバイス設計に活用することで、統合型デバイスの製品化へ向けて開発を進めていく。

#### 参考資料

- (1) 佐藤他, 豊田合成技報, Vol. 63, p. 41-45 (2021)

# パワエレ制御向け RISC-V マイコン MD6605 の開発

## RISC-V Microcontroller MD6605 for Power Electronics Control

山崎 尊永\*

Takanaga Yamazaki

宍戸 仁美\*\*

Hitomi Shishido

**概要** サンケン電気は電源やモータなどの先進的なパワエレ制御システム向けに、RISC-V CPUコア、22nm超低リークプロセス、およびReRAM不揮発メモリ技術を使用したマイコンMD6605を開発した。MD6605はRISC-V CPUコアに加え、デジタルフィルタ演算用DSPと高速タスク・スイッチが可能なEPU(Event Processing Unit)によるヘテロジニアスマルチコア構成を採用しており、パワエレ制御システムの高効率化と高機能化を実現する。MD6605の製造には、マイコンとしては最先端の22nm超低リーク・プロセス技術と不揮発メモリReRAM(抵抗変化型メモリ)を採用した。サンケン電気は、MD6605を活用し、各種パワエレ制御システム向けの製品群を積極的に展開する予定である。

### 1. まえがき

近年の脱炭素に向けたGX(Green Transformation)活動推進の中で、電子機器の省エネ性能が従来以上に厳しく求められている。特に生成AIの普及に伴い増加するデータセンターではその電力消費量の多さから、パワーデリバリ経路の電力ロスの削減、すなわち高効率化が強く求められている。それだけではなく、世の中に広く普及する家電製品や産業機器などの電源システムにも絶え間ない高効率化が要求されている。さらに最近のAIプロセッサや高性能SoC(System on a Chip)は超微細プロセスの採用と動作クロック周波数の向上から、電源の低電圧化と大電流化が著しく、そうした厳しい条件のもとで高精度な電源が要求されている。

こうした高効率かつ高精度な電源の実現方法として、サンケン電気は電源のデジタル制御方式に長く取り組んでおり、最近のより厳しい要求にも応えられる先進型のデジタル電源制御向けマイコンMD6605を開発した。

MD6605は電源制御だけでなく、白物家電や専業機器に広く用いられるブラシレスDC(BLDC)モータ制御にも活用でき、その効率向上を実現するとともに、開発を容易化するパラメータ自動調整機能も提供する。

\* 技術開発本部パワーデバイス開発統括部

システム開発部

\*\* 技術開発本部パワーデバイス開発統括部

システム開発部 デジタル開発課

### 2. 電源のデジタル制御とそのメリット

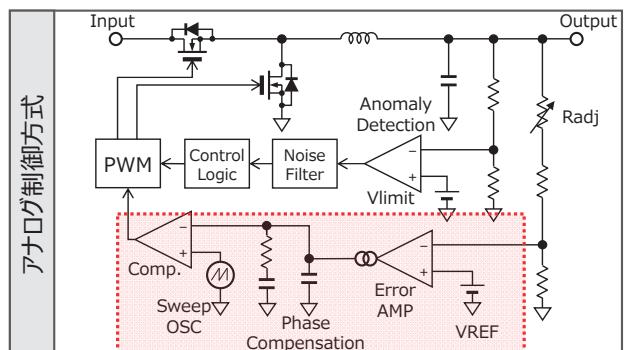

電源は図1に示すアナログ方式で制御されることが多い。古くから使われる実績のある方式で、比較的小規模のハードウェアで実現できる。一方、抵抗や容量による線形な位相補償のため特性パラメータ範囲に制限があり、コンバータのトポロジが固定化され、また最適制御の効率改善には複雑なハードウェアが必要となる。ノイズ対策はハードウェア手法のみのため、ノイズ対策用追加部品が多数必要である。外部との通信やインテリジェント機能の実現も困難である。特に高出力電源では、全負荷領域での損失低減が難しいため大きなヒートシンクが必要となり、システムコストが増大するなどのデメリットがある。

図1 電源(降圧Buckコンバータ)のアナログ制御方式の例

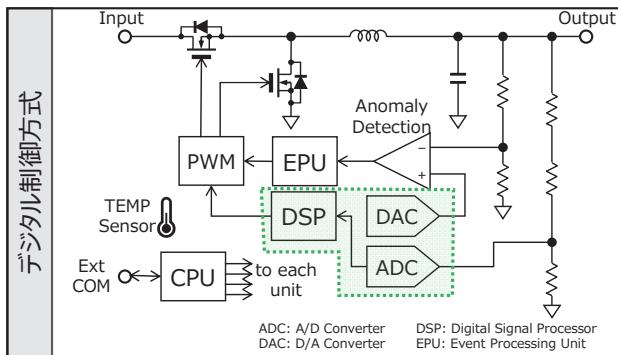

図2 電源（降圧 Buck コンバータ）のデジタル制御方式の例

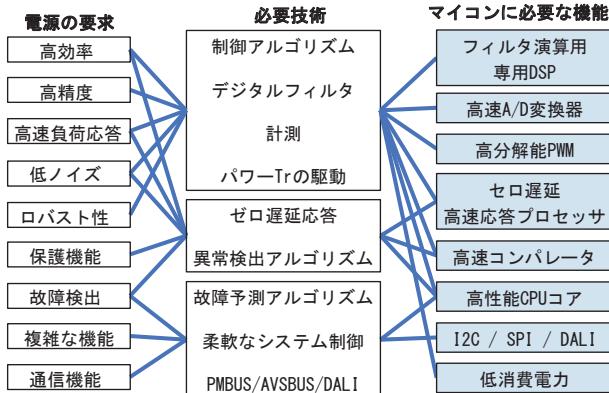

図2はデジタル制御方式の電源を示す。アナログでは実現できない数値演算による線形または非線形なフレキシブル制御を実現する。DSP (Digital Signal Processor)などの演算器を使用するため、アナログ方式よりはハードウェア量は増える。一方で、任意の電源トポロジに対応可能、高度な制御アルゴリズムにより高精度かつ高速応答性を実現、負荷状態などに応じた最適制御により高効率を実現、ソフトウェアによりノイズ対策を臨機応変に対策可能、外部との通信とインテリジェント機能を実現、高効率化によるヒートシンクの削減とノイズ対策部品の削減、特に高出力・高精度電源においてシステムコストを削減可能、などのメリットがある。このため、サーバセンター向け電源や大型AV機器などの高出力電源や、高性能AIプロセッサ向けの低電圧・大電流電源にはデジタル制御方式を採用することが多い。

以下、デジタル制御方式のメリットのいくつかを具体的に説明する。

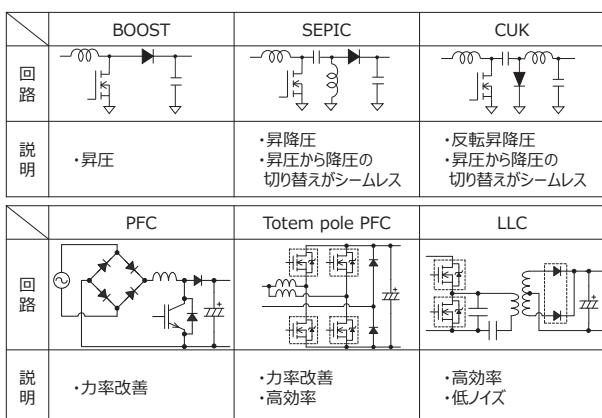

### (1) 任意の電源トポロジに対応可能

デジタル電源制御は基本的にソフトウェアによる制御であり、制御器のハードウェアを基本的に変えることなく、図2の降圧Buckコンバータに加え図3に示す様々な電源トポロジに対応可能である。

図3 デジタル電源が対応できる様々な電源トポロジ

### (2) 高精度な出力電圧を実現可能

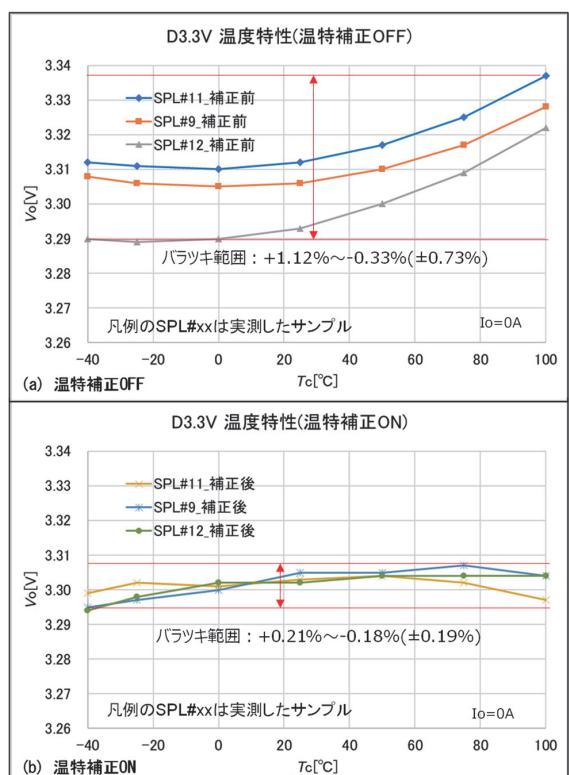

温度センサーで周囲温度をリアルタイムに検出して補正をかけることで、図4に示すような温度変動特性が極めて少ない電源を実現できる。

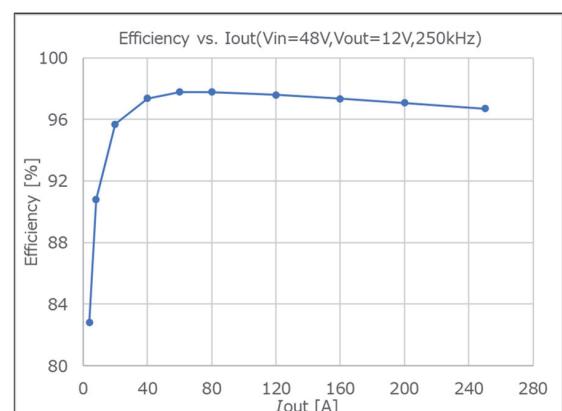

### (3) 全負荷領域での効率向上

一般に電源は軽負荷領域で効率が低下する傾向にあるが、デジタル制御では負荷状態に応じたきめ細かい最適制御により全負荷領域での効率向上を図れる。例えば、低負荷領域ではスイッチング周波数を低下させるきめ細かい制御を行う。図5はデジタル制御による高効率電源（DC-DC中間バスコンバータ）の効率の例である。

図4 デジタル制御による温度補正の効果

図5 デジタル制御による高効率電源（DC-DC）の効率

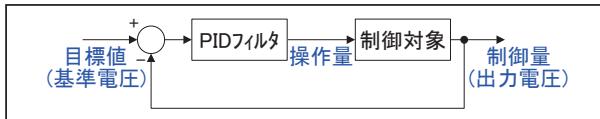

#### (4) 高度な現代制御を実装可能

図6はアナログ制御方式で多く用いられるPID制御(古典制御)のブロック図を示す。目標値と出力電圧が等しくなるようにフィルタを介してフィードバック制御を行う。大電力で負荷変動が激しく、高精度な出力電圧を要求する電源系では、本方式は目標を達成しにくい。

図6 一般的なPID制御(古典制御)

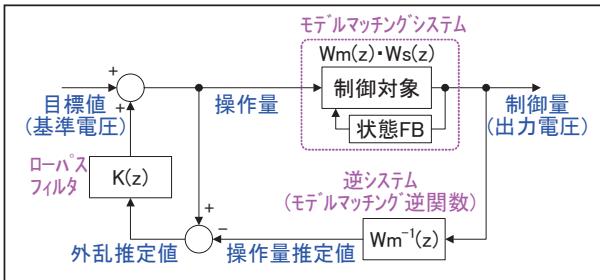

これを解決する手段が図7に示す近似的2自由度制御(現代制御)である。外乱推定値を目標値に加算することで外乱を打ち消すように制御する。数値演算が必要であり、デジタル制御でないと実現できない。

図7 近似的2自由度制御(現代制御)

近似的2自由度制御の効果を図8に示す。目標値応答特性と外乱応答特性を同時に改善できる。本方式は、大規模AIプロセッサのような低電圧・高精度(0.5V~0.9V, ±20mV)かつ大電流(~100A以上)な負荷デバイスの電源の制御方式として有効である。

図8 近似的2自由度制御の効果

#### (5) 故障判定・故障予測が可能

デジタル制御を使うことで、電源の異常の予兆を早期に検出することが可能になる。

- FFT処理：電源出力電圧の波形をA/D変換器でサンプリングした結果を、FFT処理して周波数成分の変化から異常の予兆を検出する。

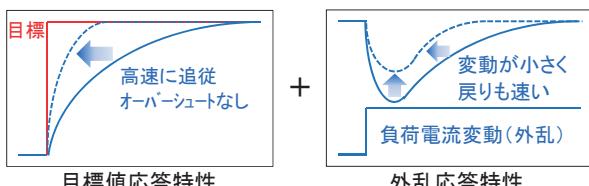

- エッジAIの活用：PWMのデューティ指令値のリアル

図9 エッジAIによる故障予測

タイムな時系列パターンから、エッジAIが学習データをもとにして異常の予兆を検出する(図9)。

#### (6) インテリジェント電源の実現

マイコン(CPU)を使うデジタル制御方式では、複雑なシステム処理が可能になる。

- 多出力電源のシーケンス制御：複数の電源出力レーンの、立上げ・立下げシーケンスを任意に設定可能。

- 通信制御：外部との通信で出力電圧の変更、ON/OFF制御、電流制限値の変更、電源動作状態のモニタなどが可能(PMBUS, AVSBUS)。

- 運転ログ管理：電源の動作状況や異常検出状況を不揮発メモリにログとして記録可能。

- 自己診断：マイコンチップそのものの自己診断、および電源システム全体の自己診断が可能。異常があれば、外部にレポートするか、または自動的に遮断可能。

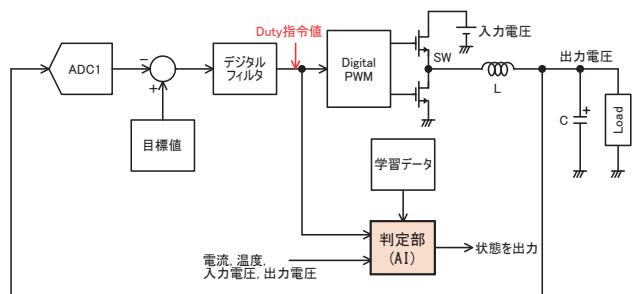

### 3. 電源制御用マイコンに必要な機能

上記に示したデジタル制御をフレキシブルに実現するには、専用マイコンが必要である(図10)。電源制御は、制御対象が電気回路であり応答性が速いため、メカを相手にするモータ制御よりは格段に制御周期が短くなる。このため、高速DSPによる演算処理能力と高速A/D変換器が必須である。またPWMキャリア周波数も向上するためPWMタイマの高分解能化も欠かせない。くわえて、電源システムには、例えば、過電圧・過電流発生時の対応、電圧・電流のゼロクロス時の応答、異常や故障の監視と検出など、各イベントに対して高速に応答できる機能が必須で、シンプルな動作はハードウェアにより直接対応できるが、フレキシビリティが必要な複雑なケースは、CPUの割込み処理だとレイテンシが長すぎるため、特別な高速応答プロセッサが必要となる。このため、電源制御用マイコンは、単一のCPUコアだけでなく、DSPコア、高速応答プロセッサから構成されるヘテロジニアスマルチコアシステムが必要である。

図10 電源制御用マイコンに必要な機能

#### 4. パワエレ制御用マイコンMD6605

サンケン電気は、上記で説明した電源制御マイコンの次世代品としてMD6605を開発した。モータと電源を同時に制御するアプリケーションも視野に入れ、モータ制御に必要な機能も搭載し、総合的なパワエレ制御用マイコンとして開発を進めた。

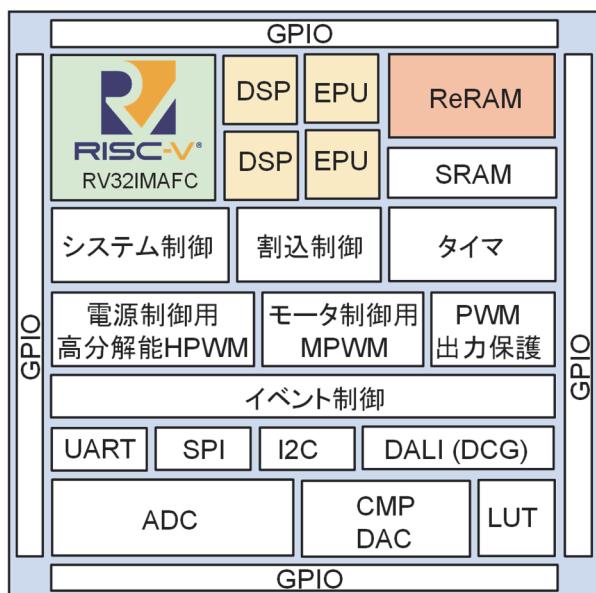

図11 MD6605のブロック図

図11にMD6605のブロック図を表1に仕様一覧を示す。以下、MD6605の主要な特長について説明する。

#### 5. ヘテロジニアスマルチコア

前述したとおり、MD6605は高効率・高精度なパワエレ制御のため異なる特長を持つ下記3種のコアにより並列処理するヘテロジニアスマルチコア構成を採用した。

- (1) CPU (Central Processing Unit) : 通信制御、運転記録、故障診断、非定常時の制御など、システム

表1 MD6605の仕様概要

| 項目         | 仕様                                    |

|------------|---------------------------------------|

| RISC-V CPU | 命令セットRV32IMAF、デバッガI/F=cJTAG           |

| DSP        | 2ユニット 浮動小数点演算                         |

| EPU        | 2ユニット 高速応答プロセッサ                       |

| ROM        | ReRAM(抵抗変化型メモリ) 128KB+ECC             |

| RAM        | 8KB+ECC                               |

| 割込み        | 64要因 優先レベル×16 周期割込みタイマ                |

| システム制御     | 内蔵発振器 PLL 低電力制御 機能安全                  |

| タイマ        | 汎用16ビットタイマ 低電力タイマ WDT                 |

| HPWM(電源用)  | 高分解能PWM 出力×8                          |

| MPWM(モータ用) | 相補PWM 出力×6                            |

| イベント制御     | チップ内イベントスイッチ網 イベント加工                  |

| シリアル通信     | UART×3ch SPI×1ch I2C×1ch DALI(DCG)    |

| ADC        | 3ユニット 12ビット 3MSPS 8入力/ユニット            |

| コンバーティ     | 6ユニット 10ビットDAC付き 出力論理演算               |

| GPIO       | 汎用入出力、全端子に任意周辺機能設定可                   |

| 動作条件       | 66.6MHz, V <sub>DD</sub> =3.3V 単一電源動作 |

| 製造プロセス     | TSMC 22nm ULLプロセス ReRAM混載             |

全体を制御する役割を担う。プログラム規模が増えており、高性能32ビットCPUが必要である。デジタルフィルタ処理やモータのベクトル制御では、固定小数点演算を使うとダイナミックレンジの低下やオーバフロー・アンダーフローの対策が必要なため、演算には浮動小数点処理が要求される。このためCPUにも浮動小数点演算命令の実装が必要である。

- (2) DSP (Digital Signal Processor) : パワエレ制御のデジタルフィルタ演算を直接担うコアで、制御サンプリング周波数の向上に伴い高速な演算処理が必要である。整数演算に加えて浮動小数点演算でも、積和命令を1サイクルで処理する性能が必要である。

- (3) EPU (Event Processing Unit) : コンバータ回路の電流や電圧がゼロクロスしたときのコンバータの反転イベントへの応答、A/D変換器の変換終了やPWMタイミングの時間イベントに伴うデータ転送とデータ演算加工など、パワエレ制御には多くのイベントに対する高速応答性が要求される。これをCPUの割込み処理で実現しようとすると汎用レジスタの退避などによるレイテンシが大きく間に合わない。このため複数のイベントに応答してゼロ時間でタスク切替え対応できる専用プロセッサが必要である。

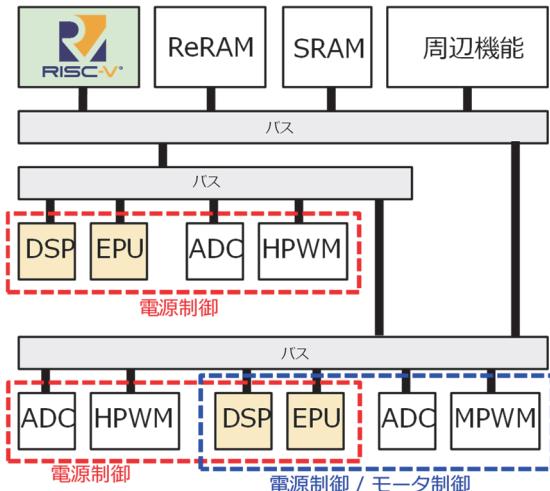

図12にMD6605のヘテロジニアスマルチコア構成を示す。パワエレ制御において、DSPとEPUは頻繁にA/D

変換器とPWMタイマと連携するので、それらを専用バスで接続した。DSPとEPUはそれぞれ2ユニット搭載し、CPUとあわせて合計5個のコアで並列処理を行う。

並列処理化により動作周波数を上げることなくシステム性能を向上できる。MD6605の動作周波数は66.6MHzであるが、ヘテロジニアス構造により浮動小数点演算性能は400MFLOPS、整数演算性能は600MOPSに達する。

図12 MD6605のヘテロジニアスマルチコアの構成

## 6. 32ビットRISC-V CPUコアの搭載

MD6605のメインCPUとしては、最新アーキテクチャであるRISC-V<sup>\*</sup>を採用した。RISC-Vは命令セットアーキテクチャがオープンに公開されており、誰もが自由に設計することができる。市販のIPコアもあるが、サンケン電気はこれを独自に開発した。RISC-Vは命令セットがシンプルで、処理性能も高くコード高率も高い。開発環境などアーキテクチャを取り巻くエコシステムも充実してきており、今後の普及が期待されている。表2にMD6605に搭載したRISC-V CPUコアの仕様を示す。

表2 MD6605に搭載したRISC-V CPUコアの仕様

| 項目            | 仕様                                              |

|---------------|-------------------------------------------------|

| 命令セット         | RV32IMAF(C(高速乗算、高速浮動小数点演算))                     |

| パイプライン        | 整数:3~5ステージ 浮動小数点:5~6ステージ                        |

| 整数乗算          | 1cyc                                            |

| 浮動小数点         | 加算/減算/乗算/積和: 1cyc                               |

| デバッガ          | 2-wire cJTAG ハードウェアブレーク×4                       |

| 割込み           | 標準×3本 + 拡張×64本(優先レベル×16)                        |

| Dhrystone 2.1 | 1.6 DMIPS/MHz                                   |

| Coremark 1.0  | 3.30 Coremark/MHz                               |

| 開発環境          | ・MD Studio (Eclipseベース)<br>・3rd Party製開発環境(計画中) |

\* RISC-VはRISC-V InternationalとKrsti Asanović氏の登録商標である。

## 7. 高機能化したDSPコアとEPUコア

MD6605は独自開発のDSPとEPUを2ユニットずつ搭載している。表3にDSPとEPUの仕様を示す。

表3 DSPとEPUの仕様

| 項目             | DSP                                               | EPU              |

|----------------|---------------------------------------------------|------------------|

| 用途             | CPUと独立した高速演算                                      | パワエレ制御イベントへの高速応答 |

| 搭載コア数          | 2コア                                               | 2コア              |

| スレッド数          | 1スレッド                                             | 2スレッド            |

| 命令セット          | 16ビット固定長                                          |                  |

| パイプライン         | 3~5段                                              |                  |

| イベント応答         | イベント待ち、タイマ待ち、イベント出力<br>(リアルタイム応用性能向上)             |                  |

| スレッド制御         | なし                                                | ゼロ時間スレッド切替       |

| 32ビット<br>固定小数点 | 加算/減算/乗算/積和: 1cyc<br>除算: 8cyc (Newton-Raphson)    |                  |

| 32ビット<br>浮動小数点 | 加算/減算/乗算/積和: 1cyc<br>除算: 8cyc<br>(Newton-Raphson) | なし               |

| デバッグ           | ステップ動作/PCブレーク/データ・ブレーク/<br>ソフトウェア・ブレーク            |                  |

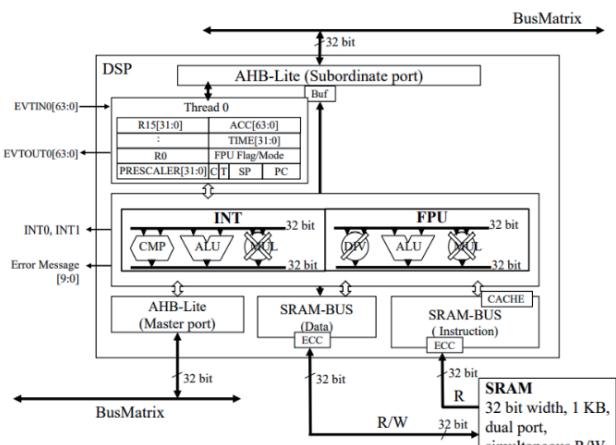

DSPは32ビット浮動小数点および固定小数点の演算ユニットを持つプロセッサである。図13にDSPのブロック図を示す。DSPはCPUを介さずにイベント入力に応じて演算・論理処理・データ転送を実行できる。浮動小数点、固定小数点とともに加減乗算や積和演算を1サイクルで処理でき、位相補償演算、ベクトル制御など高精度な制御にも対応可能である。ニュートン・ラプソン法による除算は8サイクルで実行可能である。

図13 DSPのブロック図

次にEPUを紹介する。DSPとEPUは浮動小数点器の有無とスレッド数が異なる（表3参照）。

EPUは、2つのスレッド、1つの固定小数点の演算ユニットを持つプロセッサである。スレッドは、汎用レジスタ16個やタイマ、プログラムカウンタなどを持つ。EPUは、スレッドに割り当てられたタスク（プログラム）

を1つの演算ユニットで優先順位に従って順番に実行する。前述したとおり、パワエレ制御には多くのイベントに対する高速応答性が要求される。EPUはイベント信号を受信すると瞬時に、そのイベントに対応するタスクを実行することが可能である。

次にイベント応答によるタスク切替えについて説明する。スレッドが汎用レジスタなどのリソースを持つことで、タスク切替え時にも、そのタスクが使用中のスレッドのデータはそのまま保持される。そのため、データの退避が不要である。CPUのように割込み時にデータを退避・復帰する操作が不要であるため、EPUはゼロ時間でのタスク切替えが可能である。

ゼロ時間でのタスク切替えの例を図14で示す。この例では優先順位に固定優先（常にスレッド0 > スレッド1の優先順位）を選択している。スレッド0が起動前やイベント待ちの状態のときには、スレッド1の命令を実行する。イベント待ち状態のスレッド0にイベントが入力された場合には、スレッド0の命令を実行する。このスレッド切替え時には、ゼロ時間での切替えがおこなわれる。

図14 ゼロ時間タスク切替え

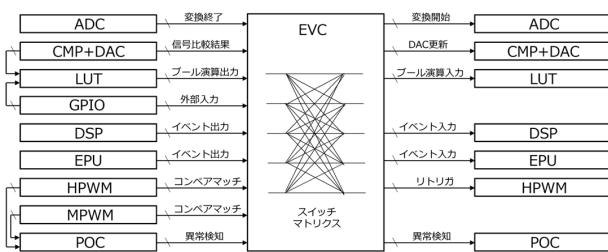

EPUの特長の一つは、イベント入出力を命令により制御可能であることである。ここでMD6605のチップ内イベント接続についても紹介する。パワエレ制御用マイコンには、各モジュールがタイミングを合わせた同期動作が要求される。それを実現するのが、各モジュールに入出力されるイベントである。図15のようにMD6605のチップ内には、A/D変換終了やコンパレータ反転など、多種類のイベント信号が行き交っている。イベント信号の接続は、EVC(Event Controller)により自由に選択でき、各モジュールが同期動作することができる。

図15 チップ内イベント接続

## 8. 周辺機能とその特徴

MD6605に搭載した主要な周辺機能を紹介する。

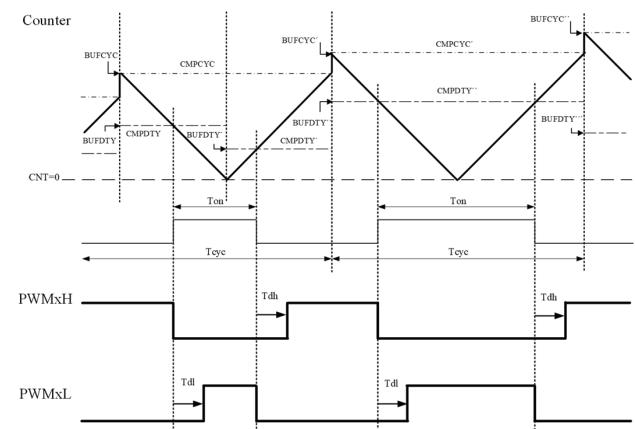

### (1) HPWM：高分解能 PWM

HPWMは、電源制御用の高分解能PWMである。前述のとおり、電源制御では制御周期が短く、PWMキャリア周波数の向上のため高分解能化が重要である。MD6605に搭載されているHPWMは分解能が1ns未満であり、細やかなデューティの調整が可能となる。

HPWMは16ビットカウンタを持ち、カウンタ値と比較値との比較により、周期やデューティを決定する。また、カウンタはアップカウントモードとアップ・ダウンカウントモードの両方をサポートしている。

さらに、HPWMは電源制御における過電圧・過電流発生時の保護動作や、電圧・電流のゼロクロス時の応答を可能とするリトリガ機能を搭載している。このリトリガ機能により、イベントに応じてカウンタ動作をリアルタイムで変更することで、HPWMの停止やデューティカット、サイクルカットを行うことができる。

### (2) MPWM：モータ用 PWM

MPWMは、モータ制御用のPWMである。32ビットアップダウンカウンタを持ち、6本（3ペア）のPWM信号を生成できる。

図16のように、MPWMの信号生成には、モータ制御においてノイズ耐性が高く、精密な制御に適したカウントアップとダウンを繰り返すセンターライメント方式を採用している。また、デューティ範囲は0%～100%で調整可能であり、スイッチの同時ONを防ぐためのデットタイム機能を備えている。

図16 MPWM のカウンタと出力波形

### (3) POC (PWM Output Controller) : PWM出力コントローラ

POCは、コンパレータやルックアップテーブルの出力信号の変化やEVCからのイベントに応じて、PWM出力端子をあらかじめ設定した端子状態に固定する。電源の異常状態に対応する際には、PWMの制御よりも先にPWM出力を固定することで、最短時間での保護処理を実現する。MD6605はPOCを2ユニット搭載しており、POC0がHPWMの出力制御、POC1はMPWMの出力制御をおこなう。

### (4) A/D変換器

MD6605に搭載したA/D変換器は、12ビットの分解能をもつ逐次比較型である。3ユニット搭載されており、電源制御では3コンバータの制御が可能であり、モータ制御では3相電流の同時サンプリングが可能である。

パワエレ制御における制御サンプリング周波数の向上に伴い、高速なA/D変換器が求められている。本A/D変換器は、小型化、高速化、低消費電力を実現しており、クロック周波数が66MHzのとき、最高変換速度は3MSPSである。

### (5) LPTMR：低電力タイマ

LPTMRは低電力モードから復帰するためのタイマである。パワエレ制御では、システム全体がアイドル状態のときなど、特定の条件下でマイコンを低電力モードに移行させる場合がある。MD6605には、以下の低電力モードと、それぞれの復帰要因がある。

- ①スリープモード：割込みで復帰

- ②スタンバイモード：GPIO割込み、CMPレベル割込み、LPTMR、DCG（DALI Control Gear）で復帰

- \* ノーマルスタンバイ（GPIO、CMP）

- \* LPTMRスタンバイ（GPIO、CMP、LPTMR）

- \* DCGスタンバイ（GPIO、CMP、DCG）

低電力モードの使用においては、一定時間の低電力モードの後に復帰し、タスクを実行するという処理が行われることがある。LPTMRはこのような周期的な低電力モードからの復帰に使用することができる。

## 9. TSMC 22nmプロセスとReRAMの採用

MD6605は、マイコンとしては最先端となる22nm ULL (Ultra Low Leak) プロセスとReRAM（抵抗変化型メモリ）を採用し台湾TSMCで製造する。

22nmプロセスは、①チップサイズ縮小によるコスト

低減、②ULLプロセスとHVT (High Vt) トランジスタによる消費電力の低減、③プレーナプロセスの最終世代であり将来の長期供給が確実、を理由として採用した。

プログラムを格納する不揮発メモリとしてはReRAMを採用した。22nm世代では下地構造が複雑なFLASHメモリの実装は困難であり、配線層に記憶材料を構築するシンプルな構造のReRAMが好適である。ReRAMは、①追加マスク枚数が少なくコスト面で有利、②FLASHメモリのようなブロック消去をせずにカラム単位での上書きができるためユーザの使い勝手が向上、③信頼性（データ保持特性）はFLASHメモリと同等以上の実力、という特長がある。

微細プロセス向けの不揮発メモリの選択肢としては、MRAM（磁気抵抗メモリ）もあるが、コスト優位性の面から車載向けを含めReRAMの採用例が増えている。

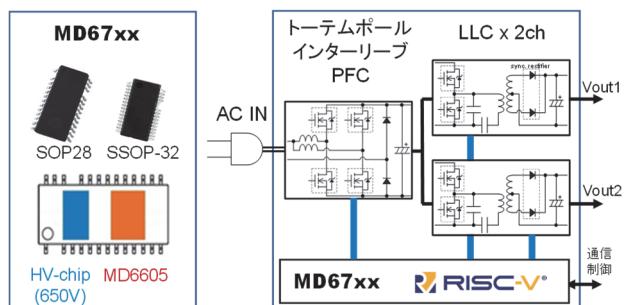

## 10. AC-DC電源IC製品への展開

MD6605は単独のマイコンとして製品化する予定はなく、システム内で使い勝手を向上させるため、ゲートドライバなどを搭載した高耐圧チップと一緒にワンパッケージ化した製品として量産予定である。

図17はAC-DC電源のPSU (Power Supply Unit) 向けの展開製品MD67xxを示す。MD6605を内蔵したMD67xxが、トーテムポールPFCと、電流共振LLCコンバータ×2チャネルを同時に制御できる。PSUに応用了MD67xxのメリットを以下に示す。

- (1) ブリッジレスのトーテムポールPFC、ゼロ・クロス・スイッチング、負荷状態に応じた最適制御により全負荷領域で高い効率（> 98%）を実現。

- (2) PFCの高速最適制御による低THDを実現。

- (3) LLCの高度な電流モード制御で高速応答を実現。

- (4) 高速スイッチング可能なGaN/SiCの活用により、ヒートシンクの小型化やプラットフォームの小型化を実現。

- (5) 通信制御、運転ログ管理、故障診断などの高機能化。

図17 MD6605のPSUへの応用例

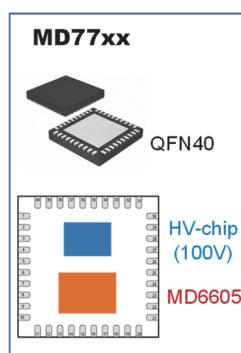

## 11. DC-DC電源IC製品への展開

図18はDC-DC電源の中間バスコンバータIBC(Intermediate Bus Converter)向けの展開製品MD77xxを示す。MD6605を内蔵したMD770xが、高効率ハイブリッドコンバータを複数チャネル並列化して制御する。IBUに応用したMD77xxのメリットを以下に示す。

- (1) 先進ハイブリッドコンバータにより、高いステップ・ダウン比率においても98%以上の高効率を実現。

- (2) 複数チャネルのコンバータを並列多相動作させ、電流バランスを精密制御することで出力200A以上の大电流化を実現。

- (3) MD770xひとつで、複数種類のコンバータ制御が可能（例：デュアルIBC、またはシングルIBC+POL x 6ch、など）。

- (4) PMBUS/AVB BUSの通信による電源制御が可能。

図18 MD6605のIBCへの応用例

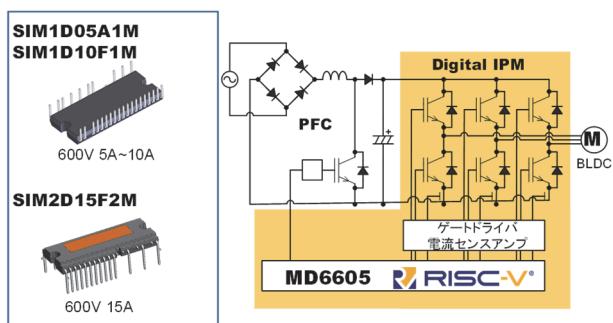

## 12. モータ制御向け製品への展開

図19は産業分野や白物家電分野に使うブラシレスDCモータ(BLDC)制御へのMD6605の応用例を示す。一般的のIPM(Intelligent Power Module)はパワー素子とゲートドライバを内蔵するが、さらにMD6605も搭載したデジタルIPMとして製品化し、モータをドライブするだけでなく回転数やトルクの制御も可能にする。MD6605の処理能力の高さからモータ制御と同時に電源制御(PFC制御など)も行うことができる。MD6605を搭載

したデジタルIPMの特長を以下に示す。

- (1) センサレスペクトル制御機能と、自動的にモータパラメータを抽出して最適制御を行うオートセルフアライメント機能を搭載し、高効率化を実現。

- (2) ゲート駆動波形のdv/dtが調整することで、低ノイズ化を実現。

- (3) モータと電源(PFC)の同時制御により部品点数を削減し基板サイズとシステムコストを低減。

- (4) モータパラメータの自動チューニング用GUIアプリの提供により、開発効率を向上。

- (5) 通信機能、故障検出機能、故障予測機能などによるインテリジェント化。

図19 MD6605のモータ制御への応用例

## 13. むすび

先進的なパワエレ制御システム向けに、RISC-V CPUコア、22nm超低リークプロセス、およびReRAM不揮発メモリ技術を使用したマイコンMD6605を開発した。CPU、DSP、EPUによるヘテロジニアスマルチコア構成により高い処理性能を実現している。今後、MD6605を活用した高効率パワエレ制御向けICの展開を継続し、脱炭素社会を目指すGXへの取り組みに貢献していく。

## 参考文献

- 1) The RISC-V Instruction Set Manual Volume I Unprivileged Architecture, May 2025, RISC-V International.

- 2) The RISC-V Instruction Set Manual Volume II Privileged Architecture, May 2025, RISC-V International.

# 48V 車載用 MOSFET Module SAM4L10M30Z1 の開発

## Development of MOSFET Module SAM4L10M30Z1 for 48V Automotive

鈴木 誠 司\*

Seiji Suzuki

**概要** 近年自動車の電動化に伴いさまざまなパワートレインが開発されている中、主に欧州での需要が高い48V系マイルドハイブリッド車（48V MHEV）がある。サンケン電気(以降当社)ではその48V MHEVに搭載される電動コンプレッサに対応した100V低圧三相MOSFET Module SAM4L10M30Z1を開発した。求められる性能とパッケージ小型化の両立を実現するためにMOSFETの低オン抵抗化とモジュールパッケージ形状が重要となる。本稿では現在開発中である本製品の性能の紹介と開発状況について述べる。

### 1. まえがき

自動車の電動化に伴い中長期的な見通しでは電気自動車（EV）シフトのトレンドには大きな変化はないとの見方がある。一方で、短期的な見通しでは環境意識から従来の内燃機関車（ICE）への抵抗はあるが、バッテリ式電気自動車（BEV）の高価格、航続距離等の不満で購入を控える一定ユーザニーズを捉えたハイブリッド車（HEV）への需要が高まってきている。中でも主に欧州で需要が高いのが48V電源を使用したマイルドハイブリッド車（48V MHEV）である。世界的にDC60V以上は人体への危険があるため厳格な安全基準が適用されているケースが多く、その分コストもかかる。そこでコストを抑えつつもCO<sub>2</sub>排出量の削減を実現できるコンセプトのもと開発されたのが48V電源を使用したマイルドハイブリッド車である。当社は将来的なBEVへの需要変動リスクにも対応できるこのMHEV市場に参入すべく100V低圧三相MOSFET Module SAM4L10M30Z1を開発した。本製品を開発するにあたり、顧客からはモジュールパッケージの小型化が求められる。これに対応するためには、大電流に対応可能でチップサイズの小型化を実現するMOSFETの低オン抵抗化と、高い放熱性を発揮するパッケージ構造が必要である。

本稿では本製品においての課題であるMOSFETの低

オン抵抗化、高放熱パッケージ設計の背景を述べる。また、本製品の性能や機能、開発状況についても合わせて述べていく。

### 2. 市場背景

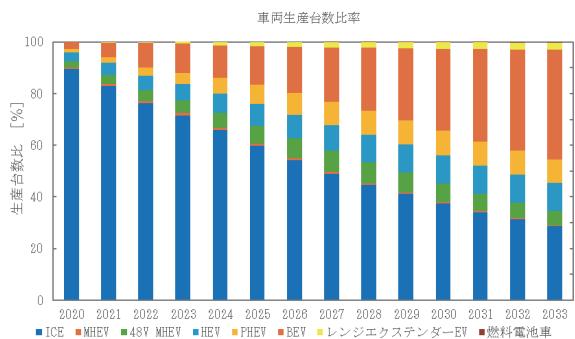

2025年現在の自動車市場の生産比率（図1）を見るにICEの生産比率が全体の約6割を占め、BEV、レンジエクステンダーEV（BEVx）と燃料電池式自動車（FCEV）の合算割合は2割弱となっている。残りの2割強をその他パワートレインが占める形となり、いまだICEの生産比率が大半を占める結果となっている。今後の予想では2033年まで緩やかに電動化が進む予測となっており、本製品のターゲットであるMHEVの市場も一定の成長が予想できる。また、2027年をめどにICEをその他電動化車両のシェアが上回る予想となっているのがわかる。

図1 2023年-2033年車両生産台数比率予測

出典：マーカーラインズ作成データ「世界ライトビークル販売に占める各パワートレインの構成比予測」(2025年10月閲覧)<sup>1)</sup>

\*技術開発本部パワーモジュール開発統括部

IPM開発部開発2課

表1 絶対最大定格

TA = 25°C

| 記号                    | 項目                                  | SAM4L10M30Z1 | 単位 |

|-----------------------|-------------------------------------|--------------|----|

| $V_{DS}$              | ドレイン-ソース間電圧                         | 100          | V  |

| $V_{GS}$              | ゲート-ソース間電圧                          | $\pm 20$     | V  |

| $E_{AS}$              | 単一パルスアバランシェエネルギー ( $I_{AS} = 50A$ ) | T.B.D.       | mJ |

| $T_j(\max)$           | 動作時最大ジャンクション温度                      | 175          | °C |

| $T_{STG}$             | 保存温度                                | -45 ~ +175   | °C |

| $V_{ISO}(\text{RMS})$ | 絶縁耐圧                                | 2500         | V  |

表2 電気的特性

TA = 25°C

| 記号                     | 項目                        | 条件                                         | SAM4L10M30Z1 |        |               | 単位                          |

|------------------------|---------------------------|--------------------------------------------|--------------|--------|---------------|-----------------------------|

|                        |                           |                                            | Min          | Typ    | Max           |                             |

| $BV_{DSS}$             | ドレイン-ソース間降伏電圧             | $I_D = 1\text{mA}, V_{GS} = 0\text{V}$     | (100)        | —      | —             | V                           |

| $I_{DSS}$              | ドレイン-ソース間漏れ電流             | $V_{DS} = 100\text{V}, V_{GS} = 0\text{V}$ | —            | —      | (5)           | $\mu\text{A}$               |

| $I_{GSS}$              | ゲート-ソース間漏れ電流              | $V_{GS} = \pm 20\text{V}$                  | —            | —      | ( $\pm 100$ ) | nA                          |

| $V_{GS(TH)}$           | ゲートしきい電圧                  | $V_{DS} = 10\text{V}, I_D = 1\text{mA}$    | (2.0)        | (3.0)  | (4.0)         | V                           |

| $R_{DS(ON)}\text{ HV}$ | ドレイン-ソース完オン抵抗<br>ハイサイドV相  | $I_D = 150\text{A}, V_{GS} = 10\text{V}$   | —            | (2.05) | (2.75)        | $\text{m}\Omega$            |

| $V_{DS}$               | ドレイン-ソース間ダイオード<br>順方向下降電圧 | $V_{GS} = 0\text{V}, I_S = 100\text{A}$    | —            | (0.85) | (1.3)         | V                           |

| $R\theta_{JC}$         | ジャンクション-ケース間熱抵抗           | —                                          | —            | (0.26) | (0.36)        | $^{\circ}\text{C}/\text{W}$ |

### 3. 製品紹介

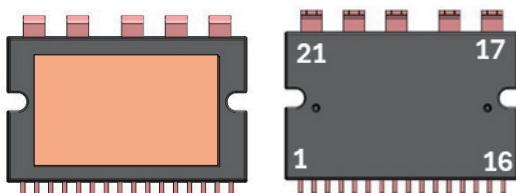

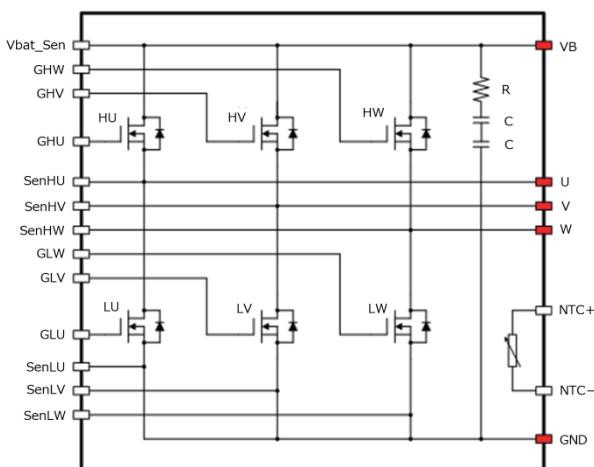

本製品の開発コンセプトは48V系電源を使用した車載への展開で当社の製品ポートフォリオを強化し、将来的なBEVへの需要変動リスクに対応するためである。ターゲットは48V系車載コンプレッサとなり、低圧パワーMOSFETが6素子入った低圧三相MOSFET Moduleとなる。本製品の仕様を表1、表2、表3、図2、図3で示す。

図2 外形イメージ図

図3 内部ブロック図

表3 ピンアサイン

| 端子番号 | 端子名      | 機能                        |

|------|----------|---------------------------|

| 1    | NTC+     | NTC サーミスタ端子1              |

| 2    | NTC-     | NTC サーミスタ端子2              |

| 3    | SenLW    | ローサイド W 相 Sense 端子        |

| 4    | GHW      | ハイサイド W 相 Gate 端子         |

| 5    | SenHW    | ハイサイド W 相 Sense 端子        |

| 6    | GLW      | ローサイド W 相 Gate 端子         |

| 7    | SenLV    | ローサイド V 相 Sense 端子        |

| 8    | GHV      | ハイサイド V 相 Gate 端子         |

| 9    | SenHV    | ハイサイド V 相 Sense 端子        |

| 10   | GLV      | ローサイド V 相 Gate 端子         |

| 11   | GLU      | ローサイド U 相 Gate 端子         |

| 12   | SunLU    | ローサイド U 相 Sense 端子        |

| 13   | SenHU    | ハイサイド U 相 Sense 端子        |

| 14   | GHU      | ハイサイド U 相 Gate 端子         |

| 15   | Vbat Sen | Vbat Sense 端子             |

| 16   | Vbat Sen | Vbat Sense 端子(15,16 共通端子) |

| 17   | VB       | バッテリー電圧端子                 |

| 18   | GND      | グランド端子                    |

| 19   | U        | U 相出力端子                   |

| 20   | V        | V 相出力端子                   |

| 21   | W        | W 相出力端子                   |

### 4. 製品の特長

本製品の特長であるMOSFETの低オン抵抗や機能、パッケージの設計について次に述べる。

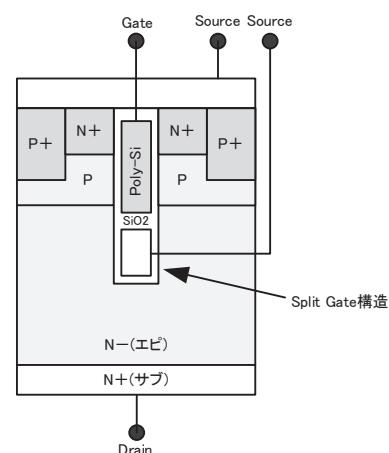

#### 4.1. MOSFETの低オン抵抗化

当社が開発したZeroMosはRepI（エピ抵抗）と耐圧のトレードオフを改善し、低オン抵抗への要求に対応することができる。図4にZeroMosの構造<sup>2)</sup>を示す。特徴はGate電極の下にSource電位を持つVFP（Vertical Field Plate）：縦型フィールドプレートを形成する事である。これによりエピ層の電界を緩和でき、大幅なオン抵抗低減を実現している。また、VFP構造でのオン抵抗の低減と合わせ、セルピッチの最適化やウエハ薄厚化技術導入し、従来のMOSFET構造に対してさらにオン抵抗の低減を実現した。大幅なオン抵抗が低減できた事に

図4 ZeroMos のセル部イメージ図

よりMOSFETチップサイズの小型化、それに伴うパッケージの小型化に貢献している。

#### 4.2. RCフィルター回路内蔵

本製品にはVB-GND間に抵抗、コンデンサーで構成されたフィルター回路が内蔵されている。(図3参照)これによりサージ電圧、スイッチングノイズ、リングイング低減に効果が期待できる。このパッケージ内部にフィルター回路を搭載することにより顧客側での外部フィルター回路の追加が抑えられるためコストの低減も期待できる。

#### 4.3. サーミスタ機能内蔵

本製品にはサーミスタ機能を搭載している。(1番端子-2番端子間)顧客ニーズとして、よりチップに近い位置での温度モニターがある。それを実現するために、パッケージ内部にサーミスタを搭載することで異常発熱の早期検知、システムの熱破壊防止を可能とする。

#### 4.4. 高放熱DBC (Direct Bonding Copper) 採用

本製品のパッケージは高放熱DBC構造を採用した放熱性に優れたパッケージとなっており、低熱抵抗化を実現している。(表2参照)

#### 4.5. 従来パッケージからの形状変更

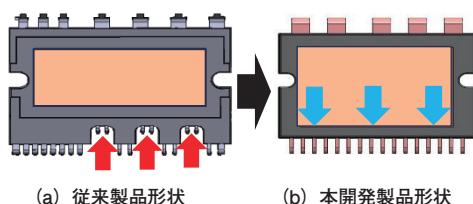

本製品は従来製品である車載向け高圧三相ブラシレス用モータードライバーSAM470××シリーズ(DIP27)のパッケージが元となり設計されている。しかし、DIP27パッケージ形状ではZeroMosのチップサイズが大きく搭載できない。ここではDIP27の長所である小型パッケージを生かしつつ形状を変更し、チップを搭載できるパッケージを設計できた背景を以下に述べる。

一つ目に高い入力電圧に対応するためパッケージに千鳥形状を設け沿面距離を確保している点がある。低圧製品である本製品は千鳥形状で沿面距離を確保する必要がないため廃止した。(図5)

二つ目にパッケージ内部にドライブ回路を有するコントロールチップ(MIC)を搭載するためのステージが構

図5 SAM470××パッケージからの変更イメージ

成されている点がある。本製品はコントロールチップを搭載しないMOSFET ModuleのためMICステージを廃止した。

千鳥形状の廃止と内部MICステージの廃止により、パッケージ形状が変更された。その結果、チップを搭載するDBC基板部の拡張が可能となり、ZeroMosチップの搭載を達成した。

### 5. 評価結果

現在開発中である本製品の評価実施結果の一部を次に示す。

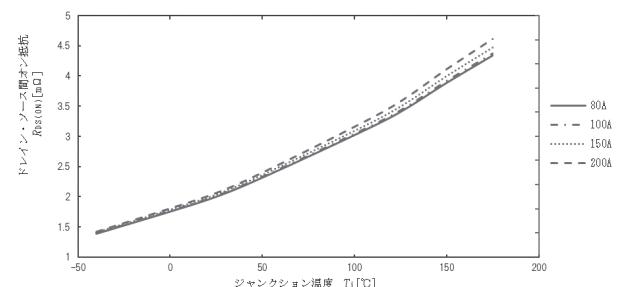

#### 5.1. $R_{DS(ON)}$ 温度特性確認

前項4.1で述べた低オン抵抗MOSFET ZeroMosの実力を確認するため $R_{DS(ON)}$ の温度特性データをグラフ化した。その結果を図6に示す。

条件：測定相 = HiSideV 相,  $V_{GS} = 10V$ ,  $I_D = 80A \sim 200A$ ,  $T_j = -40^\circ C \sim 175^\circ C$

図6  $R_{DS(ON)}$  温度特性グラフ

結果として25°Cの $R_{DS(ON)}$ 値が仕様を満足している。(表2参照)

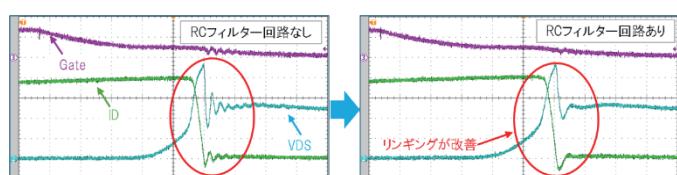

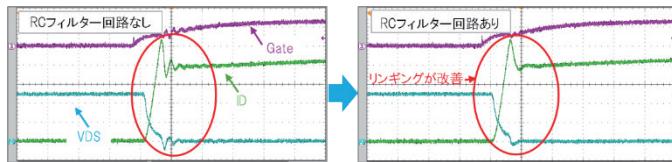

#### 5.2. RCフィルターの有効性確認

前項目4.2で述べた内蔵RCフィルターの有効性を確認するためRCフィルターあり、なしでスイッチング特性の変化を調査した。結果を次に示す。(図7), (図8)

条件：確認相 = Lo SideV,  $V_B = 48V$ ,  $V_{GS} = 15V$ ,  $L_p = 14\mu F$ ,  $T_a = 25^\circ C$ , フィルタ定数 =  $2.2\Omega + 0.047\mu F + 0.047\mu F$  あり、なし

図7 ターンオフ時のスイッチング波形

条件：確認相 = Lo SideV,  $V_B = 48V$ ,  $V_{GS} = 15V$ ,  $L_p = 14\mu F$ ,  $T_a = 25^{\circ}C$ , フィルター定数 =  $2.2\Omega + 0.047\mu F + 0.047\mu F$  あり, なし

図8 ターンオン時のスイッチング波形

結果としてターンオフ、ターンオン共にリングングの改善が認められRCフィルターの機能が有効であることが確認できた。

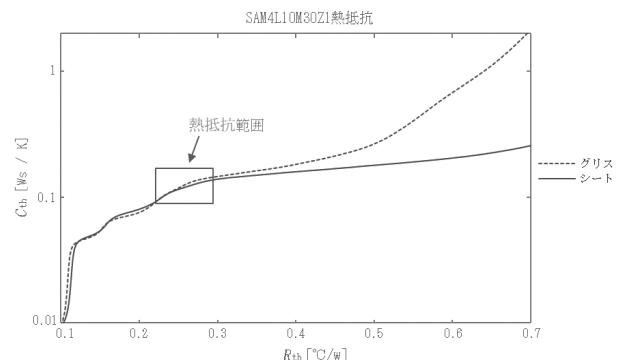

### 5.3. 热抵抗評価

前項目4.4及び4.5で述べた高放熱DBC基板を使用したパッケージの実力を確認するため熱抵抗評価を行った。結果を図9に示す。

結果は評価後の構造関数の確認でグリス、シートの境界線がグラフ上で囲った範囲であるため、仕様（表2参照）を満足している。

## 6. むすび

本稿では現在開発中であるSAM4L10M30Z1の製品紹介及び評価内容を掲載した。評価試験により、仕様を満足することが確認できた。今後の開発、評価スケジュー

条件：測定相 = HiSideW 相, サンプル取付け=グリス, 絶縁シートの2条件

図9 構造関数グラフ

ルは、AQG324、AEC101等信頼性試験の実施を予定している。

今回実施した評価結果及び今後の評価結果を製品開発に反映させ、より良い製品を顧客に提供できるよう進めていく所存である。

## 参考文献

- (1) マークライズ「世界ライトビークル販売に占める各パートトレインの構成比予測」、マークライズ社公式サイト, [https://www.marklines.com/portal\\_top\\_ja.html](https://www.marklines.com/portal_top_ja.html)

- (2) 近藤、田中：サンケン技報、vol.53、P47、(2021.11)

# 車載向け 1200V IPM シリーズ搭載パワーデバイスの開発

## Development of Power Device for Automotive 1200V IPM series

石井 孝明\*

Takaaki Ishii

山田 隼人\*

Hayato Yamada

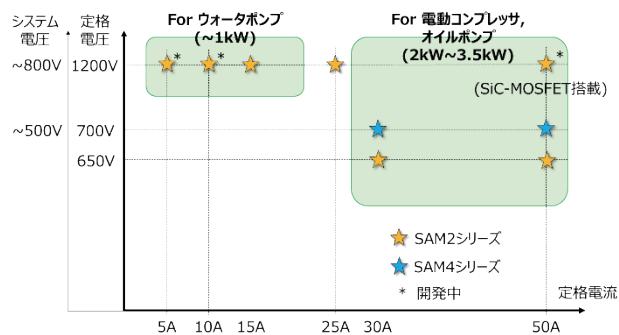

**概要** 当社では、パワーデバイスとそれを駆動かつ保護機能をもつ制御用ICチップ、温度検出用サーミスタを搭載したトランスマルチモード構造のIPM SAM2製品をシリーズ化してきた。これらは、自動車や産業機器のエアコンのモータを制御するIPMとしてインバータユニットの小型化と省エネルギー化に大きく貢献している。またアプリケーションの多様化した市場要求に応えるため、定格1200Vのラインナップの拡充を進めている。本稿では、電動ウォーターポンプ制御ドライバ用に新たに開発した、車載向け定格1200Vのパワーデバイスとそれらを搭載したSAM2製品について報告する。

### 1. まえがき

パワーデバイスとは、電力の制御や変換、供給を行うためのスイッチングデバイスである。エネルギーなどの資源を効率的に有効活用できるパワーエレクトロニクスにおけるパワーデバイスの役割は、昨今の環境に対する取り組みやそれらを取り巻く社会的背景からより一層重要度を増している。当社では600Vクラスを中心にパワーデバイスのプロセス開発を進め、内製IGBTおよびFRDを搭載した製品開発をおこなっており、エアコンやIHヒーターといった民生機器用途から、インバーター、UPSなどの産業機器用途や車載用途に至るまで、幅広く製品化してきた。特に民生エアコン向けIPMで長年培った技術と経験を基に、産業機器や車載エアコン向けに高電圧・大電流対応のパワーデバイス、制御用IC、サーミスタを搭載したトランスマルチモード構造IPM「SAM2」を製品化してきた<sup>(1)</sup>。またラインナップの拡充やアプリケーションの多様化した市場要求に応えるため、1200Vクラスのパワーデバイスおよびパッケージの技術開発により産業機器向け定格1200V SAM2製品の開発を進めてきた<sup>(2)</sup>。現在のSAM2製品ラインナップを表1、車載向けSAM2製品の開発動向について図1に示す。

表1 SAM2 製品ラインナップ

| 製品名          | 定格        | 用途   | 状況    |

|--------------|-----------|------|-------|

| SAM265M30AA1 | 650V/30A  | 車載   | 量産中   |

| SAM265M50AA1 | 650V/50A  | 車載   | 量産中   |

| SAM265M50BS3 | 650V/50A  | 産業機器 | 量産中   |

| SAM265M50AS3 | 650V/50A  | 車載   | 量産中   |

| SAM212M05BF1 | 1200V/5A  | 産業機器 | 量産中   |

| SAM212M10BF1 | 1200V/10A | 産業機器 | 量産中   |

| SAM212M15BF1 | 1200V/15A | 産業機器 | 量産中   |

| SAM212M05AF1 | 1200V/5A  | 車載   | 開発中   |

| SAM212M10AF1 | 1200V/10A | 車載   | 開発中   |

| SAM212M15AF1 | 1200V/15A | 車載   | 25年量産 |

| SAM212M25AF1 | 1200V/25A | 車載   | 開発中   |

図1 車載向け SAM2 製品の開発動向

近年のxEVでは冷却水を電動ウォーターポンプで循環させるシステムが新たに生まれている。このシステムを制御するSAM2パワーモジュールを新たにラインナップに加えるため、定格電流15A以下の1200V IGBTとFRDの開発を進めている。ウォーターポンプの冷却システム用途では、低損失や高応答な駆動性能が求められ

\*技術本部プロセス技術統括部

パワーデバイス開発部 製品開発課

るだけではなく、モジュール自体は直接冷却されない厳しい使用環境に耐える必要がある。このような市場要求に応えるべく、耐熱性として低温・高温での動作保証、耐ノイズ性としてFRDのソフトリカバリー性能を実現した。本稿では、それら車載向け定格1200Vのパワーデバイスを搭載したSAM2製品について報告する。

## 2. 製品概要

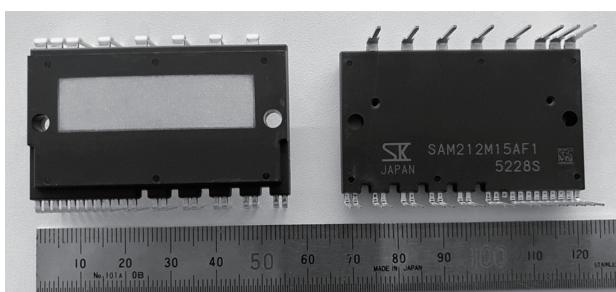

SAM2製品は、出力スイッチング素子としてIGBTとFRD、プリドライバIC、制限抵抗付きブートストラップダイオードおよび温度検出用サーミスタを搭載したトランスマルチモード構造の3相インバータ駆動用IPMである。SAM2製品シリーズの外観写真を図2に示す。パッケージは絶縁距離を確保し1200V定格を実現している。その他、シリーズで共通する製品特長を以下に示す。

- 制御電圧最大定格25V

- 絶縁耐圧2500V（1分）保証

- サーミスタ内蔵

- 各種保護機能搭載

- 過電流保護保持時間調整可能

- IGBT、FRD動作温度保証 $T_j: 175^{\circ}\text{C}$

図2 SAM2製品シリーズの外観

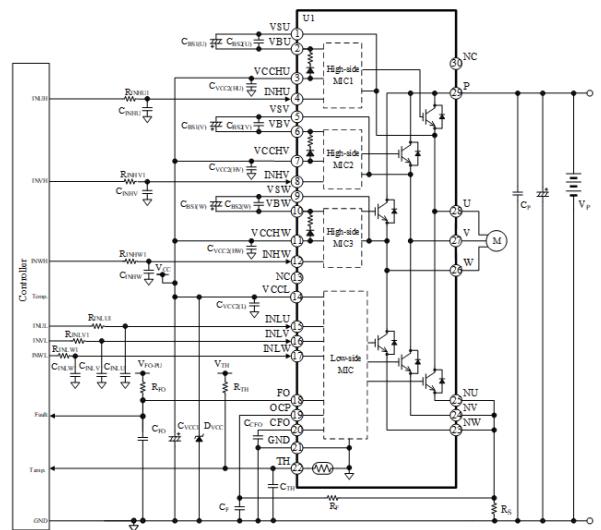

車載向け、定格1200V/15A、SAM212M15AF1の応用回路例を図3に示す。図左側のControllerから受けた信号でIGBTを駆動し、高電圧かつ大電流を制御する。これによってモータへの出力端子U、V、W端子の通電状態・電流方向を変化させ、顧客の使用方法に合わせたモータ駆動を実現する。過電流保護機能の搭載や温度監視のためのサーミスタ内蔵などといったシステム全体を補助する機能も有している。こうしたController側へのフィードバックをおこなうことができるのが製品特長である。

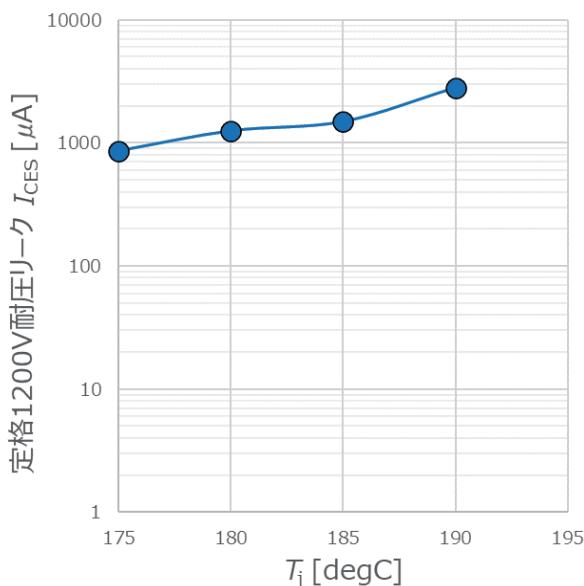

うことで高温時の耐圧リーケ電流 $I_{CES}$ を抑制し、 $T_j = 175^{\circ}\text{C}$ を超えても熱暴走しにくい設計とした。図4に示すように、IGBT単チップの定格1200V耐圧リーケ電流 $I_{CES}$ は190°Cで3mA程度であり、熱暴走していないことを確認した。

図4 SAM212M15AF1搭載IGBT単チップの定格1200V耐圧リーケ $I_{CES}$ とジャンクション温度 $T_j$

#### (C) 短絡時における安全動作領域保証

IGBTでは大容量の電力を扱うために、オン電圧の低減やターンオフスイッチング損失低減を進める一方で、破壊耐量を確保する必要がある。負荷が短絡した場合や他の素子が破壊した場合でも、短絡（過電流）保護回路が働きゲート電圧が遮断するまでの一定時間、IGBTは破壊せずに耐える設計にしなくてはならない。IGBTの電流飽和特性を生かし、表面Nエミッタ層にあたるチャネル領域を調整し、MOS構造を最適化することで飽和電流を抑制し、製品に必要な破壊耐量を確保できるように設計した。

#### (D) 車載品質保証への取り組み

車載向け製品において、品質や安全性に直結する重要特性およびお客様からの要求特性についてはリスク分析をおこない、影響度の高い項目に関連する技術的要素を製品設計や製品仕様に反映している。パワーデバイス製造は重要工程パラメータとしてSPC (Statistical Process Control) 管理をおこなっている。未然防止や異常の早期発見だけでなく、製造工程のばらつきについて日常的に把握し工程能力を管理することで品質の安定化に努めている。

### 3.3. 1200V FRDチップ技術

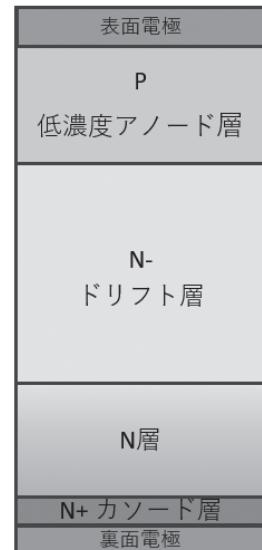

定格1200VのFRDについては、600V低ノイズFRD<sup>(4)</sup>の活性部構造を踏襲した低濃度アノード構造を採用し、ライフトタイムコントロールにより低損失化とソフトリカバリー特性を両立している。車載向け1200V FRDの特長について次項で詳述する。

### 3.4. 車載向け1200V FRDの特長

#### (A) ソフトリカバリー特性

車載向け定格1200V FRDの活性部構造を図5に示す。製品でのスイッチングノイズを抑制するために、ドリフト層の底部に緩やかな濃度勾配を持ったN層を設けることで、急峻なキャリア消滅を抑制しソフトリカバリー特性になるように設計した。低濃度アノード構造によるホール注入の抑制および粒子線によるライフトタイムコントロールの最適化により低損失化を実現した。

図5 車載向け定格1200V FRDの活性部構造

#### (B) 低温耐圧保証と順回復電圧抑制

低温-40°Cの定格電圧保持の為にN-ドリフト層を厚くする必要があるが、その際には順回復電圧について考慮する必要がある<sup>(2)</sup>。IGBTのターンオフ時、FRDの高抵抗N-ドリフト層にキャリアが注入され、電導度変調によりその抵抗値が徐々に低下するが、ターンオフ直後は抵抗値が十分に下がりきらず順方向電圧（順回復電圧）が上昇する。この発生した電圧がハイサイド駆動ICに負電位として印可され、誤動作の要因となる。N-ドリフト層厚が厚くなると順回復電圧は上昇してしまうため、N層の厚みとキャリア濃度を最適化することで、低温での定格電圧保持と順回復電圧抑制の両立をおこなった。

## 4. 製品検討結果

### 4.1. スイッチング特性および電気特性

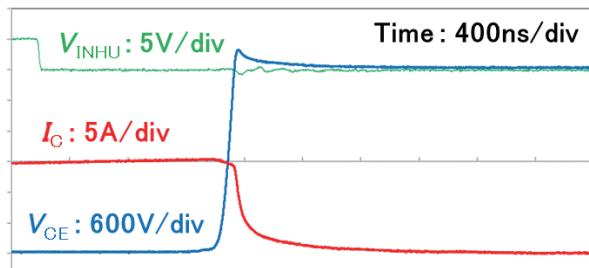

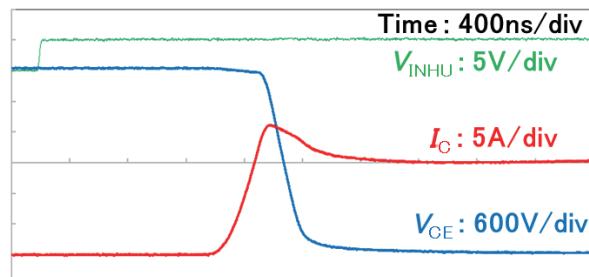

検討した車載向け定格1200V/15AのSAM2製品SAM212M15AF1のスイッチング試験波形を図6に示す。

$T_j = 175^\circ\text{C}$ においても安定した高温動作を確認しており、スイッチング損失やソフトリカバリー特性について製品目標を満足する特性が得られた。電気的特性について表2に示す。

(a) ハイサイド ターンオフ波形

(b) ハイサイド ターンオン波形

縦軸： $V_{INHU}$ ,  $V_{CE}$ ,  $I_C$ , 横軸：Time

測定条件： $V_P = 600V$ ,  $V_{CC} = 15V$ ,  $I_C = 15A$ ,  $T_j = 175^\circ\text{C}$

図6 SAM212M15AF1 スイッチング試験波形

### 4.2. 伝導ノイズ特性

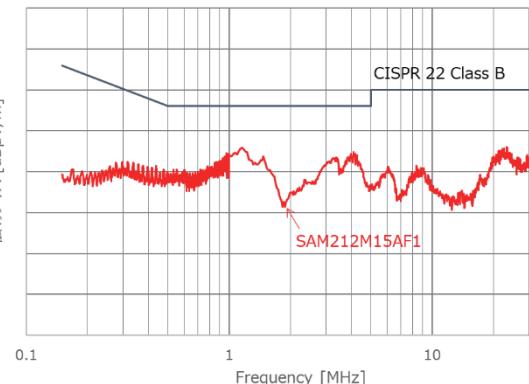

インバーターのスイッチング動作によって発生する電流・電圧の影響について、各周波数帯域での伝導ノイズ特性を図7に示す。CISPR22 Class B規格を満足しており、スイッチング損失とノイズ特性のバランスについて最適化がおこなわれていることが確認できた。

図7 各周波数帯域での伝導ノイズ特性

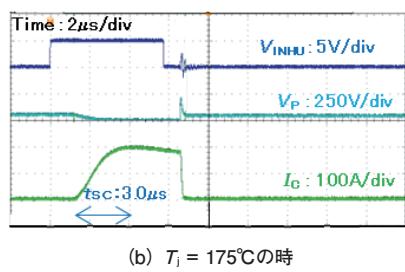

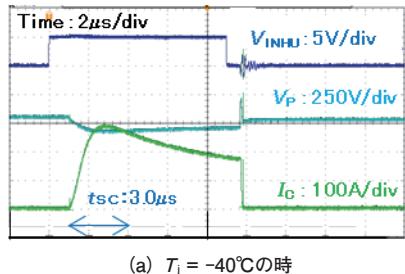

### 4.3. 短絡試験

図8に短絡試験の波形を示す。低温 $-40^\circ\text{C}$ および高温 $175^\circ\text{C}$ において、製品目標である短絡電流時間 $t_{sc} : 3.0\mu\text{s}$ に対して非破壊となり、温度保証全範囲において十分な短絡耐量を確保した。

### 4.4. 信頼性評価

パワーモジュールの性能評価として、検討した車載向け定格1200V/15AのSAM2製品SAM212M15AF1において、IEC, JEITA, AQG324の信頼性ガイドラインに準拠した包括的な試験を実施し問題ないことを確認した。

表2 SAM212M15AF1 の電気的特性

| 項目             | 記号                   | 条件                                                                                                          | Min. | Typ. | Max. | 単位            |

|----------------|----------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| コレクタ-エミッタ間漏れ電流 | $I_{CES}$            | $V_{CE} = 1200V$ , $T_j = 25^\circ\text{C}$                                                                 | —    | —    | 0.1  | mA            |

| コレクタ-エミッタ間飽和電圧 | $V_{CE(\text{SAT})}$ | $I_C = 15A$ , $T_j = 25^\circ\text{C}$                                                                      | —    | 1.7  | 2.2  | V             |

|                |                      | $I_C = 15A$ , $T_j = 125^\circ\text{C}$                                                                     | —    | 2.1  | 2.7  | V             |

| ダイオード順方向電圧     | $V_F$                | $I_F = 15A$ , $T_j = 25^\circ\text{C}$                                                                      | —    | 2.1  | 2.6  | V             |

| ハイサイドスイッチング特性  |                      |                                                                                                             |      |      |      |               |

| ダイオード逆回復時間     | $t_{rr}$             | $V_{P(\text{DC})} = 600V$ , $I_C = 15A$ , $V_{IN} = 0 \leftrightarrow 5V$ , $T_j = 25^\circ\text{C}$ , 誘導負荷 | —    | 0.50 | —    | $\mu\text{s}$ |

| ターンオン時間        | $t_{ON}$             |                                                                                                             | —    | 1.25 | —    | $\mu\text{s}$ |

| ターンオンスイッチング時間  | $t_{C(ON)}$          |                                                                                                             | —    | 0.45 | —    | $\mu\text{s}$ |

| ターンオフ時間        | $t_{OFF}$            |                                                                                                             | —    | 1.30 | —    | $\mu\text{s}$ |

| ターンオフスイッチング時間  | $t_{C(OFF)}$         |                                                                                                             | —    | 0.30 | —    | $\mu\text{s}$ |

| ローサイドスイッチング特性  |                      |                                                                                                             |      |      |      |               |

| ダイオード逆回復時間     | $t_{rr}$             | $V_{P(\text{DC})} = 600V$ , $I_C = 15A$ , $V_{IN} = 0 \leftrightarrow 5V$ , $T_j = 25^\circ\text{C}$ , 誘導負荷 | —    | 0.45 | —    | $\mu\text{s}$ |

| ターンオン時間        | $t_{ON}$             |                                                                                                             | —    | 0.90 | —    | $\mu\text{s}$ |

| ターンオンスイッチング時間  | $t_{C(ON)}$          |                                                                                                             | —    | 0.45 | —    | $\mu\text{s}$ |

| ターンオフ時間        | $t_{OFF}$            |                                                                                                             | —    | 0.90 | —    | $\mu\text{s}$ |

| ターンオフスイッチング時間  | $t_{C(OFF)}$         |                                                                                                             | —    | 0.30 | —    | $\mu\text{s}$ |

縦軸： $V_{\text{INHU}}$ ,  $V_P$ ,  $I_C$ , 横軸：Time

測定条件： $V_P = 800\text{V}$ ,  $V_{\text{CC}} = 16.5\text{V}$

図 8 SAM212M15AF1 の短絡試験波形

## 5. むすび

1200Vクラスの車載向けモータドライバIPM製品搭載に向けたパワーデバイスとしてIGBT・FRDを開発、定格1200V/15AのSAM2製品SAM212M15AF1を製品化し、SAM2ラインナップを拡張した。産業機器向けと同様な電流ラインナップを順次量産展開するとともに、定格1200Vにおいて大電流領域のIPM製品の拡充へむけてパワーデバイスおよびパッケージの開発を今後も進めていく。

## 参考文献

- (1) 高山, 浅見, 小野: サンケン技報, vol.53, pp.21-24, Nov.2021

SAM265M30AA1・50AA1 の開発

- (2) 張, 久我: サンケン技報, vol.54, pp.9-12, Nov.2022

産業機器向けモータドライバIPM

SAM212M10BF1 の開発

- (3) 石井: サンケン技報, vol.52, pp.17-20, Nov.2020

1200V FS-IGBT の開発

- (4) 南野: サンケン技報, vol.50, pp.39-42, Nov.2018

低ノイズ FRD FMXR-1206S の開発

# スマート SiC-IC の高速駆動と短絡保護技術

～誰もが簡単に超高速スイッチング性能を引き出せる SiC-MOSFET ～

## High-Speed Driving and Short-Circuit-Free Protection Technology for Smart SiC-IC

横井 魁人\*

Kaito Yokoi

町田 修\*\*

Osamu Machida

**概要** SiC MOSFETは高耐圧でありながら小型化ができるため、高圧回路で大電流の高速なスイッチングが可能となる。特にSiC MOSFETのソース電極に、主電流の流れないゲート用ソース端子を用いることで、低インダクタンスのゲート制御が可能となり、高速なスイッチングを実現できる。しかし、高圧スイッチング中に短絡が発生した場合、SiC-MOSFETには数千A/ $\mu$ sの高速で短絡電流が流れ、1 $\mu$ s以下の短絡破壊が発生する。このような4端子(4P)駆動に対して、Si-IGBTでは一般的な3端子(3P)駆動をSiC-MOSFETでおこなった場合、スイッチング速度は大幅に低下するが、短絡電流も制限されて短絡耐量時間が数倍延びることが確認された。この4P駆動による高速スイッチングと3P駆動による短絡保護を、両立する駆動方法を開発した。

### 1. まえがき

SiCはSiの約10倍の破壊電界を有し、高耐圧デバイスに応用した場合、素子サイズを数分の一に小型化できるポテンシャルを有している。しかし、従来のSi素子に最適化された高圧回路の中に単純に置き換えた場合、その性能が出しきれないため、SiCデバイスを最適に設計し、駆動する必要がある。

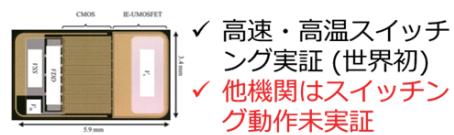

図1に示す通り、産業技術総合研究所(産総研)では超高速スイッチングを可能とするSiC-CMOS内蔵MOSFETの開発をおこなっている。このチップはSiC-MOSFETのゲート配線による浮遊インダクタンスを最小にする狙いで、SiC-MOSFETのチップ内にゲート駆動用のCMOSを有している。この技術により1200Vの電圧を数nsでスイッチングすることに成功している。<sup>1), 2), 3), 4)</sup>

一方、このような高速な素子を高圧回路に用いた場合、様々なサージが問題となるが、その中でも、短絡時のサージ電流は大きな問題である。短絡時に高速なスイッチ

グにより非常に短時間で短絡電流がピークとなり、短絡破壊に至るためである。<sup>5), 6), 7)</sup>

この課題に対し、安全に保護するゲート駆動技術の開発を産総研と当社が研究しており、“誰もが簡単に超高速スイッチング性能を引き出せるSiC-MOSFET”の実現を目指している。

#### 産総研のSiCパワーIC技術

- ✓ 高速・高温スイッチング実証(世界初)

- ✓ 他機関はスイッチング動作未実証

- ・NEパワーレアード2021 最優秀賞

- ・ISPSD2021 Best Paper Award

#### サンケン電気の外部保護回路技術

世界最高レベルの小型・省エネルギー化可能なSi MIC搭載モジュール製品

\* 技術開発本部プロセス技術統括部

\*\* 技術開発本部プロセス技術統括部

## 2. 高速スイッチングと短絡耐量の関係

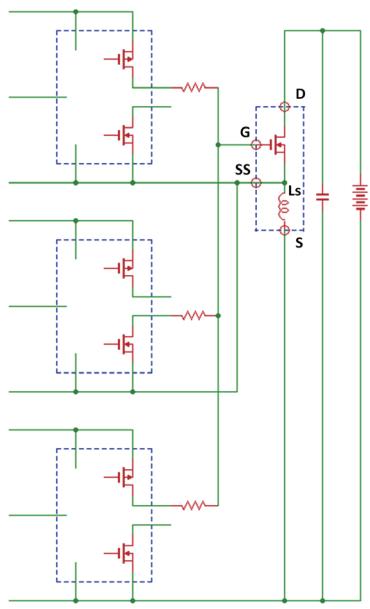

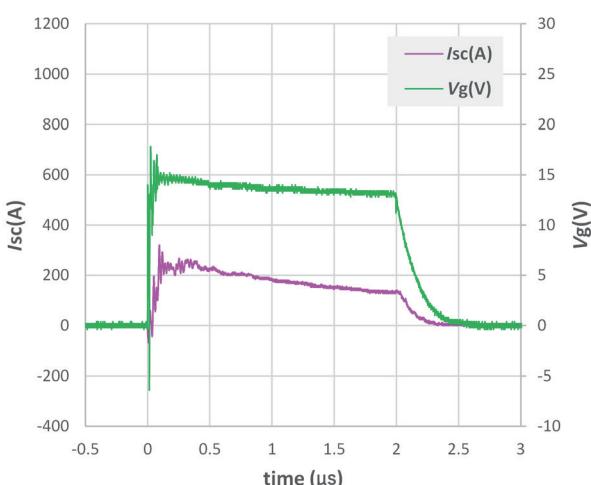

図2にSiC-MOSFETの短絡評価に用いた回路図を示す。DUTのMOSFETにはソース電流が流れ込まないセンスソース(SS)端子が存在し、通常のソース端子(S)と切り替えて評価可能な回路である。

図2 SiC-MOSFETの短絡評価回路

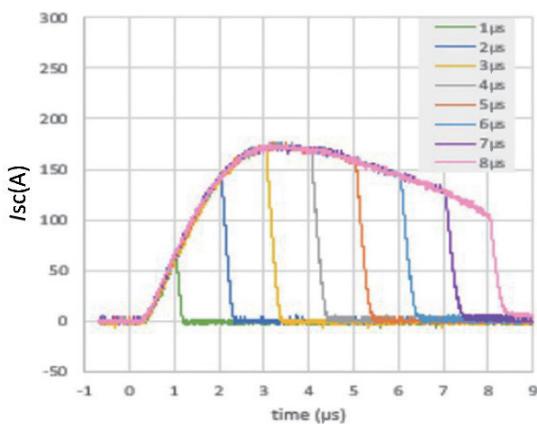

また、図3にSiC-MOSFETの典型的な短絡電流波形で $R_g = 470\Omega$ と $R_g = 10\Omega$ の場合をそれぞれ示す。ゲートの駆動端子にはS端子を使用し、3P駆動している。

SiC-MOSFETは1200V、40mΩで、 $V_d = 600V$ で負荷短絡した状態を再現している。 $R_g = 470\Omega$ を介してSiC-MOSFETをスイッチングした場合、3μs程度で電流最大となり、その後、8μsにかけて、SiC-MOSFETの自己

発熱で電流が低下し、短絡耐量が低い素子の場合は破壊に至る。

これに対して、 $R_g = 10\Omega$ に変えた場合、SiC-MOSFETのスイッチング速度が速まるため、急速に短絡電流が上昇し、2μsで電流ピークに達し、 $R_g = 470\Omega$ の場合よりも高くなっている。その後、SiC-MOSFETの温度上昇により急速に電流が減少しており、短絡時間が減少する。

短絡破壊は、短絡電流×短絡電圧×短絡時間による消費エネルギーによるものであり、図3に示すように、 $R_g$ を低くしてスイッチングスピードを速めると、短時間で電流がピークに達し、破壊リスクが高まることがわかる。

## 3. 4P駆動と3P駆動について

一方、SiC等の化合物半導体のパッケージは、高速にスイッチングするためにソース電流を流さないゲート駆動用ソース端子(SS)を設けた4端子パッケージが主流となっている(図2)。

4P駆動は寄生インダクタンスが無く、高速にスイッチングできるが、前述同様に短絡破壊に至るまでの時間、短絡耐量時間が減少する。3P駆動は寄生インダクタンスに発生する電圧によって電流変化が抑制され、短絡耐量に優れるがスイッチングが遅い。

今回、この様な高速スイッチングによる短絡耐量時間が極端に短くなる問題に対し、ソース端子を4P接続と3P接続の切替をすることで改善する技術を開発した。

スイッチング時はゲート駆動の接続をセンスソースに繋ぐ4P接続で高速スイッチングをおこない、その後の定常時は3端子のソースに繋ぎ変えることで、短絡耐量が向上することが期待される。このソース端子の切替手法の最適化をおこない、SiC-MOSFETの最速のスイッチングと短絡耐量時間の大幅な延長の両立を狙った。

(a)  $R_g = 470\Omega$

(b)  $R_g = 10\Omega$

図3 SiC-MOSFETの短絡電流例

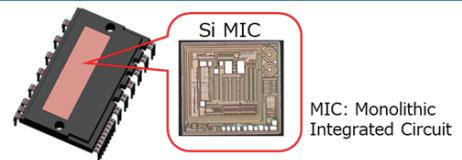

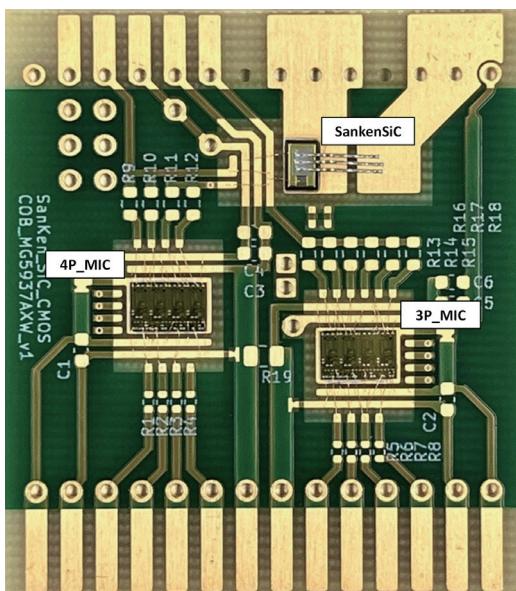

#### 4. 新規Monolithic IC (MIC) 紹介

図4に4P, 3P切替機能を有するMICのSiC-MOSFET評価ボードを示す。MICには、4P駆動用のチャンネルが3つと3P駆動用チャンネルが1つある。4P駆動用3チャンネルは、産総研のCMOSドライバー搭載SiC-MOSFETのP channel-MOSFET, N channel-MOSFET, 及び、パワーSiC-MOSFETのゲートを直接駆動するチャネルであり、ソース電流が流れないSS端子に接続して4P駆動する。一方、残りの1チャンネルもパワーSiC-MOSFETのゲートを直接駆動するが、ソース端子がS端子となり3P駆動する。

図4 SiC-MOSFETの短絡評価ボード写真

本MICは、短絡電流の急激な $di/dt$ をSS端子とS端子間の浮遊インダクタンスで発生する起電圧 $V_{ls}$ で検出して短絡遮断することを想定している。

MIC出力のDelay時間は300ns程度であり、短絡時に検出回路のDelay時間500ns以内を含めて、1μs以内に短絡保護が可能なMICである。さらに、並列で駆動した場合、いずれかのSiC-MOSFETの $V_{ls}$ で短絡を検出すると、同期して遮断できる機能も想定している。

1つのMICで産総研のCMOSドライバー搭載SiC-MOSFETを駆動できる設計だが、今回の評価ボードでは、4P駆動の高速化と3P駆動の短絡保護の効果を評価し易くするため、4P駆動と3P駆動のMICでそれぞれ2チップ構成とした。さらに、各チャンネルの出力は、SourceとSinkが個別に出力できるため、ON時の高速スイッチング時の $R_g$ を多段で切り替え可能であり、OFF時も同様に多段での切り替えが可能である。

#### 5. 実験結果

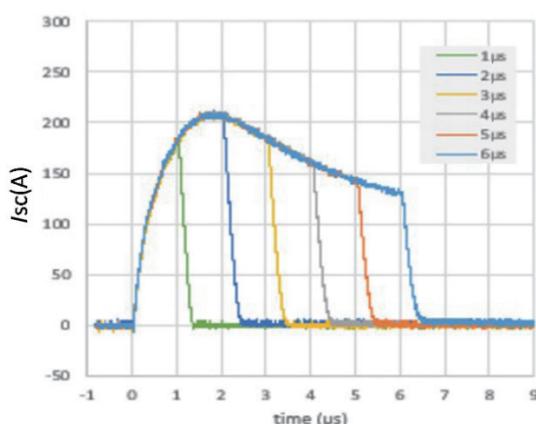

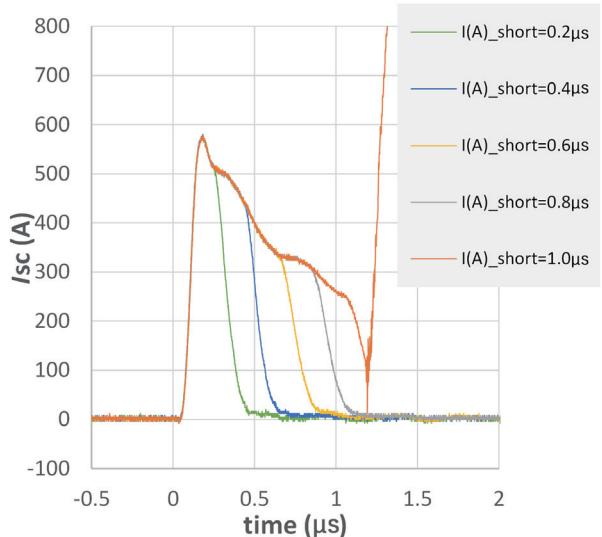

##### 5.1. 4P駆動の短絡波形

図5に4P駆動で高速スイッチングの回路構成で短絡した場合の短絡波形を示す。4P駆動では、200ns程度で短絡電流 $I_{sc}$ がピークに達し、約600Aまで増加している。その後、デバイスの発熱で急激に電流が減少し、短絡発生後1μsで破壊していることがわかる。

図5 4P構成の短絡電流波形

##### 5.2. 4P/3P切替駆動時の短絡保護と課題

図6に4P/3P駆動時の短絡波形を示す。切替手法は4P/3P同時駆動し、100ns後に4P駆動がオフとなり、3P駆動による短絡保護に切り換わる。

オン時の4P/3P駆動中に $di/dt$ が大きいため、ゲート電圧 $V_g$ の立ち上がりが遅れている。その結果、100nsの

図6 4P/3P切替駆動時の短絡波形

図7 改善後の4P/3P切替駆動のスイッチング測定波形

時点での $V_g=13\text{V}$ に留まっている。これは $di/dt$ が大きいことにより、3P駆動でのゲート電圧の立ち上がり抑制の効果である。

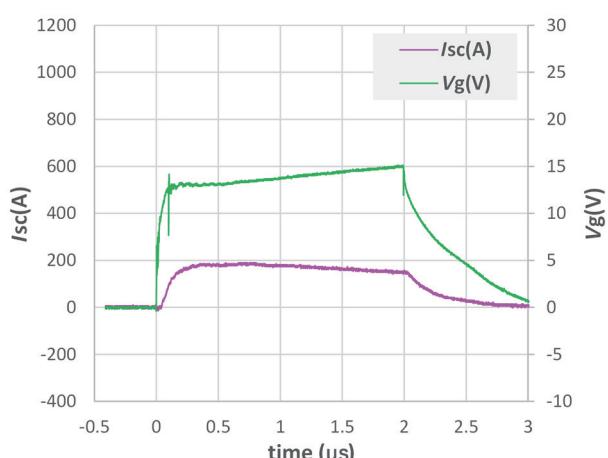

### 5.3. 改善後の4P/3P切替駆動時の短絡保護

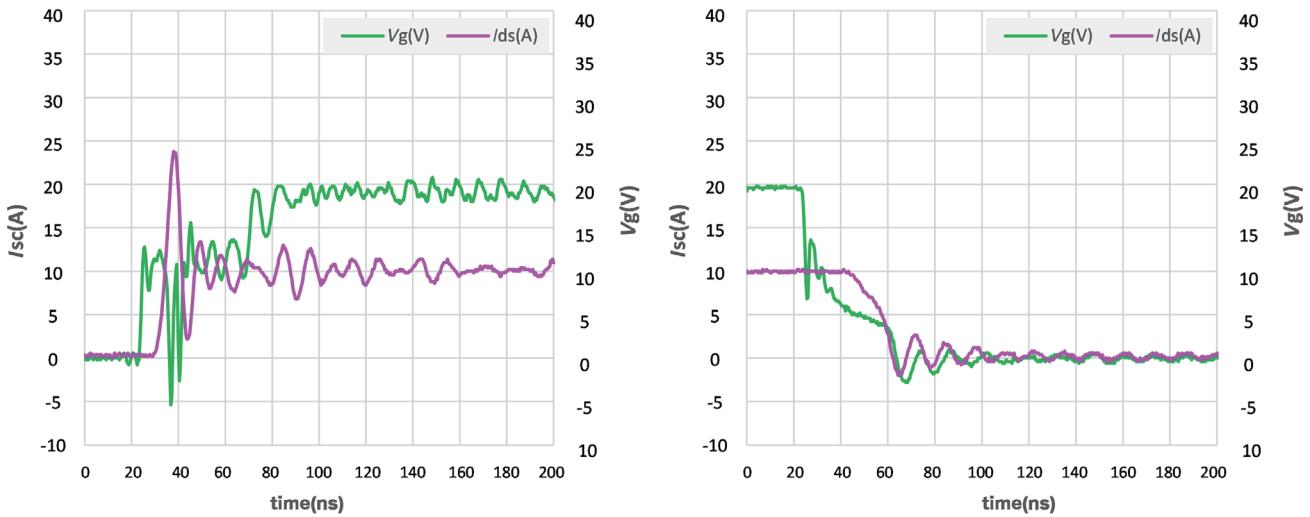

前述の切替手法に対して、以下の変更を加えた。初期状態では4P駆動のみとする。一方、3P駆動は4P駆動のオフ時に駆動する。

図7に改善した4P/3P切替スイッチング測定波形を示す。定常駆動条件として $I_{ds}$ 電流を10Aに設定し、ハーフブリッジ回路のローサイドにてスイッチングを行った。

図8に定常駆動と同一の駆動条件下における4P/3P切替の短絡測定波形を示す。短絡時には大電流が瞬時に流れることでソースインダクタンス $L_s$ に負電位が発生

する。その際、ゲート電圧が十分に上昇する前に3Pへと切り替えておくことで、短絡時のゲート電圧 $V_g$ の上昇が抑制され、短絡電流 $I_{sc}$ が低減した。結果、4P駆動単体の場合よりも短絡耐量が大幅に向上了。

## 6. むすび

本研究ではSiC-MOSFETの高速スイッチングを維持し、短絡耐量を兼ね備えることの課題について検討し、4P/3P切替駆動により実証した。その結果、4P駆動では短絡耐量1μsのデバイスを4P/3P切替駆動によって2μs以上に延長することを達成した。

これらの結果を踏まえ、さらなる“誰もが簡便に超高速スイッチング性能を引き出せるSiC-MOSFET”の実現を目指していく。

## 7. 謝辞

この成果の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構（NEDO）の委託事業（JPNP 14004）の結果得られたものです。

## 参考文献

図8 改善後の4P/3P切替駆動の短絡測定波形

- 1) Atsushi Yao, High-speed switching operation for a SiC CMOS and power module. IEICE Electronics Express, Vol. 18, No. 14, pp. 1–5, 2021.

- 2) Atsushi Yao, High-speed and high-temperature switching operations of a SiC power MOSFET using a SiC CMOS gate driver installed inside a power module. Solid State Phenomena, Vol. 360, pp. 81–87, 9 2024.

- 3) Mitsuo Okamoto, First Demonstration of a Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS

- Gate Buffer. 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 71–74, 2021.

- 4) Atsushi Yao, High-Speed and High-Temperature Switching Operations of a SiC Power MOSFET Using a SiC CMOS Gate Driver Installed inside a Power Module. Solid State Phenomena, Vol. 360, pp. 81–87, 2024.

- 5) Anas El Boubkari, CMOS Gate Driver with Integrated Ultra-Accurate and Fast Gate Charge Sensor for Robust and Ultra-Fast Short Circuit Detection of SiC power modules. In *2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, Vol. 2023-May, pp. 68–71. IEEE, may 2023.

- 6) Zhiqiang Wang, Design and Performance Evaluation of Overcurrent Protection Schemes for Silicon Carbide (SiC) Power MOSFETs. *IEEE Transactions on Industrial Electronics*, Vol. 61, No. 10, pp. 5570–5581, oct 2014.

- 7) Yuxiang Shi, Switching Characterization and Short-Circuit Protection of 1200 V SiC MOSFET T-Type Module in PV Inverter Application. *IEEE Transactions on Industrial Electronics*, Vol. 64, No. 11, pp. 9135–9143, 2017.

# 裏面漏光防止型赤外チップLEDの開発

Development of Infrared Chip LED with Backside Light Leakage Suppression

野田耕作\*

Kosaku Noda

**概要** 小型化の市場背景から、赤外チップLED裏面からの漏光が問題となってきた。本開発では、赤外チップLEDの基板材質を赤外線透過率の低い材質に変更することで、裏面からの漏光を防止することが可能となった。開発した赤外チップLEDは、現行流動品と外形も実装ランドパターンもコンパチであるため、ユーザーでの回路基板の設計変更が不要である。本稿では、そのLEDの特性、特徴を報告する。

## 1. まえがき

当社は、リモコン用から近接センサー用途までの赤外LED（以下LED）をラインアップしている。近年は製品の小型化、回路基板の縮小化、省電力化が求められる中で、部品間の実装間隔が小さくなっている。そのため、LEDと受光素子が近接することで、受光部位以外からの漏光が光ノイズとして無視できなくなってきた。

一般的には、受光素子側、LED側それぞれに遮光カバーの取付けなどにより光ノイズを低減するが、お互いが近接している場合は、回路基板自体が導光路となり遮光しきれない場合がある。

そこで今回は、LEDから回路基板への漏光に着目し、回路基板が導光路として機能しないような赤外LEDを開発したので、概略を報告する。

## 2. 裏面漏光防止赤外LED

### 2.1. 開発のコンセプト

本開発では、既存LEDの使い勝手を変えることなく、漏光を防止することを目指した。

つまり、既存LEDのユーザーが、回路基板の実装パターン形状やレジスト形状を設計変更せず、速やかな置き換えを可能とした。

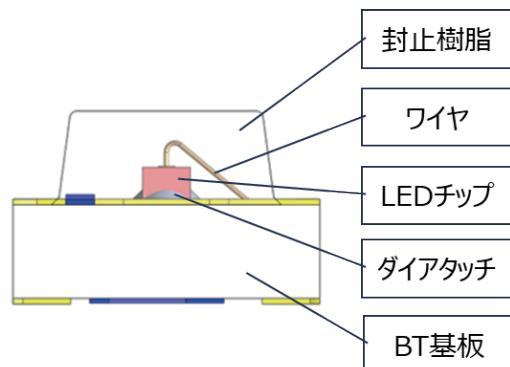

### 2.1. 現行型赤外チップLED

現行型赤外チップLED（以下現行型LED）の基本構造は図1の通りで、BT基板、LEDチップ、ワイヤ、ダイアタッチ、封止樹脂で構成される。光の配光を制御する封止樹脂は無色透明で、透過率の高いエポキシ樹脂である。BT基板とは、ガラス繊維を層構造にして反射材とBT（ビスマレイミド・トリアジン）樹脂を含侵させた白色の基板である。

BT基板は、可視光から赤外光領域では高反射率90%以上を示す。（残りの10%がBT基板側に吸収され、今回の漏光の原因になる）

図1 現行型LEDの構成図

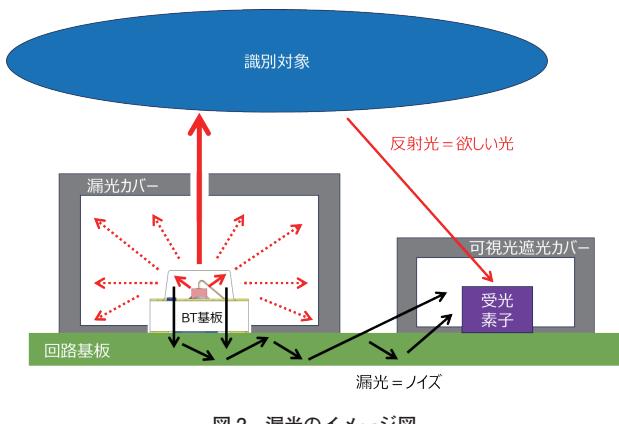

### 2.3. 現行型LEDの課題

現行型LEDを使用して、同一回路基板上の近接した受光素子にて識別対象の検知を行う場合、図2のように構成される。

通常、LEDから発した光の一部を信号として送信し、

\*技術開発本部 ワーデバイス開発統括部

オプト技術部 LED開発課

識別対象物からの反射光を受光素子が受信して検知する。

同時に、LEDの封止樹脂内で多重反射した光がBT基板側へ透過し、回路基板側へ伝搬、受光素子側へノイズとして現れる。反射光の強度が強ければ無視できるノイズが、反射光が微弱である場合は無視できなくなる。

つまり、回路基板への漏光を無視できる程度まで抑え込む必要がある。

図2 漏光のイメージ図

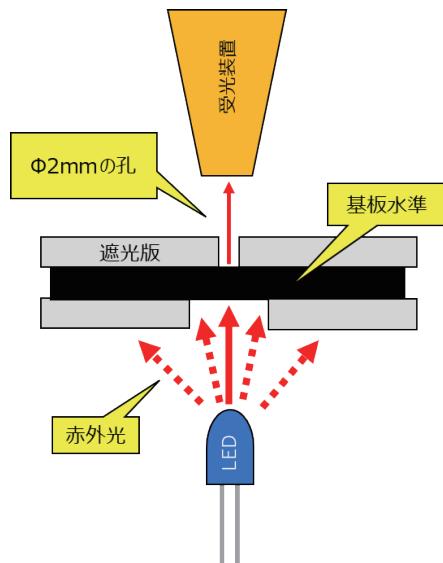

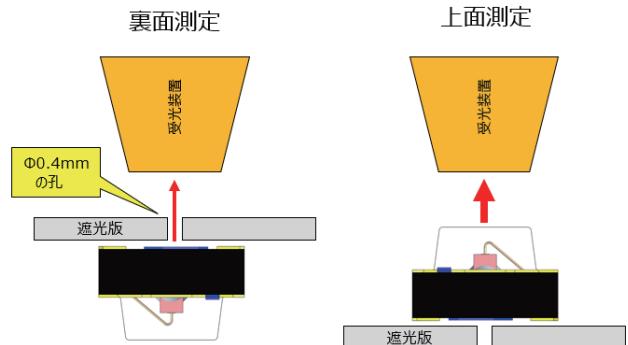

#### 2.4. 漏光防止型赤外チップLEDへの検討

回路基板側への漏光を抑えるために、現行BT基板よりも赤外線を透過しにくい赤外チップLEDの基板材質へ変更することを検討した。

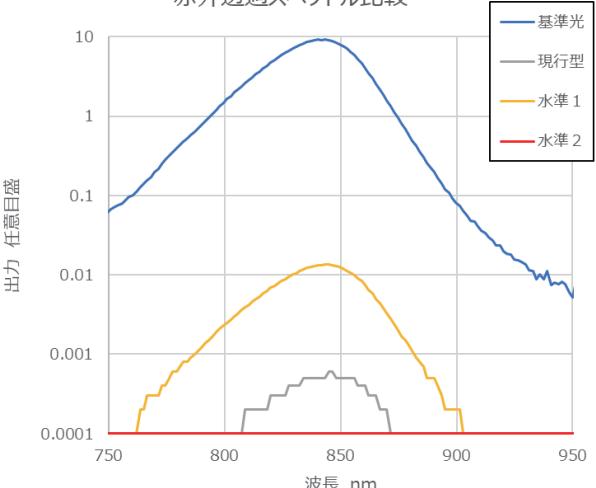

各水準を表1に示す。基板の光透過特性を確認するため、図3のような構成をとり、赤外光 ( $\lambda_p = 850\text{nm}$ ) を使用して、 $\Phi 2\text{mm}$ の孔を透過するスペクトル積分値を比較した。なお、基板なしの状態を基準スペクトルとした。

結果は表1と図4の通りで、BT基板の現行型と水準1の黒色型では基準スペクトル比がゼロにはならず、水準2のFR5相当の黒色型のみがゼロであった。

水準1と水準2は同じ黒色型の基板であっても、赤外線透過率が異なり、水準2の基板は特にスペクトル範囲650～1300nmの光を吸収するように設計されている。よって、水準2の基板を採用し赤外チップLEDを設計した。

表1 基板の水準

|     | 材質    | 色  | 厚さ    | 基準スペクトル比 |

|-----|-------|----|-------|----------|

| 現行型 | BT    | 白色 | 0.5mm | 0.006%   |

| 水準1 | BT    | 黒色 | 0.5mm | 0.154%   |

| 水準2 | FR5相当 | 黒色 | 0.5mm | 0.000%   |

図3 スペクトル透过測定方法

#### 赤外透過スペクトル比較

図4 透過スペクトル

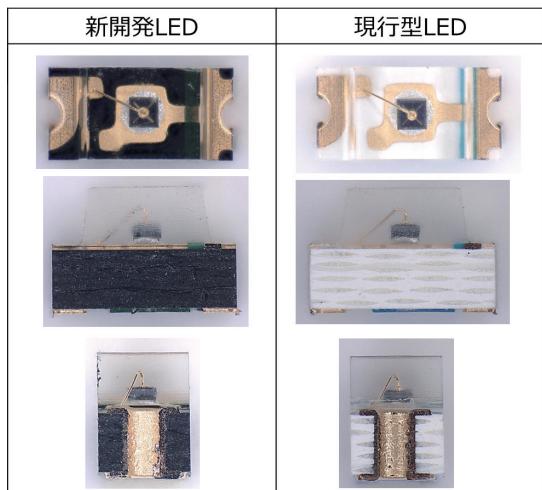

#### 2.5. 赤外チップLEDの外観・発光状態

完成した新開発チップLED（以下開発LED）の外観を図5左側、現行型LEDを右側へ示す。開発LEDは材質が黒色のため、金メッキのパッドパターンの輪郭が目立つ。

発光状態を比較した様子を図6に示す。各チップLED上面を中心とした発光状態は、透明封止樹脂内で拡散・多重反射した一部の光は基板方向へ拡散している。現行型LEDでは、拡散した赤外光が基板内へ浸透し、その一部は基板側面より漏光するため、基板のガラス繊維とBT樹脂の層構造が観察可能である。

しかし新開発LEDでは、ガラス繊維と黒樹脂の層構造が全く観察できない。これは、基板が赤外光を吸収しているためと判断する。

図5 チップLEDの外観比較

図6 チップLEDの発光状態比較

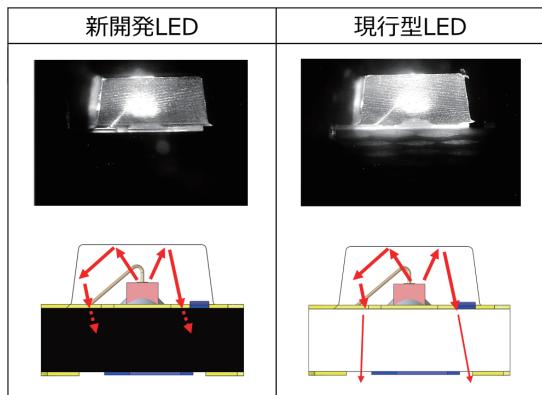

## 2.6. チップLEDの漏光特性

次に、各チップLEDの裏面側からの漏光を調査した。測定方法は図7の方法をとり、上面側と裏面側の光出力を各5個ずつの比較とした。なお、裏面測定時は上面側からの光の反射、回り込みを防止するため、Φ0.4mm孔からの透過光のみを測定した。

結果は表2に示す。

水準2では、裏面出力は測定限界値以下でほぼゼロとなり、現行型と比べ2桁以下であった。つまり、回路基板への漏光を防止可能と判断する。

一方で、水準2のトレードオフとしては、赤外チップ

図7 チップLEDの出力測定

表2 チップLEDの出力比較

| 基板         | No         | 上面出力<br>mW  | 裏面出力<br>mW   | 上面<br>出力比     |

|------------|------------|-------------|--------------|---------------|

| 現行型<br>LED | 1          | 59.7        | 0.009        | 0.015%        |

|            | 2          | 65.7        | 0.010        | 0.016%        |

|            | 3          | 60.3        | 0.007        | 0.011%        |

|            | 4          | 75.1        | 0.011        | 0.014%        |

|            | 5          | 50.4        | 0.012        | 0.023%        |

|            | <b>AVG</b> | <b>62.2</b> | <b>0.010</b> | <b>0.016%</b> |

| 新開発<br>LED | 1          | 47.5        | 0.000        | 0.000%        |

|            | 2          | 42.2        | 0.000        | 0.000%        |

|            | 3          | 40.0        | 0.000        | 0.000%        |

|            | 4          | 48.1        | 0.000        | 0.000%        |

|            | 5          | 43.6        | 0.000        | 0.000%        |

|            | <b>AVG</b> | <b>43.6</b> | <b>0.000</b> | <b>0.000%</b> |

LEDの基板が光を吸収するため上面出力が低下する。(約70%に減衰する)

## 3. むすび

光(赤外線)吸収基板を用いて、裏面漏光防止型赤外チップLEDを開発した。標準的な信頼性試験も完了し、現行型と置き換えが完了できる見込みである。

今後は上面出力を低下させない構造や材料の検討、受光素子との組み合わせモジュール等の提案をしていきたい。

# RGB 蛍光体を用いた RGB-LED の開発

## Development of RGB-LEDs using RGB-Phosphors

梅津陽介\*

Umetsu Yousuke

**概要** 車室内の間接照明としてRGB-LEDが普及しているが、RGBチップの発光をそのまま使うため、RGB単色および中間色の色ばらつきが大きい。今回、RGBの蛍光体を用いてこれらの色ばらつきを抑制した。また、温度特性や大電流領域での明るさ低下を改善し、ハイパワー化にも対応できるRGB-LEDを開発したので紹介する。

### 1. まえがき

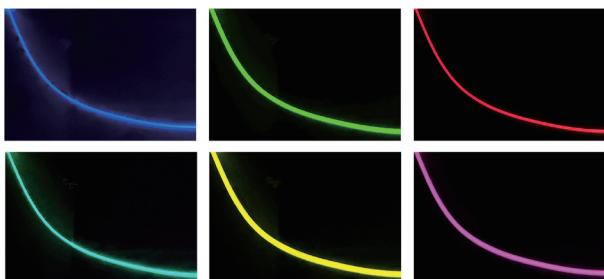

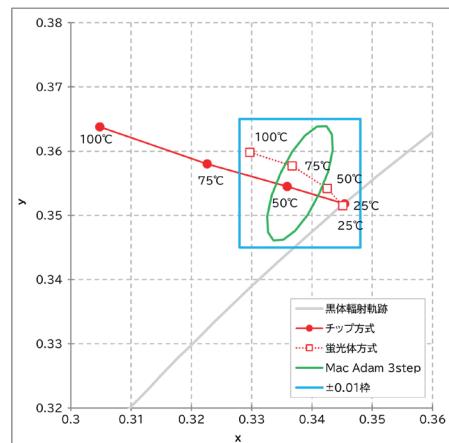

LED (Light Emitting Diode) は照明やディスプレイをはじめ、我々の生活空間に幅広く普及し、LEDによる光を目にする日はない。近年、自動車用のRGB-LEDが普及している。車室内の雰囲気を演出する照明が主流だが、自動運転のレベルに合わせたLEDが車内外でも必要とされる。図1にライトガイドを用いたRGB照明の例を示す。

図1. RGB-LEDによる演出の例

白色LEDは、InGaNの青色チップと黄色蛍光体や赤色蛍光体を用いて白色に発光している。一方、RGB-LEDはAlGaInPの赤色チップとInGaNの青色チップ、緑色チップを使用するのが主流である（チップ方式と呼ぶ）。一方で、蛍光体変換（Phosphor converted : PC）を用いたアンバー色LED<sup>1)</sup>や赤色LED<sup>2)</sup>は実用化されているが、同一パッケージで蛍光体によりRGB発光す

るLEDでは例がない。

今回はRGB全て蛍光体を用いた（蛍光体方式と呼ぶ）RGB-LEDを検討し、次の3つの課題を解決した。

- ①RGBチップの色ばらつきが大きい（現状では色ばらつきを抑えるためにソフトウェア上で微妙な調整をしている）。

- ②温度変化による色変化が大きい（温度変化に対してもソフトウェア上で調整している）。

- ③昼間でも視認できるハイパワー化の要求がある。

### 2. チップと蛍光体の波長ばらつき

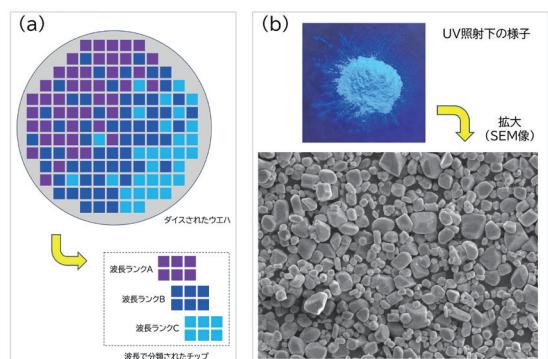

チップはウエハプロセスで作られるが、構成元素の組成比率や膜厚の不均一さによって、電気特性、光出力、発光波長がばらついてしまう。そのため、ダイスされたチップを一個一個測定し、ランク分けして使われている。ウエハ面内のチップにおける波長ばらつきを波長別にランク分けした概念図を図2(a)に示す。

図2. (a) チップの波長ランク分け概念図と、(b) 蛍光体の写真

\*技術開発本部 ハーネルバイス開発統括部

オプト技術部 LED 開発課

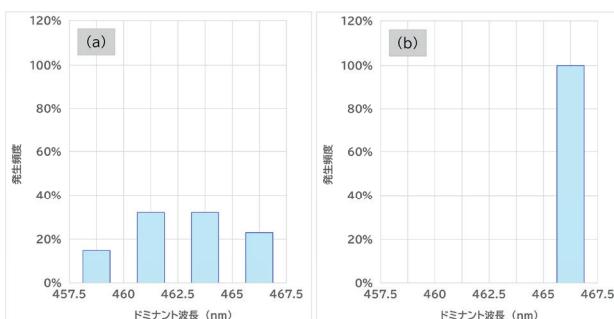

例として、青色チップの波長ばらつきの発生分布を図3(a)に示す。一般的な青色LEDは波長のばらつき幅が10nmを超える、2.5nm幅でランク分けされている。

一方、図2(b)に示すように蛍光体は5~20μm程度の粉末の集まりで、数百g程度の原材料を容器(るつぼ)に入れて焼成する。焼成後は複数のるつぼから取り出された蛍光体を粉碎、洗浄、粒径調整、混合工程などを経て製品化される。混合工程を経ることで、特性が多少異なる粉末も均一化される。そのため、ロット全体としての波長ばらつきは極めて小さい。

一例として、液晶バックライトに使われた冷陰極管(Cold Cathode Fluorescent Lamp:CCFL)で使用された青色蛍光体BaMgAl<sub>10</sub>O<sub>17</sub>:Eu<sup>2+</sup>の波長ばらつきを図3(b)に示す。青色チップと比較するため2.5nm幅でグラフを描いたが、実際は467.0~467.5nmの分布幅0.5nmに収まり、蛍光体の波長ばらつきはチップと比べて極めて狭いことがわかる。

図3. (a) 青色チップと (b) 青色蛍光体の波長ばらつき

### 3. 単色の色度ばらつき低減

チップ方式では蛍光体を使う必要はない、透明なシリコーン樹脂等で封止するだけで良い。しかし、蛍光体方式ではRGBそれぞれ異なる蛍光体を使う必要がある。チップ方式では封止する樹脂で色度ばらつきを変えることはできないが、蛍光体方式では蛍光体の量で色度ばらつきを抑えることができる。以降、蛍光体方式をRGB各色に分けて説明する。

#### 3.1. 蛍光体方式赤色(PC-Red) LED

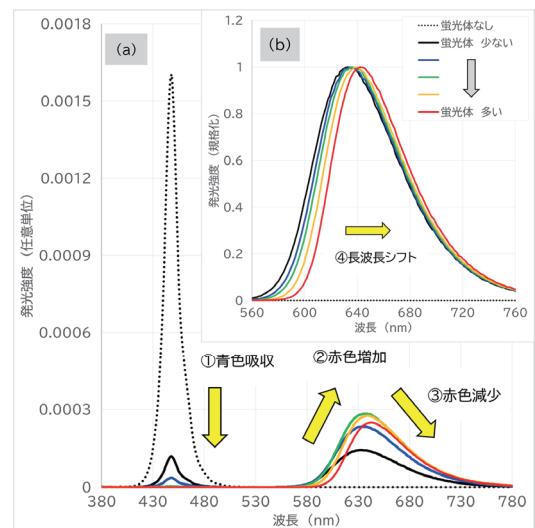

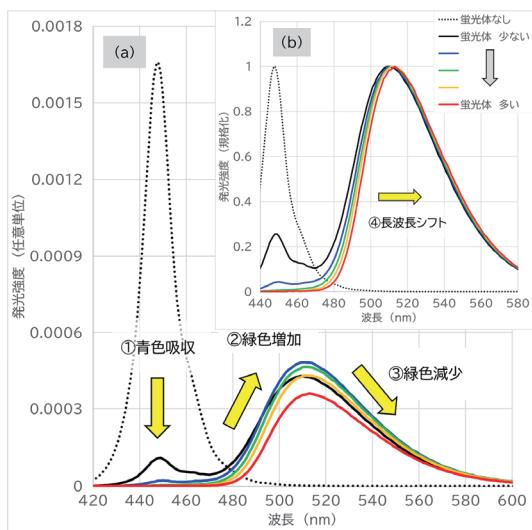

シリコーン樹脂と赤色蛍光体(Sr,Ca)AlSiN<sub>3</sub>:Eu<sup>2+</sup>を混練した蛍光体樹脂を青色チップに実装した。蛍光体の混合量を変えたときの発光スペクトルを図4に示す。チップからの青色光は赤色蛍光体により吸収されるため、

- ①蛍光体が多くなると青色発光は減少する。

- ②蛍光体は青色光を吸収して赤色に波長変換するため、

- 蛍光体が多くなると赤色発光は強くなる

- ③蛍光体がある量を超えると赤色発光は低下に転ずる。いわゆる濃度消光である。

- ④さらに蛍光体が多くなると、自らの発光(特に短波長側)を吸収し、長波長に発光すること(再吸収励起過程)によって発光波長は長波長にシフトする。

図4. (a) 青色チップに赤色蛍光体を実装した発光スペクトル

(b) 赤色の発光ピークで規格化した発光スペクトル

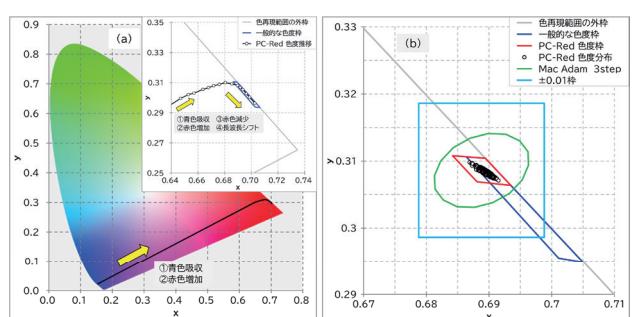

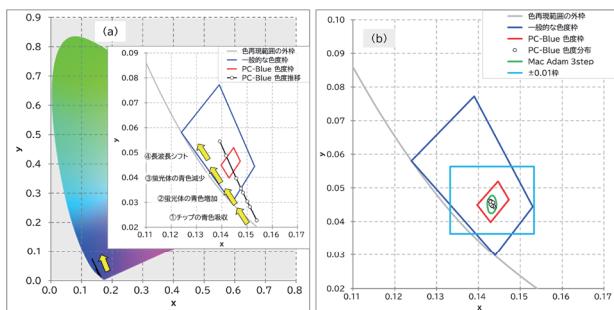

これらの現象によって、CIE色度座標上では青色から赤色方向に色度が動き、色が再現できる範囲を示す外枠に近くなるとその外枠に沿うような動きをする(図5(a))。蛍光体の量によってPC-Red LEDの色度は変わることが、蛍光体の量を均一にすることで色度ばらつきを抑えることができる。

図5. (a) 蛍光体の量を変えたときのPC-Redの色度推移と、

(b) 色度発生分布

図5(b)に開発目標である色度±0.01枠と、人間の目視で色の違いが分りにくいMac Adam 楕円の3ステップと、PC-Red LEDの色度分布を示す。この色度分布はMac Adam 楕円3ステップに収まることができる。この

色度分布が収まるようにPC-Redの色度枠（赤線）を決めた。赤色LEDの一般的な色度枠は波長で9nmの幅であるのに対して、PC-Redの色度枠は波長3nm幅にすることが可能であり、波長ばらつきは3分の1に抑えることができる。

### 3.2. 蛍光体方式緑色 (PC-Green) LED

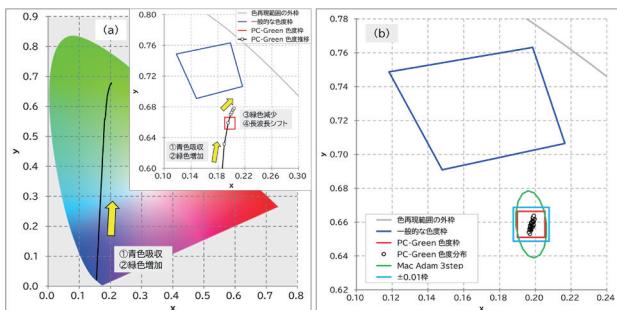

シリコーン樹脂と緑色蛍光体 $\text{Ca}_8\text{Mg}(\text{SiO}_4)_4\text{Cl}_2:\text{Eu}^{2+}$ を混練した蛍光体樹脂を青色チップに実装した発光スペクトルを図6に示す。

図6. (a) 青色チップに緑色蛍光体を実装した発光スペクトル

(b) 緑色の発光ピーク強度で規格化した発光スペクトル

PC-Redと同様に以下の現象が起きる。

- ①蛍光体が多くなると青色発光は減少する。

- ②蛍光体が多くなると緑色発光は強くなる。

- ③ある量を超えると緑色発光は低下する。

- ④さらに蛍光体が多くなると発光は長波長シフトする。

図7. (a) 蛍光体の量を変えたときのPC-Greenの色度推移と、

(b) 色度発生分布

図7(a)に示すように色度座標上では青色から緑色方向に色度が動く。使用した緑色蛍光体の発光半値幅が広

いため、緑チップと比べると色が再現できる範囲の外側に近いところまで色度は動かない。蛍光体の量が多くなると色度の動きは小さくなることがわかり、蛍光体の量を均一にすることで、色度のばらつきを抑えることができる(図7(b))。

PC-Greenの色度分布はPC-Redと同様に色度±0.01枠とMac Adam 楕円3ステップ内に収まる。この色度分布が収まるようにPC-Greenの色度枠（赤線）を決めた。緑色LEDの一般的な色度枠は波長15nmの幅であるのに対して、PC-Greenの色度枠は3nm幅にすることが可能であり、波長ばらつきは5分の1に抑えることができる。

### 3.3. 蛍光体方式青色 (PC-Blue) LED

青色チップと青色蛍光体を組み合わせた例は少ない。チップの色ばらつきは抑えようがないという考え方方が強いが、一方で青色蛍光体を用いて青色チップの色ばらつきを抑える技術が知られている<sup>3)</sup>。

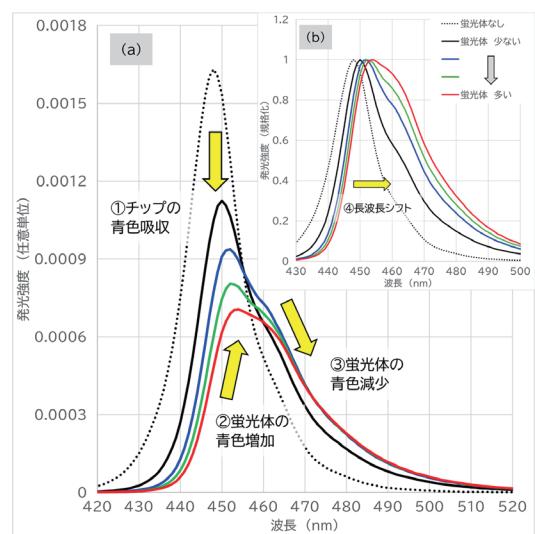

シリコーン樹脂と青色蛍光体 $\text{Sr}_3\text{MgSi}_2\text{O}_8:\text{Eu}^{2+}$ を混練した蛍光体樹脂を青色チップに実装した発光スペクトルを図8に示す。青色チップと青色蛍光体の発光スペクトルが重なっているが、PC-RedやPC-Greenと同様に以下の現象が起きている。

- ①蛍光体が多くなるとチップの青色発光は減少する。

- ②蛍光体が多くなると蛍光体の青色発光は強くなる。

- ③ある量を超えると蛍光体の青色発光は低下する。

- ④さらに蛍光体が多くなると発光は長波長シフトする。

図8. (a) 青色チップに青色蛍光体を実装した発光スペクトル

(b) 青色の発光ピーク強度で規格化した発光スペクトル

色度座標上では青色領域で直線的に動き(図9(a)), 蛍光体の量を均一にすることで色度のばらつきを抑える

ことができる(図9(b))。

PC-Blueの色度分布も色度±0.01枠とMac Adam 楕円3ステップ内に収まるが、赤色領域や緑色領域に比べて青色領域はMac Adam 楕円が小さい(表1)。そのため、PC-Blueの色度枠はMac Adam 楕円3ステップよりもやや大きい色度枠(赤線)とした。

青色LEDの一般的な色度枠は波長10nmの幅であるが、PC-Blueの色度枠は2nm幅にすることが可能であり、波長ばらつきは5分の1に抑えることができる。

図9. (a) 蛍光体の量を変えたときのPC-Blueの色度推移と、

(b) 色度発生分布

表1. PC RGB-LED の Mac Adam 楕円3ステップの色度幅

|      | x     | y     |

|------|-------|-------|

| 赤色領域 | 0.015 | 0.011 |

| 緑色領域 | 0.017 | 0.040 |

| 青色領域 | 0.002 | 0.005 |

#### 4. 色再現範囲の拡大

RGB-LEDの色ばらつきを抑えるためチップの発生分布の内側で基準色を作る方式が用いられている<sup>4)</sup>。具体的には、RGB単色の色度ばらつきの上下限の組合せで得られる三角形を色再現範囲とし、その三角形の頂点を基準点とする。緑色を例にとると、青LEDと赤LEDを微弱に発光させることで緑色の基準色(基準点)を演出する。

一般的なRGBチップ方式は波長4~5nm刻みでランク分けされている。そのため、複数ランクの組合せ毎に微弱に発光させる量を変える必要があり、ソフトウェア上の設定をランク毎に変えなければならない手間が課題であった。

しかし、これまでの結果から蛍光体方式では、RGB単色において開発目標である±0.01枠と人間が目視で色の違いが分りにくいMac Adam 楕円3ステップ内に収まる。そのため、RGBそれぞれを単ランクで、しかも基

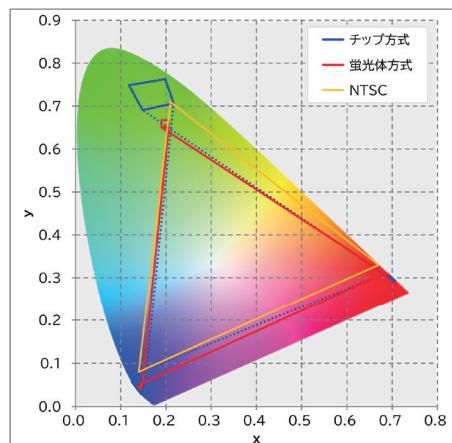

図10. 色再現範囲の比較

準点として使用することが可能である。

前述のように求められる三角形の面積を、色再現範囲として良く用いられるディスプレイのNTSC規格と比較した。チップ方式はNTSC比で83.4%，蛍光体方式は95.1%であり蛍光体方式は色再現範囲を広くすることができる(図10)。

#### 5. 白色の色度ばらつき低減

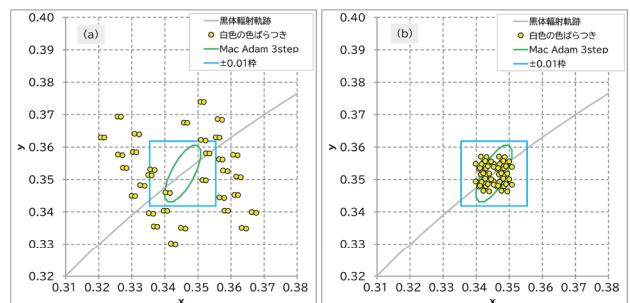

RGB-LEDは、RGBの発光強度を調整して白色や青緑色、黄色、アンバー色などの中間色を演出する。RGBのチップの色度ばらつきをソフトウェア上で調整しない場合、RGBの出力比率は固定され、チップの色度ばらつきによって中間色の色がばらついてしまう。図11は出力比率を固定したときにRGB単色の色度ばらつきがどのくらい白色の色度に影響するかをシミュレーションした結果である。

図11(a)はチップ方式であり、RGBの色度枠(図5(b)、図7(b)、図9(b)の青線)の4点の組合せで得られる $4 \times 4 \times 4 = 64$ 個の色度座標である。図11(b)は蛍光体方式であり、同様に色度枠(図5(b)、図7(b)、図9(b)の赤線)の4点の組合せで得られる64個の色度座標である。

図11. 白色の色度ばらつき (a) チップ方式、(b) 蛍光体方式

蛍光体方式の白色の色度ばらつきが小さいことは明らかであり、 $\pm 0.01$  枠にも十分に収まる。Mac Adam 極円 3 ステップからは少し外れてしまう組合せがあるが、これは前述した図 9 (b) の PC-Blue の色度枠（赤線）が、Mac Adam 極円 3 ステップの外側に余裕をもって設定したためと考える。PC-Blue の色度枠（赤線）を Mac Adam 極円 3 ステップの内側にできれば、中間色の色度ばらつきも Mac Adam 極円 3 ステップ内に収まると考えられる。

PC-Blue の色度枠（赤線）を小さくするには、材料側の改善（青色蛍光体の組成調整や粒度分布の調整など）と蛍光体樹脂の量を均一に実装する製造技術側の改善が挙げられるが、両者ともに改善の余地は十分にあると考えている。

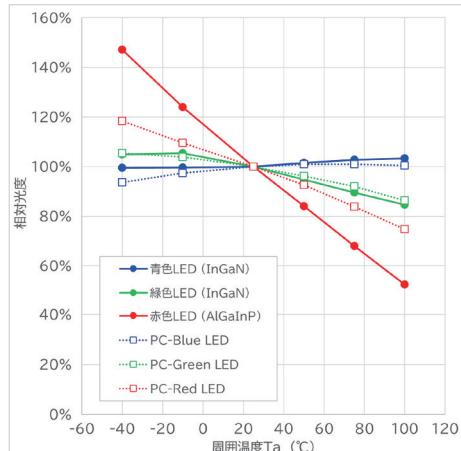

## 6. 温度変化による色度変化

LEDチップはその組成によって温度特性がほぼ決まる。特に赤色チップは温度特性が悪く、温度上昇とともに発光強度が低下する。さらに、発光波長が長波長にシフトし、視感度の低い（暗い）深い赤色発光に変化するために明るさは大きく低下してしまう<sup>5)</sup>。

一方のPC-Redは温度特性の良い青色チップと赤色蛍光体を使用しているため明るさの低下は赤チップより優れる（図12）。

図12. チップ方式と蛍光体方式の温度特性

蛍光体は賦活剤濃度を減らすことによって温度特性を改善することが可能であるが<sup>6)</sup>、賦活剤濃度を減らすと青色光の吸収が低下してしまう。青色光が吸収しきれないと色純度の高い緑色、赤色が出せない。そのため、青色光を吸収する機能を顔料やカラーフィルター（カラーレジスト材）と分担することで、温度特性を改善できる可能性がある。

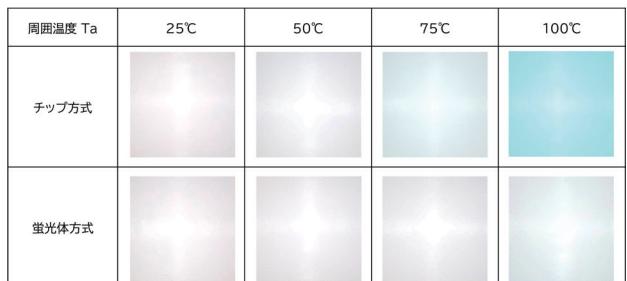

図13. 温度変化による色度変化

図13にチップ方式と蛍光体方式で白色を演出した際の温度変化による色度変化を示す。蛍光体方式は25°Cから100°Cの温度上昇でも $\pm 0.01$  枠内に収まるが、チップ方式はその2倍以上の色度変化があり、見た目でも色変化がわかる（図14）。

図14. 温度上昇によるRGB-LEDの発光色変化の様子

(拡散板を介した発光を写真撮影)

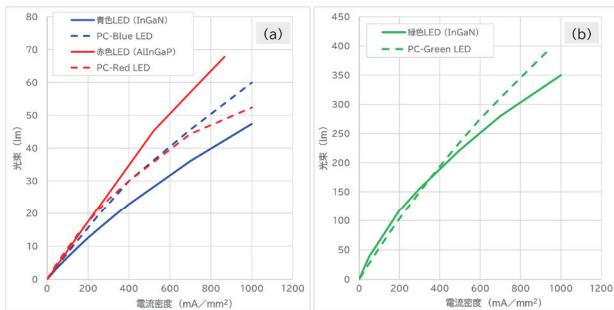

## 7. ハイパワー化への対応

車室内の間接照明は、夜間では綺麗な演出が可能であるが昼間では視認しにくい。また、昼間の走行時に自車の存在を周囲に知らせる昼間点灯 (Daytime Running Light : DRL) が欧州で義務化されている。日本では義務化されていないが、自動運転が普及するにつれ周囲へのアピールは重要になる。そこでRGB-LEDのハイパワー化が今後必要になると考えて検討をおこなった。

LEDのハイパワー化は、大電流に対応できるようにチップのサイズアップが最もシンプルなアプローチである。電流を上げたときの明るさの変化を図15に示す。

青色チップは電流増大に伴い短波長へ発光がシフトする。視感度の低い（暗い）青色発光に変化するため明るさは低下する。しかし、今回使用したRGBの蛍光体は励起波長である青色の波長が短波長になるほど発光強度

図 15. 電流密度と光束の関係 (a) 青と赤, (b) 緑

(印加時間は 10msec で発熱の影響を抑えた)

は増大する。そのため、PC-Blue と PC-Green は青色チップと比べて明るさ低下が小さく、ハイパワーLEDに向いている技術である。

一方のPC-Redは赤チップに比べると25°Cでの明るさは低いが、温度上昇によって明るさが大きく低下するため100°CではPC-Redの方が明るくなる(表2)。ハイパワーLEDは発熱量が大きく、高温動作を強いられるため、高温で明るさが低下しにくい蛍光体方式は有利である。

表2. 溫度上昇による赤色LEDの明るさ(印加時間10msec)

| 周囲温度 $T_a$       | 25°C | 100°C |

|------------------|------|-------|

| 赤色 LED (AlGaInP) | 64lm | 33lm  |

| PC-Red LED       | 47lm | 35lm  |

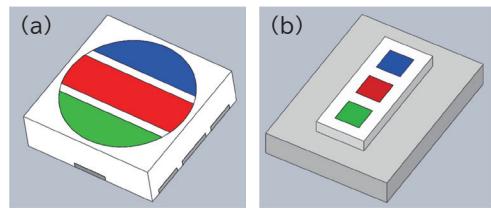

## 8. 製品構想

蛍光体方式はRGBそれぞれに蛍光体樹脂層が必要であり、PC-Redを点灯させた際にPC-GreenやPC-Blueの蛍光体が発光しないように、各蛍光体を遮蔽する必要がある。

LED製品としては、1つのパッケージに3つの部屋がある表面実装(Surface Mount Device:SMD)タイプと、基板に直接チップを実装するCOB(Chip on Board)タイプが挙げられる(図16)。

図 16. (a) SMD タイプ, (b) COB タイプ

前述のハイパワーRGBを実現しようとすると放熱性に優れるCOBタイプが有力である。また、COBは必要な明るさに応じてチップ数を変えることや、電気回路を搭載してモジュール化することも可能である。

## 9. まとめ

RGBの蛍光体を用いたRGB-LEDを開発した。RGB単色の色度ばらつきはチップ方式に対して劇的に抑えられ、白色などの中間色の色度ばらつきも抑制できる。また、温度変化による色度変化も小さく、ソフトウェアでの色調整が不要なRGB-LEDとして期待できる。

今回は上記蛍光体を例にして述べてきたが、蛍光体を変えることによって色度ばらつきや温度特性、発光波長を変えることが可能であり、顧客要求に合わせたRGB-LEDを提供することが可能である。

また、ハイパワー要求に対しても蛍光体方式は大電流かつ高温駆動でも明るさの低下が起きにくい。蛍光体やCOBでのカスタマイズは当社が大事にする「かゆい所に手が届く」製品になると確信する。

## 10. 引用文献

- 1) 日本国 特開 2023-145094 号

- 2) 日本国 特願 2024-056800 号

- 3) 日本国 特開 2017-152522 号

- 4) 杉浦他：豊田合成技報, Vol.61, p.37-39 (2019)

- 5) 梅津：サンケン技報, Vol.56, p.4-01-p.4-06 (2024)

- 6) Y. Umetsu, S. Okamoto, and H. Yamamoto, J. Electrochem. Soc. 155 (2008) J193.

# 非絶縁コンバータ電源 IC STR5M400 シリーズの開発

Development of non-isolated converter power supply IC STR5M400 series

伊藤 公一\*

Koichi Ito

塩津 興一\*\*

Koichi Shiotsu

早川 章\*\*\*

Akira Hayakawa

**概要** 近年、シーリングファン、コーヒーメーカ、除湿・加湿器、掃除機などの小物家電に使用する電源ICにおいては、面実装による小型化、非絶縁化によるフォトカプラレスおよびシステムとして外付け部品点数削減、さらに全負荷領域で高効率化が求められている。本稿ではこれらのニーズを満足するSTR5M400シリーズを開発したので報告する。

## 1. まえがき

照明、シーリングファン、コーヒーメーカ、除湿・加湿器、掃除機などの小物家電に使用する5W以下の小容量領域の電源には、非絶縁バックコンバータが使用され、絶縁トランジスタやフォトカプラを不要としている。このため、小型で低コスト、高効率となっている。

この負荷領域の電源ICの市場動向としては、省人化のため面実装、小型化のため基板面積縮小、コスト低減のため負荷容量に合わせた部品選定が主流となっている。

市場動向を踏まえて、STR5M400シリーズでは、部品点数削減、全負荷領域高効率化を図っている。また、多種多様なアプリケーション用途に対応するため、出力電圧、動作周波数、出力電力容量を変えた豊富なラインナップを取り揃えている。本稿では、これらのニーズを満足するSTR5M400シリーズを開発したので報告する。

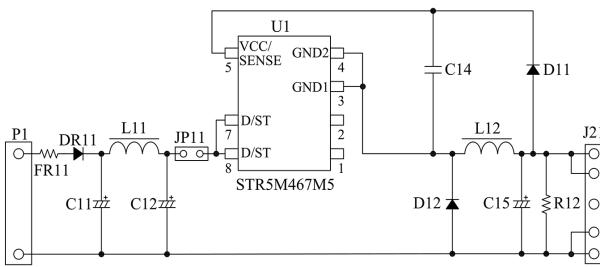

## 2. 製品概要

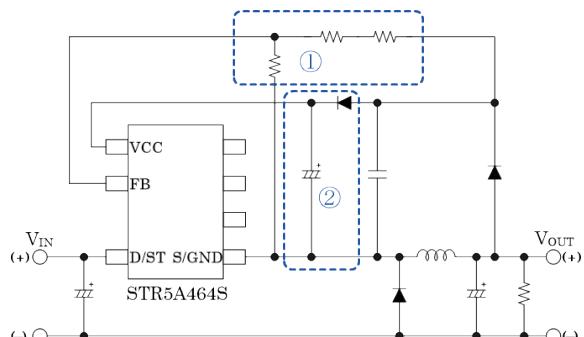

STR5M400シリーズは、制御チップと高圧700VパワーMOSFETを面実装タイプのSOIC8パッケージに搭載した電源ICである。既存量産品STR5A464S<sup>1)</sup>に対して、部品点数5点の削減を実現した。図1で示すSTR5A464Sの電源構成図において、①部分のフィードバック(FB)

検出抵抗(出力電圧設定抵抗)と、②部分のダイオードおよび電解コンデンサをVCC端子とFB端子を1つに共通端子化することで削減でき、図2で示すようにシンプルな電源構成を可能とした。

図2の③部分のコンデンサにおいては、VCC端子とFB端子を共通化したVCC/Sense端子への適用を検討した。その場合、既存量産品STR5A464SでOLP遅延時間を確保するため使用していた10μF以上の容量を使用すると、応答性が悪化するため低容量化が課題であった。

図1 既存量産品STR5A464S電源構成図

図2 STR5M400シリーズ電源構成図

\*サンケンエレクトリック

\*\*技術開発本部ワーティス開発統括部

電源IC開発部開発1課

\*\*\*技術開発本部ワーティス開発統括部

電源IC開発部電源制御開発課

この課題を解決するため内部回路の見直しをおこなった結果、低容量のものを使用しても遅延時間を正確に確保し、応答性との両立を実現した。

本シリーズのラインナップは、多種多様なアプリケーション用途に対応できるよう、表1に示すように各特性仕様を組み合わせたものを取り揃えている。

表1 STR5M400シリーズラインナップ

| 製品名        | V <sub>OUT</sub><br>[V] | f <sub>s</sub><br>[kHz] | R <sub>DSON</sub><br>Max.<br>[Ω] | I <sub>O</sub><br>[A] | GM |

|------------|-------------------------|-------------------------|----------------------------------|-----------------------|----|

| STR5M467H4 | 14.2                    | 100                     | 16                               | 0.10                  | —  |

| STR5M467H3 | 13.0                    | 100                     | 16                               | 0.10                  | —  |

| STR5M467M5 | 15.0                    | 60                      | 16                               | 0.25                  | ○  |

| STR5M422M5 | 15.0                    | 60                      | 3                                | 0.40                  | ○  |

| STR5M422M2 | 12.0                    | 60                      | 3                                | 0.40                  | ○  |

注：構想品を含む

※ GM：グリーンモード 軽負荷発振周波数低減機能

### 3. 製品特徴

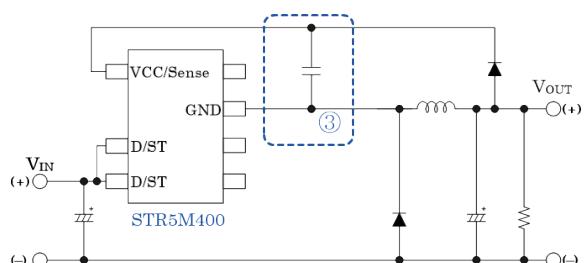

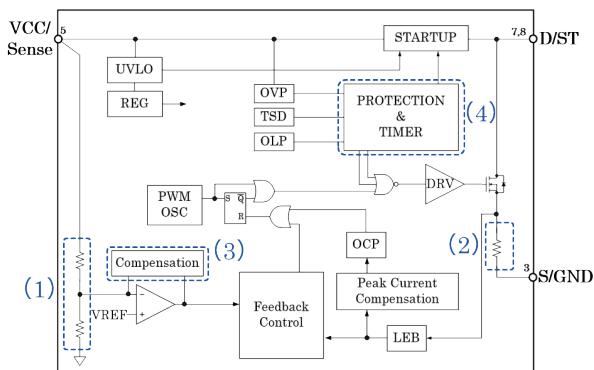

図3に本ICのブロック図を示す。本製品は主に以下(1)～(4)の4つを内蔵したことを特徴とする。

- (1) フィードバック抵抗

- (2) 電流検出抵抗

- (3) 位相補償

- (4) 過負荷保護(以下、OLPとする) タイマ

図3 ブロック図

#### 3.1. フィードバック抵抗

フィードバック抵抗は、図3の(1)にあたる。抵抗を内蔵することで周辺部品の削減ができる、またユーザ側が個別に定数設定をおこなう手間を省くことができる。

#### 3.2. 電流検出抵抗

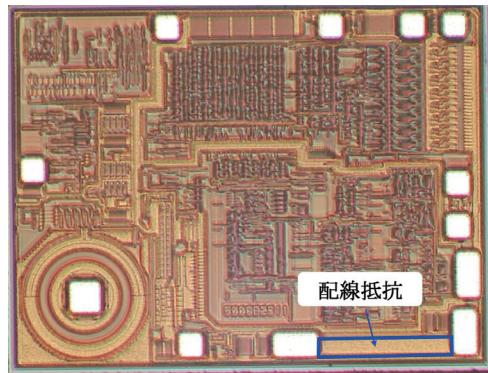

電流検出抵抗は図3の(2)にあたり、図4に示す制御チップ上の配線抵抗を使用している。配線抵抗はアルミニウムで形成され、一般的に100°Cの温度上昇で30%以上

図4 制御チップ写真

の温度特性をもつため、弊社独自の技術でこの温度特性を打ち消す補償をおこなっている。本ICは、電流モード制御方式を採用しており、電流検出抵抗により電流情報を検出する。また、過電流状態もこの検出抵抗で検出する。この抵抗を内蔵することで図3の(2)と同様に周辺部品の削減ができる、またユーザ側が個別に定数設定をおこなう手間を省くことができる。なお、本ICは弊社既存高圧プロセスに対して低コスト化をおこなった最新高圧プロセス<sup>2)</sup>を使用した電源ICとして初の製品である。

#### 3.3. 位相補償

本ICには、エラーアンプ部分に位相補償回路を内蔵している。この位相補償回路は、非絶縁バックコンバータの出力コンデンサが低容量から大容量まで(約10μF～470μF)対応でき、低ESRのセラミックコンデンサにも対応できるように補償している。また、ユーザ側が個別に定数設定をおこなう手間を省くことができる。

#### 3.4. OLP タイマ

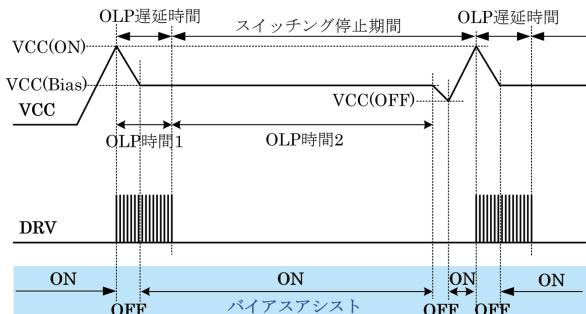

図5にOLP動作時のVCCおよびPower MOSFETのゲート信号DRVのタイミング波形を示す。図中に示すOLP時間1およびOLP時間2はともにICに内蔵しているタイマで時間を決めている。このため、本ICではSTR5A464SのようなVCCコンデンサ容量による影響を受けず、スイッチング停止時間を確保することができる。これにより異常時でのICの温度上昇の抑制を確実におこなうことができる。

なお、図5に示すとおり、OLP時間1およびOLP時間2の間にVCCがVCC(Bias)まで低下するとSTARTUP回路によりバイアスアシストが動作しVCC電圧を保持する。さらに、OLP時間2が終了するとバイアスアシストが停止しVCCがVCC(OFF)を下回ると再びバイアスアシストが動作しVCCを上昇させ、この繰り返しにより、スイッチングが間欠動作する。

図5 OLP動作中のタイミング波形

図6にAC200V時の過負荷保護時の重負荷時動作波形を示す。この間欠動作によりAC265Vでも過負荷保護動作時温度は92.4°Cとなり100°C以下を満足している( $T_a = 60^{\circ}\text{C}$ 想定)。

図6 OLP動作

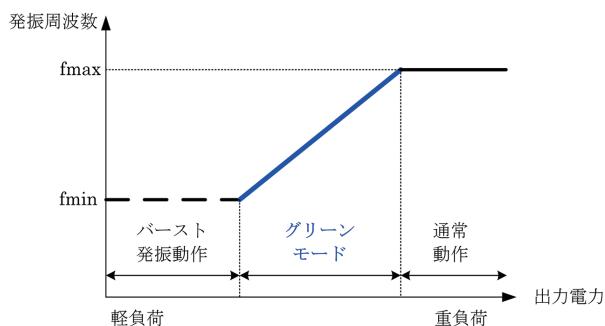

### 3.5. 発振制御

本ICでは、図7に示すように中負荷から軽負荷における電力変換効率を高めるためにグリーンモードを採用している。負荷に応じて発振周波数を自動的に制御し、無駄な電力消費を抑えることで、全負荷領域で高効率な電源設計を可能とした。

図7 グリーンモード動作領域

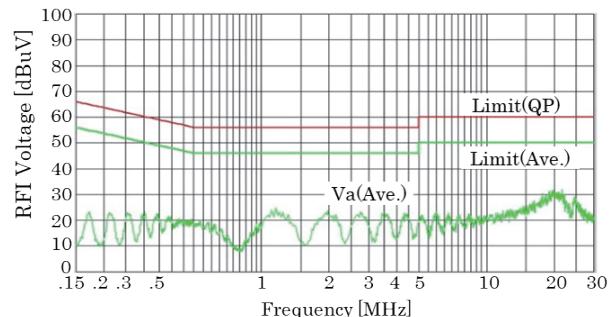

また、PWM平均発振周波数に周波数変動を重畠するランダムスイッチング機能を内蔵し、図8のように入力ラインフィルタなどのノイズ対策部品がない状態でも規格値以内に入るよう設計されている。

Limit (QP) : Quasi-Peak 測定における RFI (無線周波数干渉) 電圧上限値

Limit (Ave.) : 平均測定における RFI 電圧上限値

Va (Ave.) : 測定データ

図8 伝導エミッション試験 (AC200V, CISPR14 規格適用)

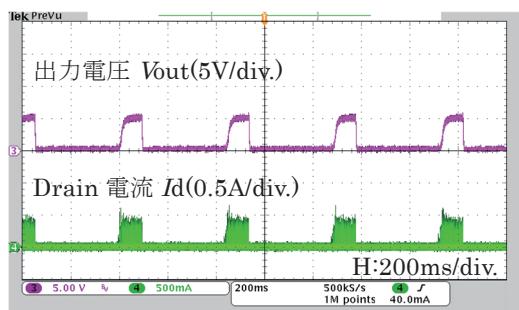

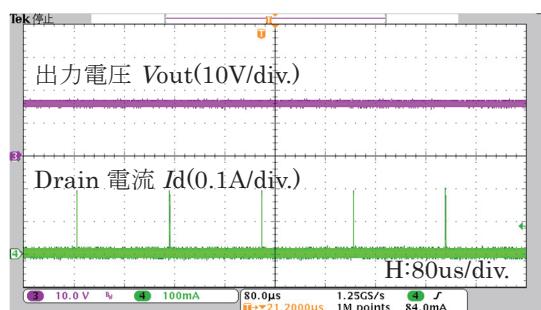

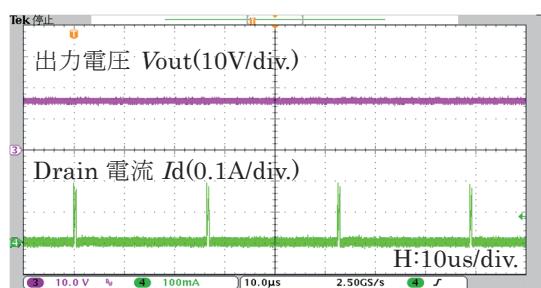

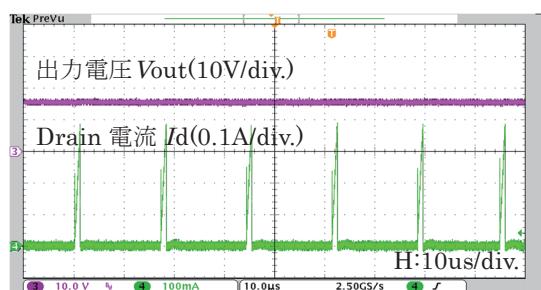

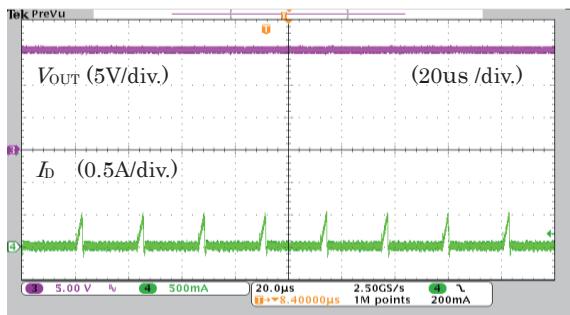

AC200V,  $V_{\text{out}}=15\text{V}$ の条件における $I_{\text{out}}=3\text{mA}$ 時のバースト発振動作波形、 $I_{\text{out}}=25\text{mA}$ 時のグリーンモード波形、 $I_{\text{out}}=200\text{mA}$ 時の通常動作波形を、それぞれ図9、図10、図11に示す。

図9 バースト発振動作

図10 グリーンモード

図11 通常動作

#### 4. 試作評価結果

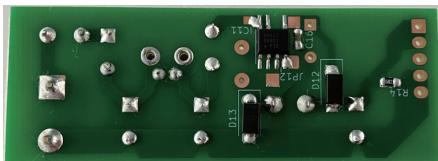

図12に本ICの電源評価ボードの回路図、図13に本ICを実装した電源評価ボード写真を示す。また表2に実装部品の一覧を示し、従来品に対して部品点数42%削減を可能とした。4章では、このボードで電源評価をおこなった結果を報告する。

図12 電源ボードの回路図

(a) 表面

(b) 裏面

図13 電源評価ボード

表2 実装部品の一覧

| 記号  | 部品名                   | 定格                    | 本製品          | 従来品           |

|-----|-----------------------|-----------------------|--------------|---------------|

| C12 | 電解コンデンサ               | 105°C, 400V, 8.2μF    | ○            | ○             |

| C14 | セラミックコンデンサ            | 50V, 0.47μF           | ○            | ○             |

| C15 | 電解コンデンサ               | 105°C, 25V<br>(220μF) | ○<br>(470μF) | ○             |

| C16 | 電解コンデンサ               | 105°C, 50V, 10μF      | —            | ○             |

| D11 | 高速整流ダイオード             | 500V, 1A(SJPD-D5)     | ○            | ○             |

| D12 | 高速整流ダイオード             | 500V, 1A(SJPD-D5)     | ○            | ○             |

| D13 | ショットキーバリア<br>ダイオード    | 60V/1A(SJPD-D6)       | —            | ○             |

| L12 | インダクタ                 | 470μH, 0.6A           | ○            | ○             |

| R1  | チップ抵抗                 | 6.8kΩ, 1/8W, 1608     | —            | ○             |

| R2  | チップ抵抗                 | 33kΩ, 1/8W, 1608      | —            | ○             |

| R3  | チップ抵抗                 | 1.3kΩ, 1/8W, 1608     | —            | ○             |

| R12 | チップ抵抗                 | 6.8kΩ, 1/8W, 1608     | ○            | ○             |

| U1  | PWM オフライン<br>コンバータ IC |                       | STR<br>5M467 | STR<br>5A464S |

#### 4.1. 電源特性

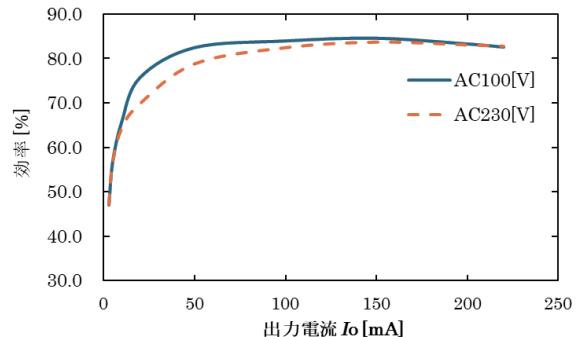

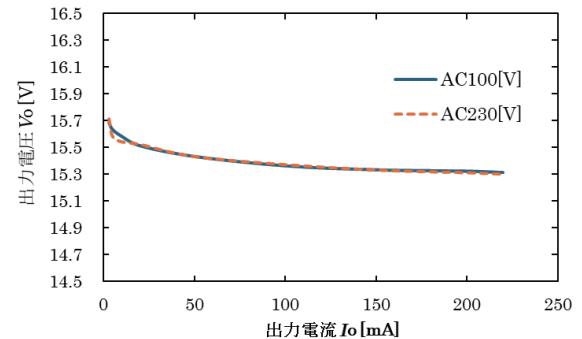

図14に効率特性、図15にロードレギュレーション特性を示す。

図14 効率特性

図15 ロードレギュレーション特性

#### 5. むすび

今回、弊社最新高圧プロセスを使用した電源ICとして初の製品であるSTR5M400シリーズの開発をおこなった。

グリーンモードの採用により軽負荷高効率を実現した。また、チップ上配線抵抗を電流検出抵抗として弊社初として採用し、さらにFB検出抵抗をICに内蔵することで電源の小型化、電源低コスト化が実現した。

今後、新たな市場を開拓すべく大容量化、高効率化に向けてパワーMOSFETのGaNデバイス化をおこない、また2出力化に向けて製品開発を進めていく。

#### 6. 参考文献

- 1) 恒政, 寺澤, 川真田:サンケン技報, vol.46, p29-32 (2014. 11)

- 2) 青木:サンケン技報, vol.55, p22-25 (2023.11)

# 非絶縁フライバック電源 IC STR5A300 シリーズの開発

Development of non-isolated flyback power supply IC STR5A300 series

田畠 鉄哉\*

Tetsuya Tabata

塩津 興一\*

Koichi Shiotsu

早川 章\*\*

Akira Hayakawa

**概要** エアコン、洗濯機、空気清浄機といった白物家電やスマートメーターなどの小容量電源に搭載する電源ICを開発した。これらの機器の電源システムは、低コストおよび省スペース化が重要なポイントとして挙げられ、今後さらに小型化が進むと考えられる。非絶縁用電源向けに高耐圧パワーMOSFETを搭載し、エラーランプを内蔵した電源ICを開発した。本報告では、開発したICの特徴、回路方式の比較、本ICを搭載した電源ボードの特性を紹介する。

## 1. まえがき

現代では、エネルギー資源の消費量を低減するため「省エネルギー」が求められ、省エネルギーは地球温暖化の要因となるCO<sub>2</sub>排出量の削減にも効果が期待される。

日本国内では、特定機器に分類されるエアコンやテレビなどの家電や自動車に対し、トップランナー制度による省エネルギー基準が導入されている。製造事業者はトップランナー規制に対応した機器の製造および供給が義務化されている。家庭用エアコンでは2027年度から新基準が適用となり、さらなる厳しい規格への適合が求められる<sup>1)</sup>。電源ICなどの半導体製品が「省エネルギー」に貢献できる可能性が高まっている状況である。

小容量電源には、設計しやすいフライバック方式が使用されており、絶縁タイプでは出力側からのフィードバック信号を、電圧検知回路とフォトカプラを介し制御する方法が多い<sup>2)</sup>。エアコンなどの白物家電には、筐体が絶縁されたものに対し、電源システムとしては絶縁を不要とし、非絶縁タイプで構成しているものがある。非絶縁タイプの場合、有寿命部品であるフォトカプラが不要となり、信頼性品質の向上といったメリットが挙げられる。

今回、非絶縁用電源向けに高耐圧900VのパワーMOSFETを搭載し、フライバック方式を採用した軽負荷高効率の電源ICを開発した。

本報告では、開発した電源ICの特徴、回路方式の比較、システムの動作原理、搭載した電源ボードの評価結果を報告する。

## 2. 製品概要

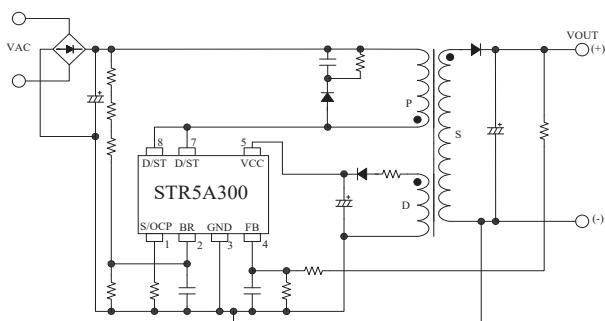

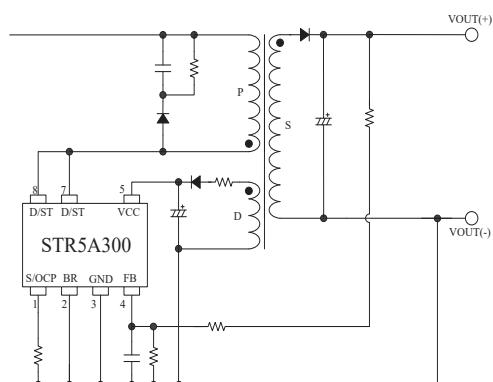

STR5A300シリーズの製品外観と応用回路例を図1、図2、製品ラインアップと端子機能を表1、表2に示す。

全負荷範囲の高効率、無負荷時消費電力が25mW以下を特長としている。パワーMOSFETは電源電圧が不安定な地域も踏まえ、より堅牢性を高めた高耐圧900Vをラインナップした。

パッケージはフライバック方式電源ICとして一般的な挿入実装のDIPと表面実装のSMDを設定している。

表1 製品ラインアップ

| Line up  | $f_{OSC(AVG)}$<br>typ. | $V_{DSS}$<br>min. | $R_{DS(ON)}$<br>max. | $P_{OUT}$<br>(230V/Wide) |

|----------|------------------------|-------------------|----------------------|--------------------------|

| STR5A361 | 100kHz<br>/130kHz      | 700V              | 3.95Ω                | 35W/23.5W                |

| STR5A369 |                        |                   | 6.0Ω                 | 30W/19.5W                |

| STR5A342 |                        | 900V              | 3.0Ω                 | 37.5W/26W                |

| STR5A349 |                        |                   | 6.5Ω                 | 30W/19.5W                |

DIP タイプ

SMD タイプ

図1 製品外観

\*技術開発本部パワーデバイス開発統括部

電源 IC 開発部 開発1課

\*\*技術開発本部パワーデバイス開発統括部

電源 IC 開発部 電源制御開発課

表2 端子機能

| 端子配列 | 記号    | 機能                        |

|------|-------|---------------------------|

| 1    | S/OCP | パワー MOSFET ソース過電流保護検出信号入力 |

| 2    | BR    | 入力電圧検出                    |

| 3    | GND   | グランド                      |

| 4    | FB    | 定電圧制御信号入力                 |

| 5    | VCC   | 制御回路電源入力<br>過電圧保護信号入力     |

| 6    | —     | (抜きピン)                    |

| 7    | D/ST  | パワー MOSFET ドレイン起動電流入力     |

| 8    |       |                           |

図2 応用回路例

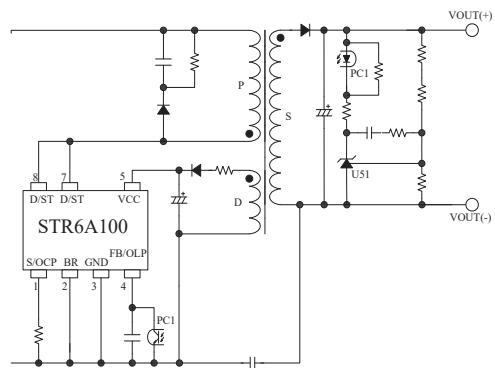

図3 絶縁タイプ（従来製品）

図4 非絶縁タイプ（開発製品）

### 3. 絶縁用の電源構成

図3に従来製品の絶縁タイプ、図4に今回の開発製品STR5A300シリーズの非絶縁タイプのフィードバック周辺部品を示す。電源ICでは、出力側からのフィードバック信号を、電圧検知回路とフォトカプラを介しIC内部制御回路に伝達する。今回の開発製品の非絶縁タイプでは、エラーアンプをIC内部制御回路に内蔵することにより、絶縁タイプでは従来必要であったシャントレギュレータ、フォトカプラなどの周辺部品が不要となる。部品点数としては5点削減できることから、非絶縁タイプを選択できるアプリケーションでは、電源システムの小型化、低コストといった優位性がある。

### 4. 機能と特徴

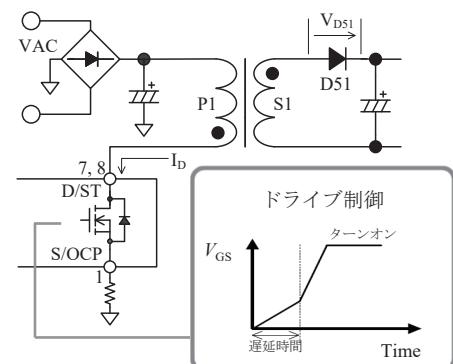

#### 4.1. ステップドライブ制御

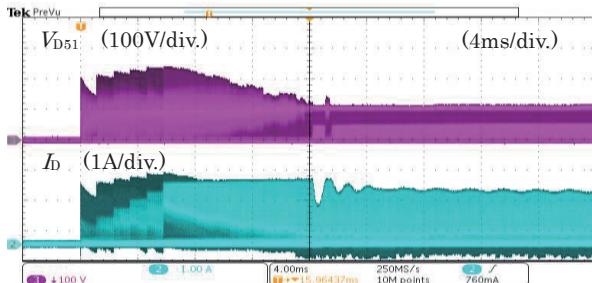

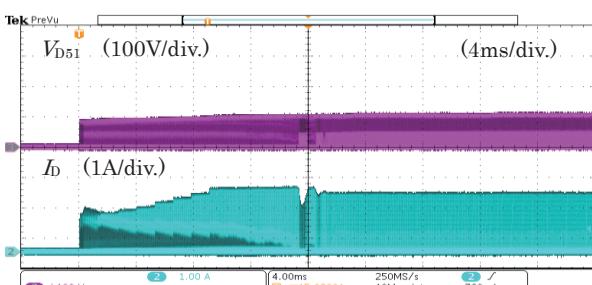

図5にステップドライブ制御動作、図6、図7に起動時のステップドライブ制御有無の波形を示す。

パワーMOSFETのターンオン時、2次側の整流ダイオードD51の両端には、リカバリー電流とインダクタンス成分による逆起電圧がサージ電圧として発生する。整流ダイオードはこのサージ電圧を考慮した耐圧を選定する必要がある。弊社独自技術のステップドライブ制御により、負荷条件に応じて内蔵しているパワーMOSFET

のゲートの立ち上がり時間をIC内部で最適に制御する。これによりターンオン時の整流ダイオードのリカバリー電流の傾斜を抑制し、サージ電圧を低減する。表3のように、ステップドライブ制御により整流ダイオードのVRM耐圧は従来よりも低く設定できるため、低コスト化と低VF化による回路効率の向上が実現できる。

ステップドライブ制御は、過渡条件の状態条件で有効となり、定常動作時は無効となっている。過渡条件と定常動作条件でドライブスピードを切り替え、スイッチングスピードを最適に制御している。結果として、全動作

図5 ステップドライブ制御動作

図6 起動時ステップドライブ制御なし ( $V_{OUT} = 24V$ )図7 起動時ステップドライブ制御あり ( $V_{OUT} = 24V$ )

表3 整流ダイオードVRM耐圧(参考値)

| 出力電圧 | ステップドライブ制御<br>なし | ステップドライブ制御<br>あり |

|------|------------------|------------------|

| 5V   | 100V             | 60V              |

| 12V  | 200V             | 120V             |

| 15V  | 200V             | 120V             |

| 24V  | 400V             | 200V             |

領域においてパワーMOSFETの損失低減、電源の高効率化が実現できる。

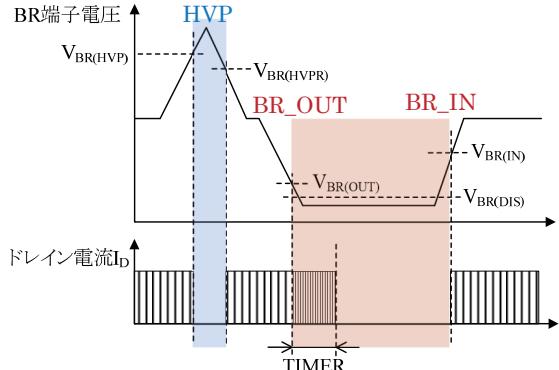

#### 4.2. 入力電圧検出機能

入力電圧検出機能は、電源事情が不安定な地域でも安全に使用できるよう入力電圧が高い場合に働くAC入力過電圧保護機能(HVP)と、アブノーマル状態の電源入力電圧が低い場合に働くブラウンイン・ブラウンアウト機能(BR\_IN・OUT)を同一端子で設定している。入力電圧を随时モニターすることでパワーMOSFETに対し、過入力電圧による損傷を瞬時に抑制し、低入力電圧の一定期間継続による過熱を防止する。

図8にBR端子電圧とスイッチング電流を示す。入力電圧検出機能は、BR端子で入力電圧を検出し、BR端子電圧に応じてスイッチング動作を制御することで各保護へ移行する。入力電圧検出機能を使用しない場合は、BR端子をGNDへ接続し電位を固定することで、機能を無効化できる。

図8 BR端子電圧とスイッチング電流

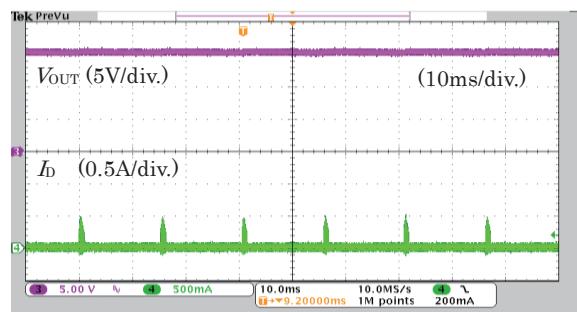

#### 4.3. 低消費電力・全負荷高効率

STR5A361発振周波数100kHzタイプの実測値を報告する。図9に効率測定を実施した評価ボードを示す。無負荷時電力は、絶縁タイプの従来製品と同等の25mW(AC230V)と低消費電力となっている。

今回の開発品の非絶縁タイプのSTR5A300シリーズは、制御ICにエラーアンプ内蔵により回路規模は増加しているが、回路構成の見直しにより従来製品と同等の制御チップサイズを実現している。

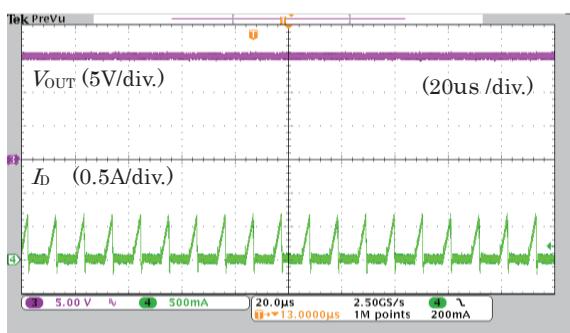

図10、図11、図12に示すようにICの動作モードは負荷電流に応じ、バースト発振動作、グリーンモード(25kHz～100kHz)、通常動作(100kHz)に自動的に切り替わる。

スタンバイ負荷条件まで負荷が減少すると、グリーンモードからバースト発振動作に移行する。グリーンモー

図9 評価ボードの外観

図10 バースト発振動作

図 11 グリーンモード

図 12 通常動作

ドではスイッチング回数を減少、バースト発振動作では一定期間スイッチング動作を停止させることで、スイッチング損失を低減し、変換効率を改善する。

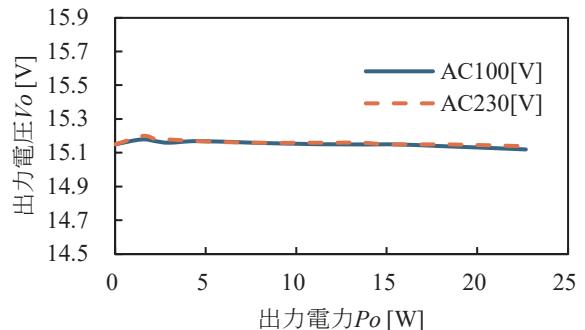

図13に出力電力とロードレギュレーション特性を示す。良好なロードレギュレーション特性を確認した。

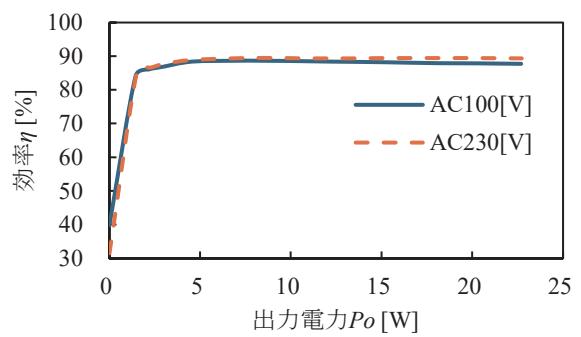

図14に全負荷での効率特性を示す。発振周波数動作制御とドライブ回路の最適化により、出力電力5W～23Wの範囲で88%～89%程度と高い効率を達成した。

## 5. むすび

今回、非絶縁フライバック電源システムに適用できる電源IC STR5A300シリーズを開発した。エラーアンプの内蔵により周辺部品を5点削減し、電源システムの小型化およびコスト化が可能となった。ステップドライブ

図 13 ロードレギュレーション特性

図 14 効率特性

制御と発振周波数制御によって、低消費電力および全負荷領域高効率を実現した。また、パワーMOSFETの高耐圧化や入力電圧検出機能を取り入れており、電源事情が不安定な地域でも安全に使用できる。

今後、様々な電源要求を電源ICで解決し、「省エネルギー」に貢献できるよう製品開発を進める。

## 参考文献

- 1) 資源エネルギー庁 “家庭用エアコンディショナーの新たな省エネ基準を策定しました”, 経済産業省, 2022, <https://www.meti.go.jp/press/2022/05/20220531003/20220531003.html>, (参照 2025-09-18)

- 2) 早川, 田畠 : サンケン技報, 2014, vo.46, p.33-36

# ドッキング接続時の汎用化パフォーマンスボード設計

## Generalized Performance Board Design for Docking Interfaces

木村 将吾\*

Shougo Kimura

真尾 麻美\*

Asami Sanao

**概要** 当社はIPMやパワーマネジメントICなどのパワー半導体を取り扱っている。その半導体製造の前工程の一つであるウェーハテストには品質とスループット向上が常に要求されている。

このスループット向上には「半導体検査装置（ATE：Automated Test Equipment）」や「プローバ」が持つ複数チップを一度に検査する同時測定機能を使用して応える。同時に測定をするチップ数が増えることによりパフォーマンスボードやプローブカードなどのコンポーネントも大型化する傾向がある。大型のコンポーネントを製品毎に製造した場合はコストが増大することから、それを抑制するためにコンポーネントの汎用化設計をおこなった。本稿ではその事例について報告する。

### 1. まえがき

当社はIPM（Intelligent Power Module）やパワーマネジメントICなどのパワー半導体を取り扱っている。そしてそれらの製品に組み込まれる多様な半導体チップの電気的特性や機能などの検査（ウェーハテスト）もおこなっている。

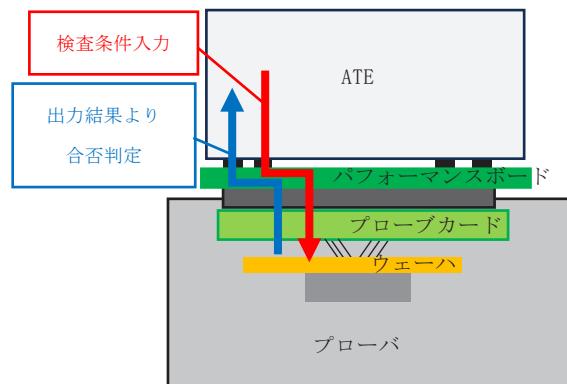

このウェーハテストでは、検査条件を入力し出力結果から合否判定をおこなうATEと、ウェーハの搬送や位置決めなどをおこなうプローバの二つの装置を用いる。しかしこれら装置だけではウェーハテストは成立しない。その他にもパフォーマンスボード（PB：Performance Board）とプローブカードという二つの重要なコンポーネントがある。これらは検査品質や製造工場のランニングコストに大きく関与する。

PBは測定対象チップの検査に必要な電子部品を搭載するインターフェース基板である。PBは電気信号をATEから受けとりプローブカードに渡す。一方、プローブカードはプローブ（探針）を搭載したインターフェース基板である。受け取った電気信号をチップに伝達する役割がある。

ウェーハテストにおいて、これらのインターフェース基板と装置の接続には二つの方式が広く用いられる。それはケーブル接続方式とドッキング接続方式である。

ケーブル接続方式は、その名の通りATEとPBをケーブルで接続する方式である。この接続方式をおこなう場合、ATEはデバイスから数m離れた位置に設置する。

一方、ドッキング接続方式はATEに直接PBを取り付ける（図1）。ケーブル接続方式に比べてデバイスまでの配線が数十cmと短い。そのため配線の寄生容量が小さく測定への影響を抑制することにつながる。さらに、この方式はケーブル接続方式のようなコネクタをほとんど用いない。したがって抜き差しによる接続不具合や断線リスクの低減になる。

利点の多いドッキング接続方式だが課題もある。PBやプローブカードが大型となり基板一枚当たりの製作費用が高額となる。従来、当社ではドッキング接続方式にて機能が異なる製品群毎にPBを設計、製作していた。そのためコスト増となっていた。またATEからデバイ

図1 ドッキング接続方式 模式図

\*技術開発本部プロセス技術統括部

ICデバイス開発部 テスト課

スマートでは構造が非常に密接でオシロスコープのプローブを自由にあてられるスペースがない。よって波形観測は容易ではなく特性評価の効率はケーブル接続方式に比べ低くなる傾向にあった。

## 2. 汎用化PB設計

従来、当社では機能が異なる製品群毎にPBを設計、製作していたが大型基板でありコスト増となっていた。

そこで当社製品の半導体チップを一つのPBで検査する（汎用化）という目標を立てPBを設計した。

### 2.1. 汎用化設計

生産性向上には汎用化とスループット向上を両立させる必要がある。パフォーマンスボードを汎用化することはATE搭載のリソース（電源、計測器、信号線など）をチップの端子へ適切に割り当てて、当社の半導体チップを一つのPBで検査できるようにすることである。

またスループット向上には複数のチップを一度に検査する同時測定機能を使用して、かつ同時測定数の最大化を図る必要がある。そのためにはATE搭載のリソースを無駄なく活用することが重要となる。

以上から汎用化とスループット向上を両立させるにはリソースを適切に割り振ることが設計のポイントとなることが分かる。その方法について検討をおこなった。

一般に半導体チップの電気的特性検査は複数の検査から成る。それらを一連のシーケンスで実行し、このシーケンス全体を考えてすべての端子にリソースを繋ぐ。それに加えて同時測定により複数のチップを検査すると必要なリソース数はさらに増加する。しかしATEの搭載リソースには限度がある。すべての端子に常時リソースを繋ぐと端子数の多い半導体チップでは同時測定数を多くすることはできない。

一方で、一つ一つの電気的特性検査では必ずしも全ての端子に常時リソースを繋いでおく必要はない。適切にリソースを割り振る上で、この点に着目した。ここで重要なことは、各端子における検査条件である。

当社で近年開発した半導体チップの端子と検査条件を分析した。その結果から汎用化とスループット向上を両立できるよう各検査に必要なリソースを割り出し、分岐回路などでリソースを無駄なく端子に割り当てる設計をおこなった。

### 2.2. 高耐圧への対応

当社で取り扱う製品は600Vを超える高耐圧製品のパワー半導体が多く高耐圧の基板設計が必要である。

高耐圧の基板設計には注意すべきことがある。それは

基板内に高耐圧配線パターンを形成した場合、絶縁破壊防止の観点から沿面距離を考慮することである。沿面距離を考慮するということは他の配線パターンや電子部品配置の自由度を下げ、汎用化を妨げる要因となる。そこで高耐圧配線は配線パターンではなく高耐圧用のワイヤーを用いた。これにより沿面距離を考慮する箇所が少くなり、配線パターンや電子部品配置の自由度が高まつた。

### 2.3. 汎用化の効果

以上を踏まえて、汎用性のあるPBを製作した。これによって当社製品のほとんどの半導体チップを一つのPBで検査することが可能となった。

なお汎用化によりPBを複数保管することが不要になり管理工数や保管場所の削減にもつながる。また製品群毎のPB設計の工数が少なくなり検査立ち上げの時間短縮につながる。

しかし製品に特化した専用回路を要求される場合がある。それについては製品に特化した専用回路を実装したPBを設計したので次の章で説明する。

## 3. サブPB設計

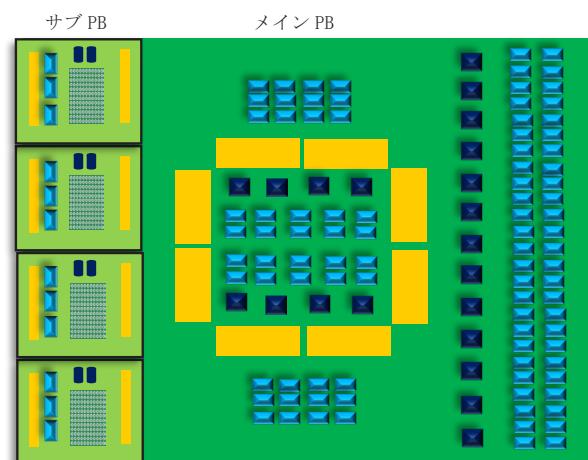

ここまで述べた汎用化設計をおこなったPBのことをメインPB、製品に特化した専用回路を実装したPBのことをサブPBと呼ぶ（図2）。

図2 パフォーマンスボード 模式図

### 3.1. サブPB

サブPBは汎用化したメインPBと組み合わせて使用する。従来は全てのDUT（Device Under Test：被測定対象）分の検査回路を一つのPBに実装していたが、このサブPBはその回路の一部をDUT毎に分離したものである。

特性評価時にはPBの回路修正をおこなう場合が少なからずあるが、全てのDUT分の回路修正を待たずに特性評価ができることが利点の一つである。

またサブPBの設計は一つのDUT分のみでよい。プリント基板での製作により予備基板の製作も容易である。

量産時にも利点がある。サブPBの何れかに故障が発生した場合、予備基板に交換することで速やかに量産への復帰をおこなうことができる点である。

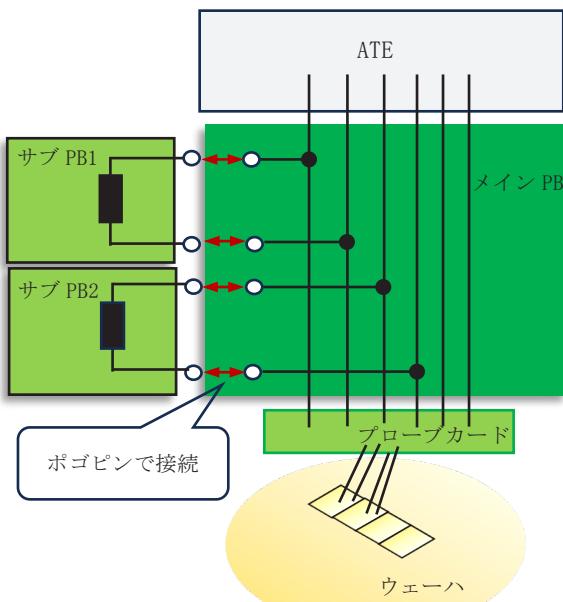

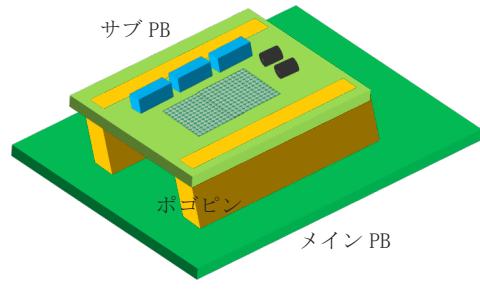

### 3.2. メインPBとサブPBの接続

サブPBはメインPBと組み合わせて使用するが、その接続をするためのポイントは二つある。

一つ目は、メインPBの回路にサブPBの回路を後付けできる設計としたことである。メインPBに予めサブPBと接続可能な配線を配置した（図3）。これによりメインPBの回路を変更せず回路の拡張が可能となる。またメインPBからサブPBへの繋がる配線の長さは電気的特性検査に影響の無い範囲に留めた。

図3 配線模式図

二つ目は、接続不具合を低減したことである。サブPBは製品群毎に設計することを想定した基板であり交換頻度が高い見込みである。そのような交換頻度が高い接続部に機械的寿命が短いコネクタを用いると故障リスクが大きくなる。それゆえ比較して接点が長寿命であるポゴピンを選定した（図4）。

図4 PB接続模式図

### 3.3. 交換作業の容易性

ウェーハテストでは製品群Aから製品群Bに検査対象を変更するときはコンポーネントも交換することが一般的である。当社でも製品群毎にPBとプローブカードを交換していた。しかし大型PBの交換は重量が重く作業効率が悪い。一方、サブPBの基板面積はメインPBの約二十分の一と小型で軽量である。サブPBを交換する方がより作業性が良い。

このようにサブPBをメインPBに後付けできることで製品に特化した検査要求へ柔軟な対応が可能となった。

## 4. モニタPB

ドッキング接続方式はATEと半導体チップとの距離が近いのでケーブルの影響は小さい。反面、一章でも述べたように構造上の理由によりオシロスコープなどの外部計測器での波形観測は容易ではない。それにより特性評価の効率が悪いという課題がある。このような背景から、当社ではモニタPBという観測専用のコンポーネントを製作した。

このモニタPBは特性評価時の波形観測のみPBに取り付ける。また着脱も容易である。この結果、特性評価の効率は飛躍的に向上した。

## 5. 今後の課題

今回汎用化パフォーマンスボード（メインPB）、サブPB、モニタPBを設計した。

しかし、もう一つ重要なコンポーネントの課題がある。それはプローブカードの汎用化である。

プローブカードの汎用化は、PBより複雑である。その一番の要因は高耐圧製品を検査することにある。高耐圧検査では基板沿面距離の確保が必要である。しかしプローブカードはPBに比べ基板寸法と実装可能面積が小さい。さらに汎用化をより難しくしている原因是半導体チップ上の高压端子が多種多様な配列になっていることである。

PB同様に製作コストや開発リードタイム短縮の観点からもプロープカードの汎用化は重要な課題である。複雑ではあるが、引き続き汎用性を高める設計検討を進めます。

## 6. むすび

ウェーハテストで重要なコンポーネントであるパフォー

マンスボードの汎用化設計をおこなった。これにより大型であるメインPBを交換する事や複数枚製作をすることもなくなり作業性は向上し、コストも抑制した。

今後はプロープカードも汎用化設計を進めてさらなるコスト低減をおこない、お客様に満足のいく製品を提供していく。

## 主力製品

### IC製品

パワーマネジメントIC

デジタルパワーマネジメントIC

車載IC

### パワーモジュール・IPM製品

民生・産機IPM

車載IPM

ディスクリートモジュール・アレイ

### ディスクリート製品

パワーMOSFET

IGBT

ダイオード

LED

サンケン技報編集委員会

©2025 Sanken Electric Co.,Ltd.

禁複製転載

委員長 福田光伸

委員 李明濬

赤石和夫

莊裕信

半貫恵司

志賀利貴

小池憲吾

松元貴志

杉田一美

大畠典久

志摩陽一郎

サンケン技報

第57巻

2025年11月20日発行

編集兼発行人 福田光伸

発行所 サンケン電気株式会社

〒352-8666 埼玉県新座市北野3-6-3

URL <https://www.sanken-ele.co.jp/>

電話 048(472)1111(代表)

印刷所 有限会社カムシリング

〒359-0011 埼玉県所沢市南永井570-3

電話 04(2944)1381(代表)