# Mixed Signal MCU MD6603

# **Contents**

| Co | ontents            |                                                                               | C-1          |

|----|--------------------|-------------------------------------------------------------------------------|--------------|

| 1. | Produc             | t Overview                                                                    | 1-1          |

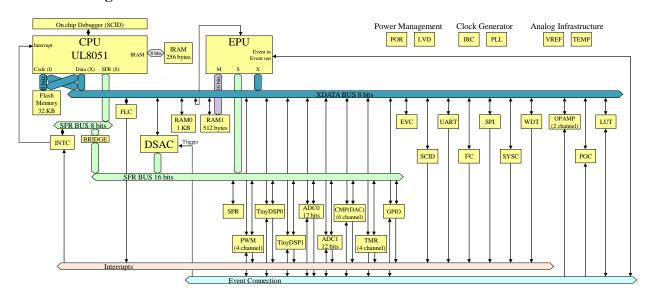

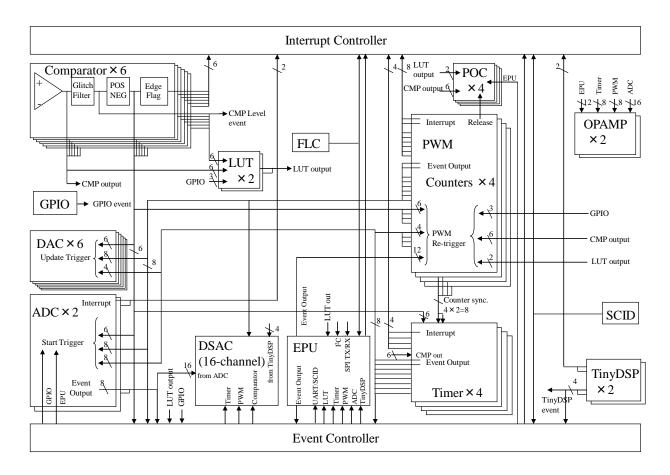

| 2. | Block I            | )iagram                                                                       | 2-1          |

| 3. | Pin Co             | nfiguration Definitions                                                       | 3-1          |

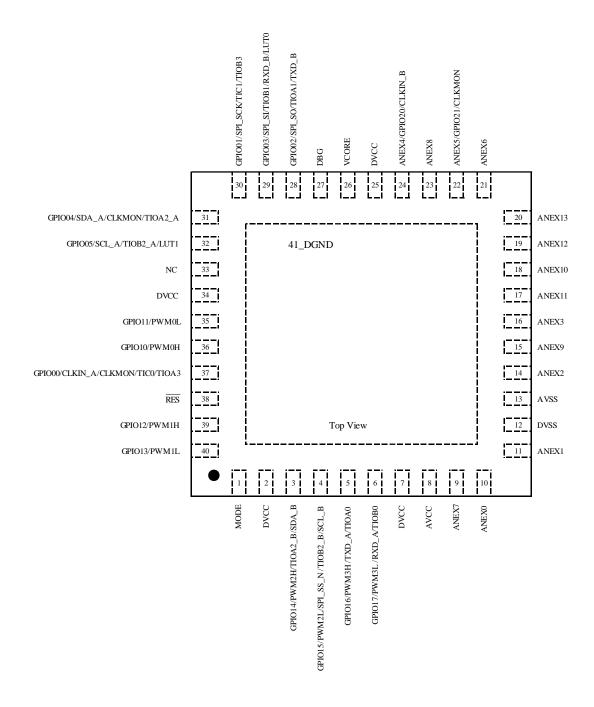

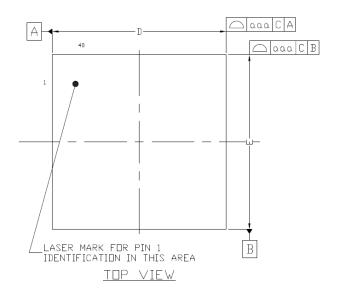

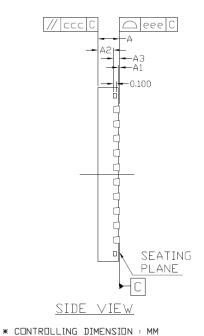

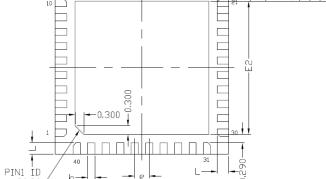

|    | 3.1. Pi            | n Configuration                                                               | 3-1          |

|    | 3.2. Pi            | n Definitions (QFN40)                                                         | 3-2          |

| 4. |                    | Controller (SYSC)                                                             |              |

|    |                    | verview                                                                       |              |

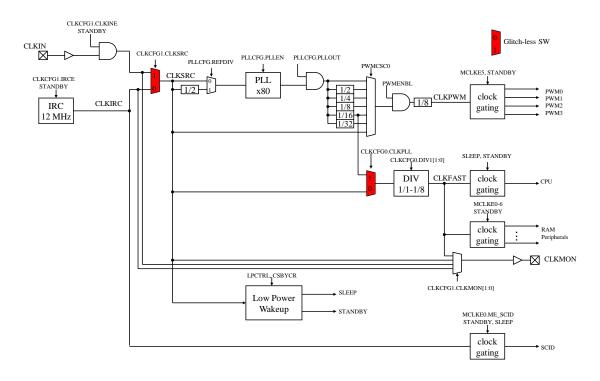

|    | 4.2. Cl            | ock System                                                                    | 4-2          |

|    | 4.2.1.             | Clock Sources                                                                 |              |

|    | 4.2.2.             | PLL Clock                                                                     |              |

|    | 4.2.3.             | Distribution Clocks                                                           |              |

|    | 4.2.4.             | Module Clocks                                                                 |              |

|    | 4.2.5.             | Clock Setting Procedure                                                       | 4-5          |

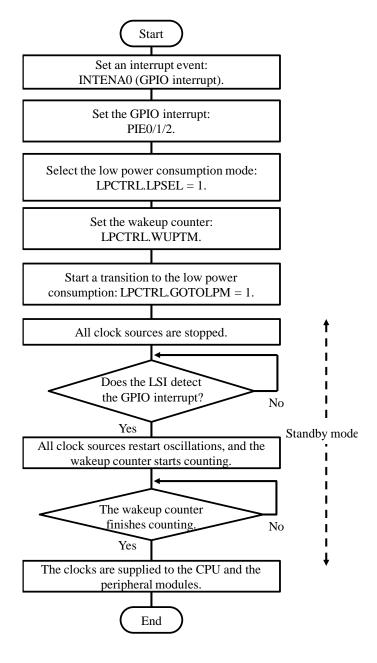

|    |                    | w Power Consumption Modes                                                     | 4-6          |

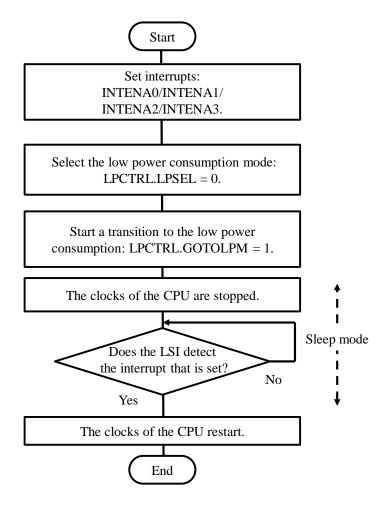

|    | 4.3.1.             | Sleep Mode                                                                    | 4-6          |

|    | 4.3.2.             | Standby Mode                                                                  |              |

|    | 4.3.3.             | Inserting NOP Instruction at Transition to Sleep and Standby Modes            | 4-8          |

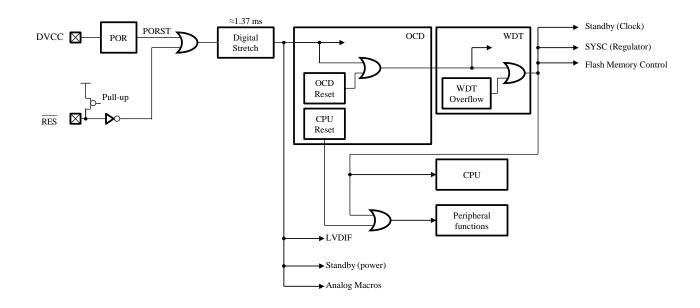

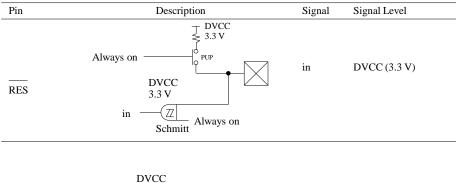

|    | 4.4. Re            | set Circuit                                                                   | 4-9          |

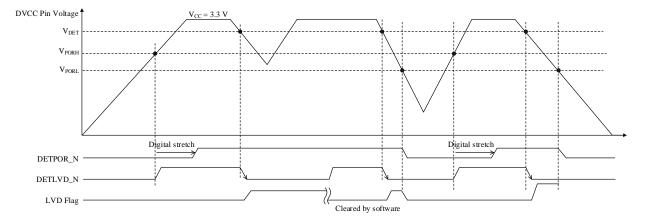

|    | 4.5. Lo            | w Voltage Detection (LVD)                                                     | 4-10         |

|    |                    | nalog Infrastructure Control                                                  |              |

|    |                    | gister Descriptions                                                           |              |

|    | 4.7.1.             | CLKCFG0 (Clock Configuration0 Register)                                       | 4-13         |

|    | 4.7.2.             | CLKCFG1 (Clock Configuration1 Register)                                       | 4-14         |

|    | 4.7.3.             | PLLCFG (PLL Configuration Register)                                           | 4-15         |

|    | 4.7.4.             | MCLKE0 (Module Clock Enable0 Register)                                        | 4-15         |

|    | 4.7.5.             | MCLKE1 (Module Clock Enable1 Register)                                        | 4-16         |

|    | 4.7.6.             | MCLKE2 (Module Clock Enable2 Register)                                        |              |

|    | 4.7.7.             | MCLKE3 (Module Clock Enable3 Register) MCLKE4 (Module Clock Enable4 Register) |              |

|    | 4.7.8.             | MCLKE5 (Module Clock Enable5 Register) MCLKE5 (Module Clock Enable5 Register) | 4-1/<br>4-10 |

|    | 4.7.9.             | MCLKE6 (Module Clock Enable6 Register) MCLKE6 (Module Clock Enable6 Register) | 4-18         |

|    | 4.7.10.            | PWMENBL (PWM Clock Enable Control Register)                                   | 4-18         |

|    | 4.7.11.<br>4.7.12. | PWMCSC0 (PWM Clock Source Control Register)                                   | 4-19<br>1 10 |

|    | 4.7.12.<br>4.7.13. | LVDCTRL (Low Voltage Detector Control Register)                               | 4-19         |

|    | 4.7.13.<br>4.7.14. | REFCTRL (Reference Control Register)                                          | 4-20<br>4-21 |

|    | 4.7.15.            | RESCTRL (Resistor Control Register)                                           | 4-21<br>4-21 |

|    | 4.7.16.            | LPCTRL (Low Power Control Register)                                           | 4-21         |

|    | 4.7.17.            | CSBYCR (CMP Standby Control Register)                                         | 4-22<br>4-23 |

|    | 4.7.18.            | DEVER (Device Version and Revision Register)                                  | 4-23         |

|    | 4.7.19.            | REMAP (Remap Control Register)                                                |              |

|    | 4.7.20.            | BUSBUFCR (BUS Buffer Control Register)                                        |              |

|    | 4.7.21.            | LINECTRL (DBG Line Control Register)                                          | 4-25         |

|    | 4.7.22.            | TMR2INCR (TMR2 Input Control Register)                                        | 4-25         |

|    | 4.8. Us            | age Notes and Restrictions                                                    | 4-26         |

|    |                    |                                                                               |              |

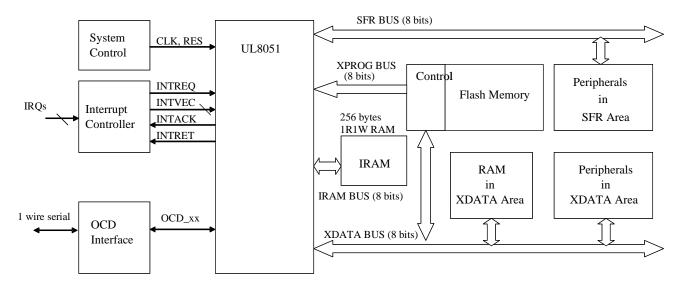

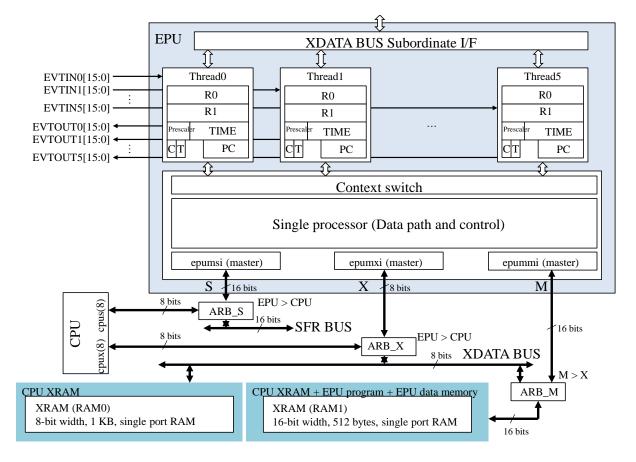

| 5. |                    | PU                                                                            |              |

|    |                    | verview                                                                       |              |

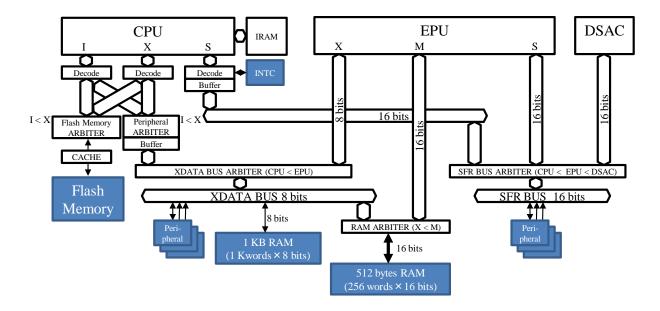

|    | 5.2. Cl            | PU Peripheral System Configurations                                           | 5-2          |

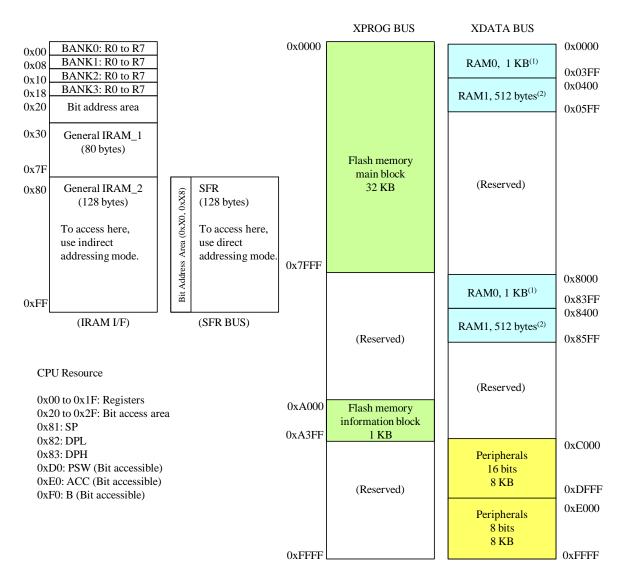

|    | 5.3. M             | emory Map                                                                     | 5-3<br>      |

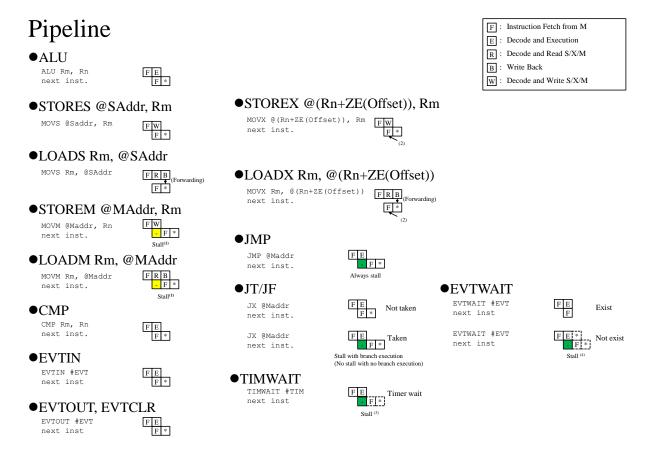

|    |                    | struction Code Map                                                            |              |

|    | 5.4.1.             | Notes on CPU Instruction                                                      |              |

|    | 5.4.2.             | Execution Cycle Counts per Instruction                                        | 5-6<br>      |

|    | 5.5. Bu            | is Configurationss Operational Descriptions                                   | 5-7<br>      |

|    |                    | ss Operational Descriptions                                                   | 5-8<br>0 =   |

|    | 5.6.1.<br>5.6.2    | Bus Master                                                                    |              |

|    | 5.6.2.<br>5.6.3    | Arbitration Circuit                                                           |              |

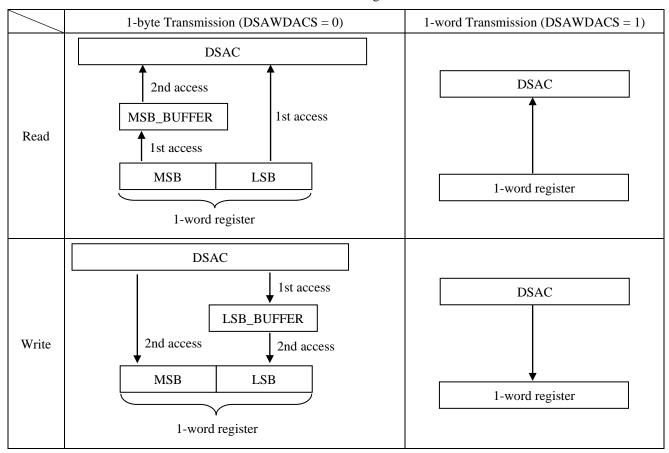

|    | 5.6.3.<br>5.6.4.   | 16-bit Access Buffer                                                          |              |

|    |                    | age Notes and Restrictions                                                    |              |

|    | J.1. US            | age more and Acsumeuris                                                       | 3-12         |

| 5.7.1.                | Restrictions on XDATA BUS Buffer                                       | 5 12         |

|-----------------------|------------------------------------------------------------------------|--------------|

| 5.7.1.<br>5.7.2.      | Conflict between 16-bit Register Write and Interrupt                   |              |

| 5.7.2.<br>5.7.3.      | Access to RAM1 Area                                                    | 5-12         |

| 5.7.4.                | Access to XDATA Space                                                  |              |

| 5.7.5.                | MOVX Instructions to Peripheral Registers of XDATA Space               | 5-12         |

| 5.7.6.                | EPU Operation While CPU Is Accessing UART Register                     | 5-12         |

| 5.7.7.                | CPU and EPU Simultaneous Access to XDATA Space                         | 5-14         |

| C Dominte             | r Mapping                                                              | 6.1          |

| 6. Registe<br>6.1. Po | eripheral Address on XDATA BUS                                         | 0-1<br>6 1   |

| 6.2. Po               | eripheral Address on SFR BUS                                           |              |

| 6.3. SI               | PRn (Scratch Pad Register n) (n = 0 to 7)                              | 6-5          |

|                       |                                                                        |              |

|                       |                                                                        |              |

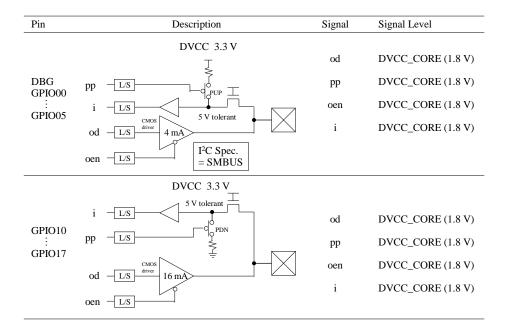

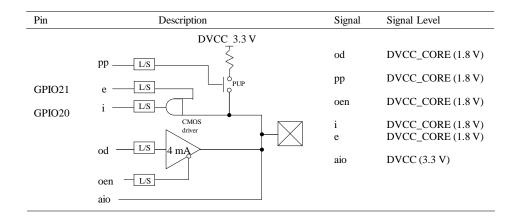

|                       | PIO Structureegister Descriptions                                      |              |

|                       | PFS0 (Pin Function Select for GPIO0)                                   |              |

| 7.2.1.<br>7.2.2.      | PFSH0 (Pin Function Select High for GPIO0)                             | 7-5          |

| 7.2.2.                | PFS1 (Pin Function Select for GPIO1)                                   |              |

| 7.2.3.                | PFSE1 (Pin Function Extend Select for GPIO1)                           |              |

| 7.2.5.                | PFS2 (Pin Function Select for GPIO2)                                   |              |

| 7.2.6.                | PFSE2 (Pin Function Extend Select for GPIO2)                           | 7-8          |

| 7.2.7.                | PDD0 (Pin Data Direction for GPIO0)                                    | 7-8          |

| 7.2.8.                | PDD1 (Pin Data Direction for GPIO1)                                    |              |

| 7.2.9.                | PDD2 (Pin Data Direction for GPIO2)                                    | 7-9          |

| 7.2.10.               | PDR0 (Pin Data for GPIO0)                                              |              |

| 7.2.11.               | PDR1 (Pin Data for GPIO1)                                              |              |

| 7.2.12.               | PDR2 (Pin Data for GPIO2)                                              | 7-12         |

| 7.2.13.               |                                                                        | 7-13         |

| 7.2.14.               |                                                                        | 7-1 <b>3</b> |

| 7.2.15.               |                                                                        |              |

| 7.2.16.               | PIEO (Pin Interrupt Enable for GPIOO)                                  |              |

| 7.2.17.               |                                                                        |              |

| 7.2.18.               | (                                                                      |              |

| 7.2.19.<br>7.2.20.    | PIFU (Pin Interrupt Flag for GPIOU)PIF1 (Pin Interrupt Flag for GPIO1) |              |

| 7.2.20.               |                                                                        |              |

| 7.2.21.               | PISO (Pin Interrupt Sense for GPIO0)                                   |              |

| 7.2.23                | PIS1 (Pin Interrupt Sense for GPIO1)                                   |              |

| 7.2.24                | PIS2 (Pin Interrupt Sense for GPIO2)                                   |              |

| 7.2.25                | · · · · · · · · · · · · · · · · · · ·                                  |              |

| 7.2.26.               | PIL1 (Pin Interrupt Level for GPIO1)                                   | 7-19         |

| 7.2.27                |                                                                        |              |

| 7.2.28.               | PIB0 (Pin Interrupt Both Edge for GPIO0)                               |              |

| 7.2.29                | PIB1 (Pin Interrupt Both Edge for GPIO1)                               | 7-20         |

| 7.2.30.               | PIB2 (Pin Interrupt Both Edge for GPIO2)                               | 7-21         |

| 7.2.31.               |                                                                        | 7-21         |

| 7.2.32.               |                                                                        | 7-22         |

| 7.2.33.               |                                                                        | 7-22<br>     |

| 7.2.34.               |                                                                        | 7-23         |

| 7.2.35                |                                                                        | 7 24         |

| 7.2.36.<br>7.2.37.    |                                                                        | /-24<br>7 24 |

| 7.2.38                |                                                                        |              |

| 7.2.39                |                                                                        |              |

| 7.2.40.               | PEMETHOD (PWM and ADC Event Gathering Method)                          | 7-26         |

| 7.2.41                |                                                                        | . 20<br>7-26 |

| 7.2.42                | SIS (Serial Input Select)                                              | 7-27         |

| 7.2.43.               | I2CIS (I <sup>2</sup> C Input Select)                                  | 7-27         |

| 7.2.44.               | TMRIS (TMR Input/Output Select)                                        | 7-28         |

| 7.2.45.               | CLKIS (Clock Input Select)                                             | 7-28         |

| 7.3. U                | sage Notes and Restrictions                                            | 7-29         |

| 7.3.1.                | Reading from PDRx Register after Writing to PDRx Register              | 7-29         |

| 7.3.2.                | Setting the Pin Functions: GPIO14, GPIO15, GPIO16, GPIO17, and GPIO21  | 7-29         |

| 8 Event               | Connection                                                             | Q_1          |

| 9. Ev                                                                                     | 4 C                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.1                          |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

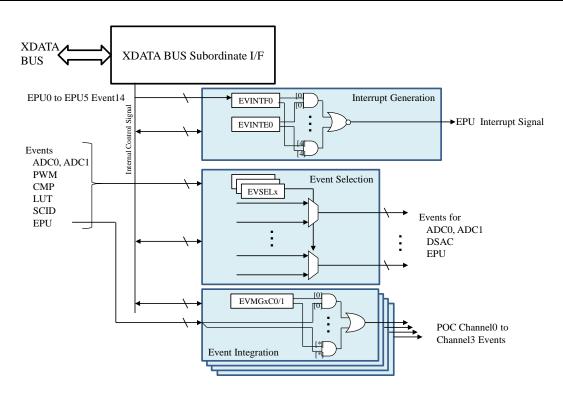

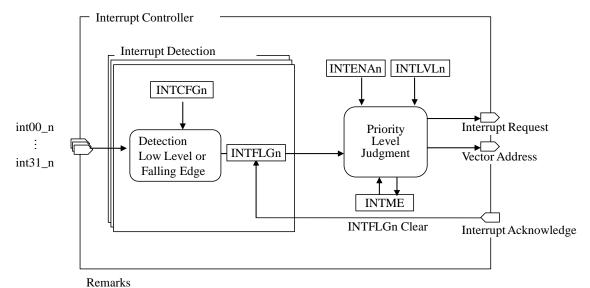

|                                                                                           |                                                                                                                           | ontroller (EVC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |

| 9.1.                                                                                      |                                                                                                                           | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |

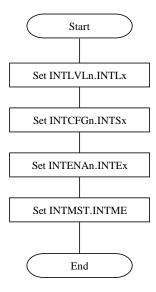

| 9.2.                                                                                      | Op                                                                                                                        | eration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-2                          |

| 9.2                                                                                       | 2.1.                                                                                                                      | Interrupt Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

| 9.2                                                                                       | 2.2.                                                                                                                      | Event Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-2                          |

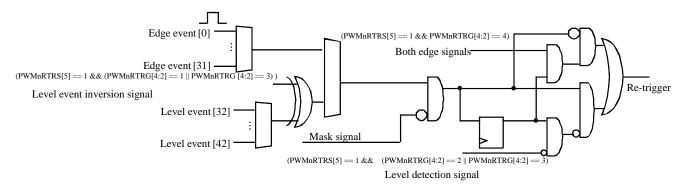

| 9.2                                                                                       | 2.3.                                                                                                                      | Event Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9-5                          |

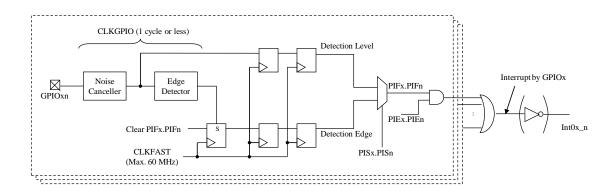

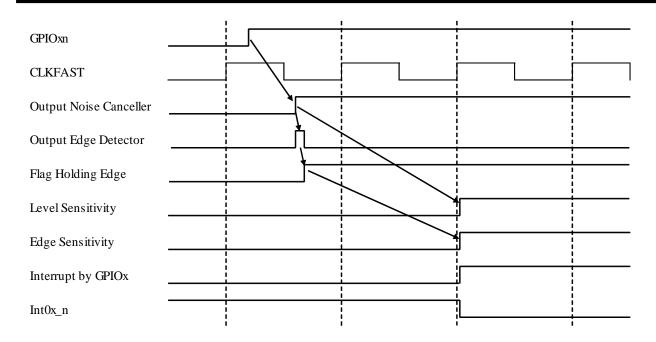

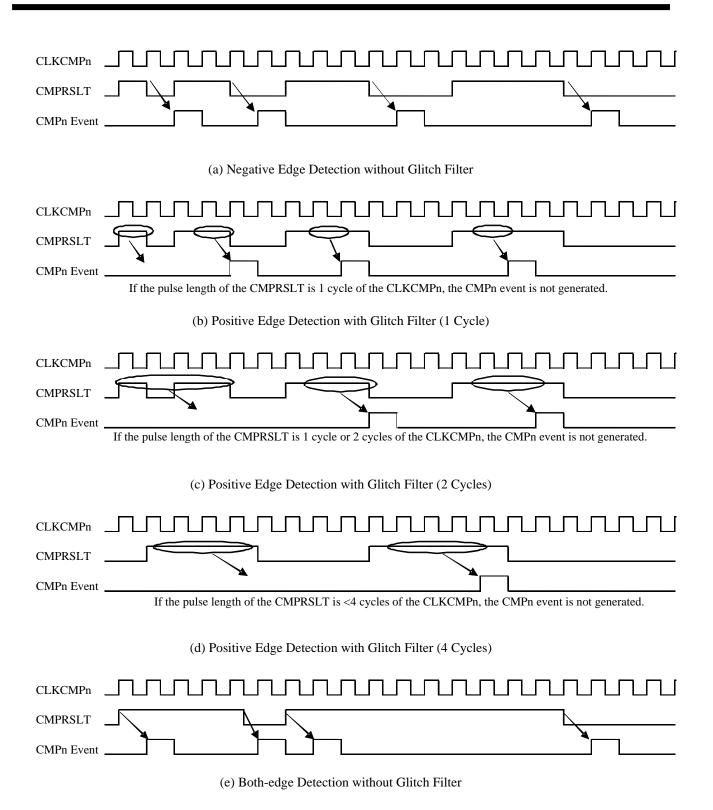

| 9.2                                                                                       | 2.4.                                                                                                                      | GPIO Event Edge Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-5                          |

| 9.3.                                                                                      |                                                                                                                           | gister Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.6                          |

|                                                                                           | 3.1.                                                                                                                      | EVINTE0 (EVC Interrupt Enable0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.7                          |

|                                                                                           |                                                                                                                           | EVINTEO (EVC Interrupt Enableo) EVINTFO (EVC Interrupt Flag0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9-7                          |

|                                                                                           | 3.2.                                                                                                                      | EVIN1F0 (EVC Interrupt Flagu)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9-8                          |

|                                                                                           | 3.3.                                                                                                                      | EVMGAC0 (EVC Event Merge A Configuration0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-10                         |

| 9.3                                                                                       | 3.4.                                                                                                                      | EVMGAC1 (EVC Event Merge A Configuration1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

| 9.3                                                                                       | 3.5.                                                                                                                      | EVMGBC0 (EVC Event Merge B Configuration0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-12                         |

| 9.3                                                                                       | 3.6.                                                                                                                      | EVMGBC1 (EVC Event Merge B Configuration1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-13                         |

| 9.3                                                                                       | 3.7.                                                                                                                      | EVMGCC0 (EVC Event Merge C Configuration0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-14                         |

|                                                                                           | 3.8.                                                                                                                      | EVMGCC1 (EVC Event Merge C Configuration1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.15                         |

|                                                                                           | 3.9.                                                                                                                      | EVMGDC0 (EVC Event Merge D Configuration0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 16                         |

|                                                                                           |                                                                                                                           | EVMGDC0 (EVC Event Merge D Configuration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.17                         |

|                                                                                           | 3.10.                                                                                                                     | EVMGDCI (EVC Event Merge D Configuration1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-17                         |

|                                                                                           | 3.11.                                                                                                                     | EVSEL0 (EVC Select0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-18                         |

| 9.3                                                                                       | 3.12.                                                                                                                     | EVSEL1 (EVC Select1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-19                         |

| 9.3                                                                                       | 3.13.                                                                                                                     | EVSEL2 (EVC Select2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

| 9.3                                                                                       | 3.14.                                                                                                                     | EVSEL3 (EVC Select3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-21                         |

| 9.3                                                                                       | 3.15.                                                                                                                     | EVSEL4 (EVC Select4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-22                         |

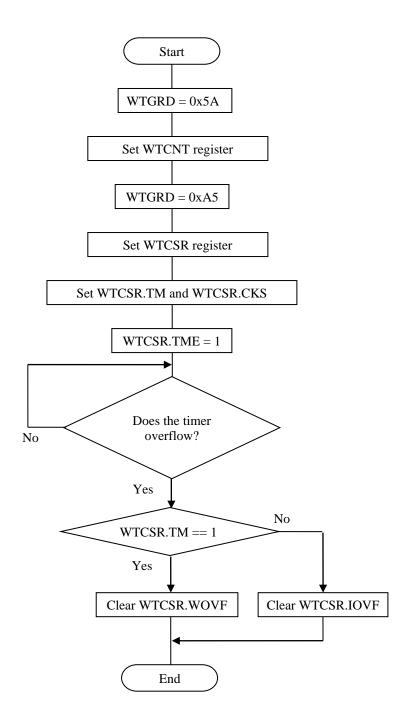

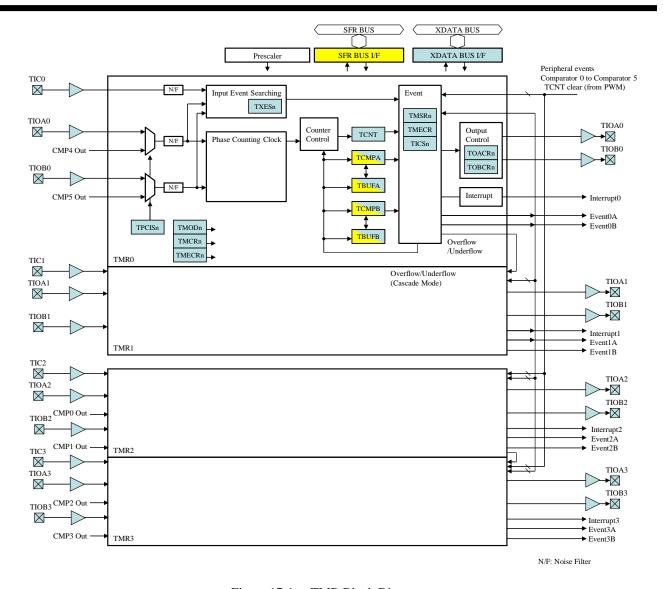

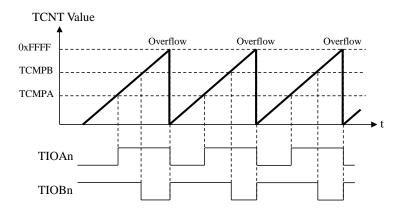

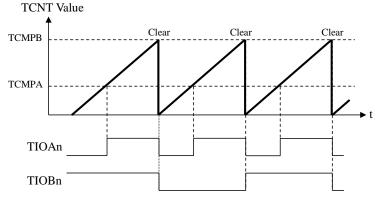

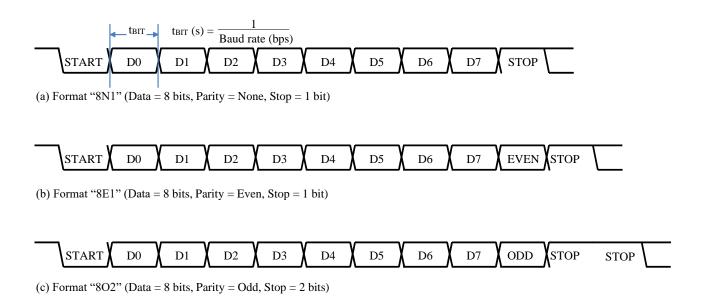

|                                                                                           | 3.16.                                                                                                                     | EVSEL5 (EVC Select5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-23                         |